1. 介紹

現場可編程門陣列(FPGA,Field-Programmable Gate Array)是當今電子領域不可或缺的一部分,具有出色的靈活性和可配置性。不過,FPGA依賴SRAM單元進行配置,因此容易受到單粒子翻轉(Single-Event Upsets,SEU)的影響。本文探討了FPGA中的SEU,強調了必須防范SEU的原因,以及快速錯誤糾正的重要性。

2. 理解單粒子翻轉

SRAM單元FPGA的核心

SRAM單元是FPGA的控制中心,存儲著控制其運行的比特流。SRAM單元狀態發生任何變化都可能導致災難性的功能故障,因此,SEU是一個十分嚴重的問題。

晶體管縮小和SEU

雖然SRAM單元通常采用較老的技術,但隨著為節省芯片面積而縮小晶體管尺寸,SRAM單元對SEU的敏感性也會增加。晶體管尺寸縮小降低了SRAM保存數據的能力,使其對各種外部因素更加敏感,特別是在航空航天應用中。

宇宙射線和地球表面

通常,宇宙射線會在地球大氣層中消散,對地表居民幾乎不構成威脅。然而,由于SRAM單元的晶體管尺寸不斷縮小,人們擔心即使宇宙射線減弱也會造成SEU,從而可能導致FPGA故障。

相關粒子

造成SEU的兩種粒子主要是中子(模擬宇宙射線)和α粒子,這兩種粒子通常由封裝中的焊球發射。雖然可以更換材料,但通常更經濟的做法是有效處理SEU。

3. 高云FPGA解決方案優勢

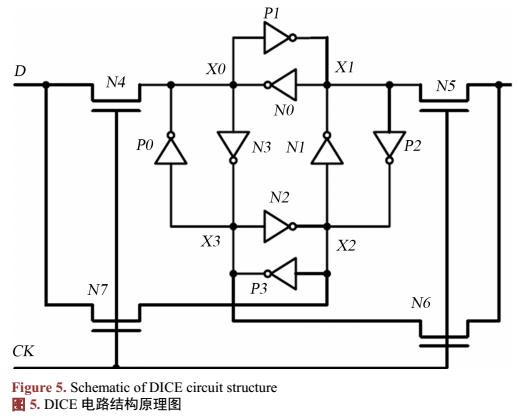

增強SRAM單元

要防止SEU,首先要增強SRAM單元。高云的創新之舉有:設計定制的SRAM單元;增強SRAM單元抗干擾性。這一舉措顯著提高了抗SEU能力,甚至在較小的芯片尺寸,如22nm的Arora V器件中也是如此。

22nm的BSRAM仍使用TSMC的晶圓廠技術,軟錯誤率(Soft Error Rate,SER)報告中存在顯著的差異。高云為用戶提供了硬件校驗和糾錯(Error Checking and Correction,ECC)電路,用于在讀取BSRAM內容時糾正BSRAM的SEU錯誤。

性能比較

高云的抗SEU能力更強,全面的測試數據彰顯了這一性能優勢。

受控測試

為了量化抗SEU能力,進行中子和α粒子轟擊的受控測試至關重要。高云的故障率數據顯示,高云FPGA的抗SEU能力非常強,超過了競爭產品和先前幾代的FPGA。以下是與高云GW2A 55nm配置SRAM單元的比較,該單元來自TSMC 55nm GP工藝。

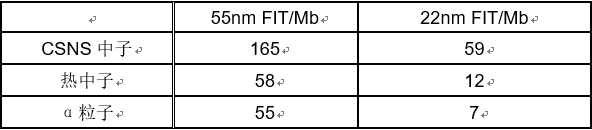

表 1 55nm TSMC 配置SRAM單元 VS 22nm高云配置SRAM單元

4. 快速錯誤糾正

錯誤糾正的重要性

對于關鍵任務的應用,錯誤糾正至關重要。高云采用基于漢明碼的錯誤糾正系統,能夠檢測和糾正數據錯誤。

比較錯誤糾正

與X公司相比,X公司只能糾正一位錯誤,而高云的GW5A器件可以糾正兩位錯誤并報告三位錯誤,提高了系統的可靠性。(138K器件是GW5A器件中唯一糾正一位錯誤的器件)X公司只能每個frame中糾正一位錯誤或者相鄰兩位錯誤(高級模式下),而高云的GW5A器件可以每個frame中糾正更多類型的兩位錯誤或者分布在frame中不同位置的更多位的錯誤,并報告不可修復的多位錯誤,提高了系統的可靠性。

高效的幀大小

高云FPGA的幀設計注重效率,與X公司的幀相比,每幀的位數要少得多。幀大小較小可降低出現多位錯誤的風險。

關于幀大小的更多信息:

138K: 幀長1513比特

25k: 幀長469比特

60k: 幀長918比特

作為對比,X公司7系列器件的幀長為3232比特。

專用Parabit

高云在SRAM幀內集成了專用Parabit,簡化了錯誤糾正過程,無需使用fabric功能來進行檢測和糾正操作。高云提供了一個簡單的封裝IP——“SEU Handler”,使用戶能輕松訪問SEU報告和糾正功能。這樣既提高了效率,也提高了可靠性。

可定制的掃描頻率

高云的FPGA解決方案提供了可定制的掃描頻率,能實現更快的錯誤檢測和糾正,這對于在關鍵的服務器環境中保持不間斷運行至關重要。在高級模式下,掃描頻率可高達200MHz。

5. 效率與整合

高云的FPGA解決方案將緩解SEU功能集成到硬件中,簡化了客戶的部署過程。這確保了運行的高效可靠。

6. 高云22nm FPGA軟錯誤率測試報告

測試背景

高云的FPGA設備是基于SRAM的,這意味著用戶邏輯是通過內部的配置SRAM單元進行編程和控制的。

業界對由α粒子或中子粒子引起的SRAM單元的SEU有充分的了解,并且在對于在計算關鍵任務、功能安全和高可靠性應用的系統故障率時需要考慮到這一點。

已測試的SRAM

SRAM單元的數量可從比特流文件中得出。

比特流文件包含需要編程到FPGA SRAM單元陣列的所有數據。

因此,根據陣列大小,可以得到SRAM單元的數量。

這種陣列包括兩類SRAM單元:一類是配置SRAM;另一類是塊SRAM,用戶在設計中將其用于存儲器存儲,不涉及邏輯控制。

表1和表2顯示了SEU所導致的軟錯誤率,該SEU會影響用作配置SRAM和塊SRAM的存儲單元。

測試方法

中子截面根據JESD89/6加速高能中子測試程序的CSNS射束測試確定,熱中子截面根據JESD89/7加速熱中子測試程序確定。

紐約市的中子軟錯誤率以FIT/Mb為單位進行了校正。

α粒子截面是根據JESD89/5加速α粒子測試程序,以镅-241源作為α輻射源測定的,α SER(FIT/MB)是根據α發射率每小時每平方厘米0.001計數校正的。

配置SRAM的SER

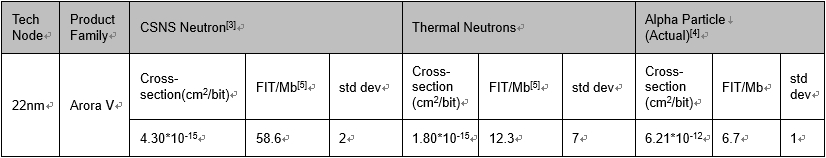

表2顯示了SEU所導致的SER,該SEU會影響用作配置SRAM的存儲單元。

表2配置SRAM的SER

Note! ? [1]實驗在帶有650Kbytes SRAM的GW5A-25產片上進行。 ? [2]實驗在常溫下進行,使用典型的電源電壓。 ? [3]數據來源于中國散裂中子源。 ? [4]典型的阿爾法數據基于0.001個每平方厘米每小時的阿爾法發射率 ? [5]中子軟錯誤率(以FIT/Mb為單位)根據JESD89A在紐約市進行了修正。.

? [6]在啟用ECC功能的測試中,所有在測試期間檢測到的SEU都進行了糾正,SER為0。

塊SRAM的SER

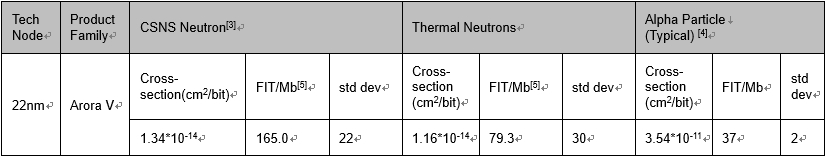

表3顯示了SEU所導致的SER,該SEU會影響用作塊SRAM的存儲單元。

表3塊SRAM的SER

Note! ? [1]實驗在帶有126Kbytes SRAM的GW5A-25產片上進行。 ? [2]實驗在常溫下進行,使用典型的電源電壓。 ? [3]數據來源于中國散裂中子源。 ? [4]典型的阿爾法數據基于0.001個每平方厘米每小時的阿爾法發射率

? [5]中子軟錯誤率(以FIT/Mb為單位)根據JESD89A在紐約市進行了修正。

配置SRAM的ECC

為驗證高云22nm FPGA的ECC功能,高云成立了一個實驗小組。

在相同的FLUX實驗條件下,SRAM的回讀頻率為15MHz,回讀和比較周期為 44610us,在回讀過程中可以觀察SEU,其中觀察到了SBU,但沒有觀察到MBU。所有觀察到的SBU都被ECC電路糾正,整個比特流保持完好,從而器件可以正常工作。

7. 結論

高云的GW5A和GW5AT系列FPGA在防止和糾正SEU方面表現出色憑借增強SRAM單元、高效糾錯和專用Parabits,高云為關鍵任務應用提供了更可靠、更高效的解決方案。

高云的FPGA解決方案使客戶即使在最具挑戰的環境中,也能滿懷信心地部署穩健的系統。

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598952 -

sram

+關注

關注

6文章

757瀏覽量

114450 -

可編程門陣列

+關注

關注

0文章

18瀏覽量

7753 -

SEU

+關注

關注

0文章

12瀏覽量

13685

原文標題:技術白皮書 | 緩解FPGA中的單粒子翻轉(SEU)——對比分析

文章出處:【微信號:gowinsemi,微信公眾號:高云半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

單粒子翻轉引起SRAM型FPGA的故障機理闡述

用SOI技術提高CMOSSRAM的抗單粒子翻轉能力

特征工藝尺寸對CMOS SRAM抗單粒子翻轉性能的影響

高速ADC的單粒子閂鎖和瞬態

如何對ADC、DAC、PLL進行單粒子翻轉容錯設計

在芯片設計階段如何防護“單粒子翻轉”

有效容忍單粒子多點翻轉的加固鎖存器

航空電子設計之“單粒子翻轉”問題

單粒子翻轉效應的FPGA模擬技術 (上)

單粒子翻轉效應的FPGA模擬技術 (下)

理解FPGA中的單粒子翻轉

理解FPGA中的單粒子翻轉

評論