11月6日消息,據(jù)彭博社報道,佳能公司正計劃將其新的基于“納米壓印”技術(shù)的芯片制造設(shè)備的價格定為ASML的EUV***的1/10。由于該設(shè)備可以用于制造5nm尖端制程芯片,且不是基于光學技術(shù),或?qū)⒊蔀橹袊@過美國限制來制造尖端制程芯片的可行方案。但是,佳能首席執(zhí)行官三井藤夫在采訪中表示,該設(shè)備無法出口到中國。

尖端制程嚴重依賴EUV***

總部位于荷蘭的ASML是目前全球最大的***廠商,同時也是全球唯一的極紫外光刻設(shè)備供應商。EUV***是目前世界上最先進的芯片制造設(shè)備,每臺成本高達數(shù)億美元。

雖然目前在***市場,還有尼康和佳能這兩大供應商,但是這兩家廠商的產(chǎn)品主要都是被用于成熟制程芯片的制造,全球市場份額僅有10%左右,ASML一家占據(jù)了90%的市場份額,并壟斷了尖端的EUV***的供應。

目前7nm以下的先進制程芯片的大規(guī)模生產(chǎn)主要都是依賴于ASML的EUV***,但只有少數(shù)現(xiàn)金充裕的公司才有能力投資購買這些EUV***。

即便如此,EUV***仍因為其在尖端芯片制造供應鏈中的關(guān)鍵地位而一直受到出口管制審查。多年前,美國就有向其盟友——荷蘭施壓,要求其限制EUV設(shè)備出口到中國。今年6月30日,荷蘭政府正式出臺了新的半導體出口管制措施,ASML被禁止向中國客戶出口EUV系統(tǒng)以及先進的浸沒式DUV系統(tǒng)。

這也意味著中國想要突破到5nm,甚至更尖端的制程工藝將會面臨極大的困難。

繞過EUV,佳能納米壓印技術(shù)可量產(chǎn)5nm

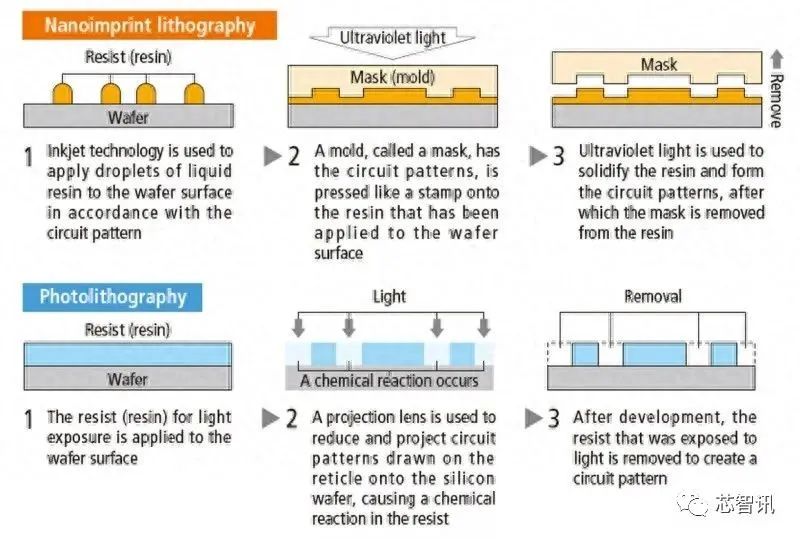

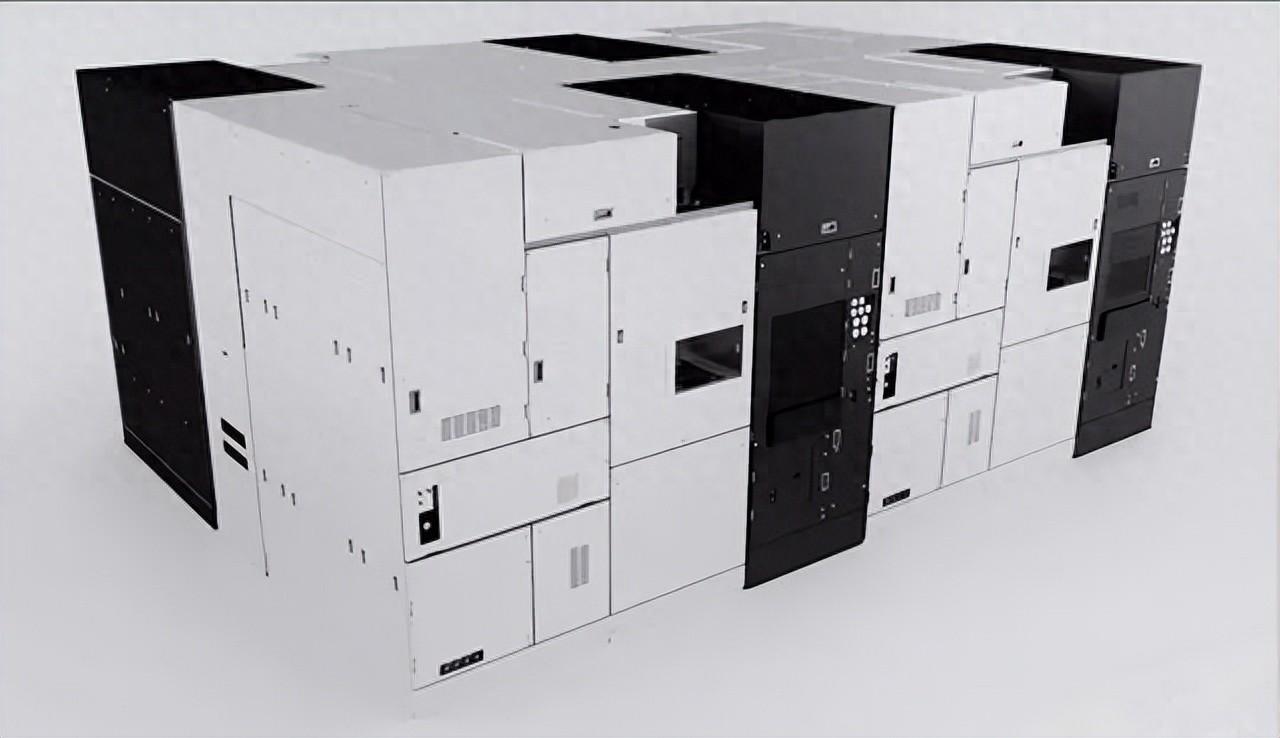

今年10月中旬,佳能公司宣布開始銷售基于“納米壓印”(Nanoprinted lithography,NIL)技術(shù)的芯片生產(chǎn)設(shè)備 FPA-1200NZ2C。佳能表示,該設(shè)備采用不同于復雜的傳統(tǒng)光刻技術(shù)的方案,可以制造5nm芯片。

此前佳能一直專注于制造不太先進***產(chǎn)品。直到2014年,佳能收購了Molecular Imprints股份有限公司,開始押注納米壓印技術(shù)

近十年來,佳能一直在與日本光罩等半導體零組件制造商大日本印刷株式會社(DNP)和存儲器芯片制造商鎧俠(Kioxia)合作研發(fā)納米壓印工藝。該技術(shù)可以不使用EUV***,就能使制程技術(shù)推進到5nm。

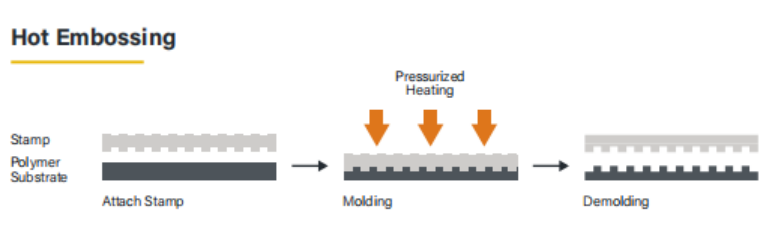

佳能表示,這套生產(chǎn)設(shè)備的工作原理和行業(yè)領(lǐng)導者 ASML 的***不同,其并不利用光學圖像投影的原理將集成電路的微觀結(jié)構(gòu)轉(zhuǎn)移到硅晶圓上,而是更類似于印刷技術(shù),直接通過壓印形成圖案。

相較于目前已商用化的EUV光刻技術(shù),盡管納米壓印技術(shù)的芯片制造速度要比傳統(tǒng)光刻方式慢,但鎧俠在2021年就曾表示,納米壓印技術(shù)可大幅減少耗能,并降低設(shè)備成本。原因在于納米壓印技術(shù)的制程較為簡單,耗電量可壓低至EUV 技術(shù)的10%,并讓設(shè)備投資降低至僅有EUV設(shè)備的40%。

佳能首席執(zhí)行官三井藤夫在最新的采訪中表示,這項新的納米壓印技術(shù)將為小型半導體制造商生產(chǎn)先進芯片開辟一條道路。“價格將比ASML的EUV***低一位數(shù)(即僅有10%)”這位88歲的老人上一次退出日常運營是在2016年,現(xiàn)在是他第三次擔任佳能公司總裁。他補充說,佳能尚未做出最終定價決定。

另外,納米壓印設(shè)備還可以使得芯片制造商降低對于ASML的EUV***的依賴,使得臺積電、三星等晶圓代工廠可以有第二個路線選擇,可以更靈活的為客戶生產(chǎn)小批量芯片。甚至,芯片設(shè)計廠商可以不依賴于晶圓代工廠來自己生產(chǎn)小批量的芯片。

因為NAND閃存的圖形更為簡單,因為其采取是多層幾乎相同的層的堆疊,所以更容易適應基于納米壓印的技術(shù)制程。鎧俠數(shù)年前就表示,已解決納米壓印的基本技術(shù)問題,正在進行量產(chǎn)技術(shù)的推進工作,希望能較其他競爭對手率先引入到NAND 生產(chǎn)當中。但隨后的消息顯示,鎧俠在對納米壓印技術(shù)進行測試之后,遭到了潛在客戶提出的投訴,認為產(chǎn)品缺陷率較高,最后并未實際應用。

另外,相對于更為復雜的,邏輯芯片來說,應用納米壓印技術(shù)的來制造還是面臨著很多的挑戰(zhàn)。不過,佳能在推動納米技術(shù)量產(chǎn)NAND的同時,也致力于將納米壓印量產(chǎn)技術(shù)廣泛的應用于制造DRAM 及PC 用的CPU 等邏輯芯片的設(shè)備上,以在未來供應多的半導體制造商,也希望能應用于手機應用處理器等最先進制程上。

據(jù)了解,佳能目前正在日本東京北部的宇都宮建造20年來第一家新的光刻設(shè)備工廠,將于2025年上線。

佳能最新發(fā)布的這套納米壓印設(shè)備可以應用于最小14平方毫米的硅晶圓,從而可以生產(chǎn)相當于5nm工藝的芯片。佳能表示會繼續(xù)改進和發(fā)展這套系統(tǒng),未來有望用于生產(chǎn) 2nm 芯片。

對于納米壓印技術(shù)市場前景,三井藤夫說:“我不認為納米壓印技術(shù)會超過EUV,但我相信這將創(chuàng)造新的機會和需求。我們已經(jīng)接到了很多客戶的咨詢。”

納米壓印設(shè)備無法出口到中國

受美國及荷蘭出臺對于先進半導體設(shè)備的出口管制影響,國內(nèi)業(yè)界對于佳能最新推出基于納米壓印技術(shù)的芯片制造設(shè)備可以繞過EUV生產(chǎn)5nm充滿了興趣,認為這可能會是一條能夠繞過美國限制制造更先進制程芯片的路徑。

雖然在今年7月日本實施了新的半導體出口管制措施,限制了可以被用于先進制程的浸沒式***的出口,其中似乎并未新增對于限制基于納米壓印技術(shù)的***的出口。

但是事實上,芯智訊查閱日本的出口管制清單,當中就有限制“可實現(xiàn)45nm以下線寬的壓印光刻裝置”。

佳能CEO三井藤夫也在最新的采訪中表示,佳能可能無法將這些(基于納米壓印技術(shù)的)芯片制造設(shè)備出口到中國。“我的理解是,任何超過14nm技術(shù)的出口都是被禁止的,所以我認為我們無法銷售。”

日本經(jīng)濟省的一名官員表示,他無法評論出口限制將如何影響特定的公司或產(chǎn)品。

-

存儲器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163604 -

光刻機

+關(guān)注

關(guān)注

31文章

1147瀏覽量

47252 -

EUV

+關(guān)注

關(guān)注

8文章

604瀏覽量

85967

原文標題:可繞過EUV量產(chǎn)5nm!佳能CEO:納米壓印設(shè)備無法賣到中國!

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

納米壓印光刻技術(shù)應用在即,能否掀起芯片制造革命?

HyperLith軟件 EUV光刻交流

臺積電產(chǎn)能爆棚:3nm與5nm工藝供不應求

AI芯片驅(qū)動臺積電Q3財報亮眼!3nm和5nm營收飆漲,毛利率高達57.8%

今日看點丨TCL收購LGD廣州廠;佳能首次出貨納米壓印光刻機

納米壓印技術(shù)的分類和優(yōu)勢

三星將為DeepX量產(chǎn)5nm AI芯片DX-M1

消息稱臺積電3nm/5nm將漲價,終端產(chǎn)品或受影響

基于納米壓印超構(gòu)透鏡陣列的增強現(xiàn)實方案

臺積電擴增3nm產(chǎn)能,部分5nm產(chǎn)能轉(zhuǎn)向該節(jié)點

佳能預計到2024年出貨納米壓印光刻機

可繞過EUV量產(chǎn)5nm!佳能CEO:納米壓印設(shè)備無法賣到中國!

可繞過EUV量產(chǎn)5nm!佳能CEO:納米壓印設(shè)備無法賣到中國!

評論