在高速設計中,如何解決信號的完整性問題?

在高速設計中,信號完整性問題是一個至關重要的考慮因素。它涉及信號在整個設計系統中的傳輸、接收和響應過程中是否能夠維持其原始形態和性能指標。信號完整性問題可能導致信號失真、時序錯誤、帶寬衰減等問題,從而影響整個系統的可靠性和性能。為了解決信號完整性問題,以下是一些必要的措施和方法。

首先,正確的信號完整性設計需要一個全面而準確的信號完整性分析。這包括對布線、噪聲、反射、環境電磁干擾等進行分析和模擬。通過使用高級仿真工具和電磁場分析軟件,可以快速評估信號完整性問題,并進行必要的優化。

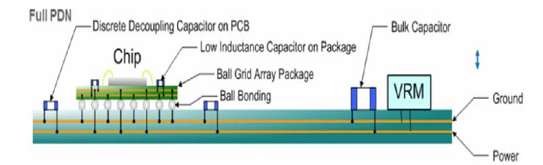

第二,布線和PCB設計是保證信號完整性的關鍵。在布線設計中,應避免信號線的過長、過細、過靠近其他干擾源等情況。信號線的長度和寬度應根據信號的頻率和速度進行優化。同時,還需要注意信號線與地線和電源線的距離,避免電磁干擾。

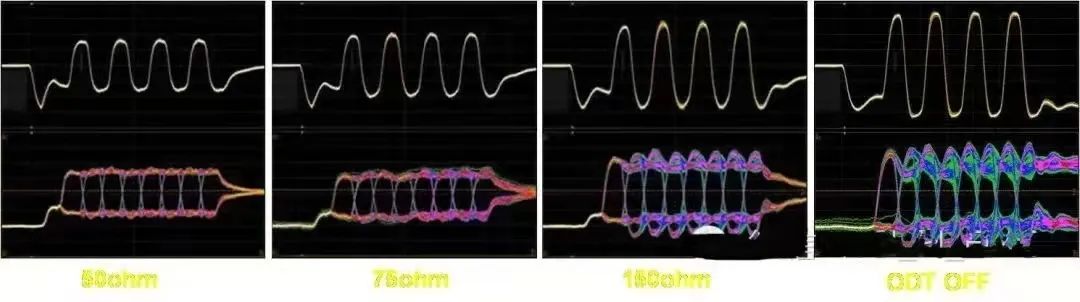

第三,選擇合適的信號傳輸線路和接口標準也是保證信號完整性的重要因素。高速信號傳輸通常需要使用特殊的傳輸線路,如微帶線、同軸線等。這些線路具有較低的傳輸損耗和較好的抗干擾性能。同時,使用合適的接口標準,如PCIe、USB、HDMI等,也能確保信號的正確傳輸。

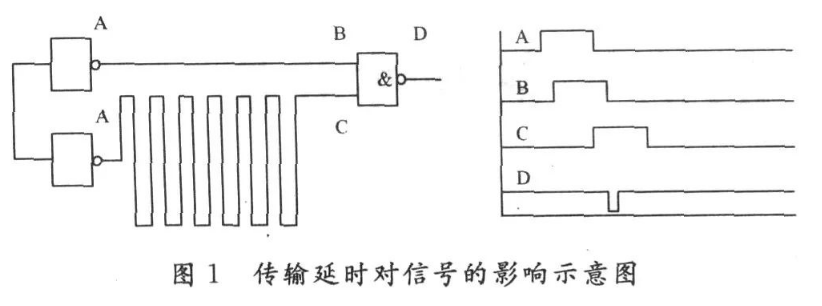

第四,信號觸發和時序控制是保證信號完整性的關鍵。在設計中,應合理設置信號的觸發時機和時序,以避免時序錯誤和不穩定性。使用合適的時鐘同步和時序控制方法,可以確保信號在傳輸過程中保持正確的順序和穩定性。

第五,電磁兼容性(EMC)是信號完整性的重要方面。EMC設計可以避免信號與其他系統成分產生電磁干擾,如電磁輻射和敏感干擾。使用合適的屏蔽措施、干擾濾波器和接地策略可以減小電磁干擾和噪聲的影響,從而保證信號的完整性。

最后,測試和驗證是確保信號完整性的最終手段。通過使用高精度的測試設備和測試方法,驗證信號的傳輸質量和時序正確性。這包括信號的電平、噪聲、波動、時延等參數的測試和分析。如有必要,還可以進行故障分析和優化。

總結起來,解決信號完整性問題需要綜合考慮設計、布線、選擇合適的線路和接口、精確的時序控制、電磁兼容性和測試驗證等多個方面的因素。只有在整個設計過程中充分考慮這些因素,并采取相應的措施,才能確保高速設計中信號的完整性,提高系統的可靠性和性能。

-

PCB設計

+關注

關注

394文章

4648瀏覽量

84531 -

信號完整性

+關注

關注

68文章

1380瀏覽量

95166 -

信號失真

+關注

關注

0文章

72瀏覽量

11308

發布評論請先 登錄

相關推薦

電源完整性問題是指什么?電源完整性分析

分析高速數字PCB設計信號完整性解決方法

使用LTspice解決信號完整性問題

PCB設計中的信號完整性問題

在高速設計中,如何解決信號的完整性問題?

在高速設計中,如何解決信號的完整性問題?

評論