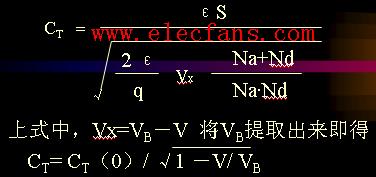

在我們現有的功率半導體器件中,PN結占據了極其重要的地位,其正向阻斷能力的優劣直接決定著功率半導體器件的可靠性及適用范圍。

當PN結兩邊摻雜濃度為固定值時,一般認為除超級結(superjunction)之外,平行平面結的擊穿電壓在所有平面結中具有最高的擊穿電壓。

在實際半導體功率器件的制造過程中,一般會在PN結的邊緣引入球面邊界和柱面邊界。該邊界位置的擊穿電壓低于平行平面結的擊穿電壓,使半導體功率器件的擊穿電壓降低。

由于PN結邊緣結構造成的曲率效應對PN結擊穿電壓有一定的負面影響,許多學者提出了一系列的結終端技術用以消除或者減弱球面結或柱面結的曲率效應。

下文對曲率效應的產生及一些新型結終端技術做簡單介紹。

1

曲率效應的產生及其對擊穿電壓的負面影響

在半導體制造過程中,當通過矩形的掩膜進行擴散形成PN結時,PN結的構成成分包括中心位置的平板形結、邊緣區的柱面結和掩膜彎角處的球面結(如圖1-1)。

柱面結或球面結都會使PN結的擊穿電壓低于平行平面結的擊穿電壓。

圖1-1 邊緣區柱面結和球面結

常見的PN結中,通過掩膜擴入的異型雜質濃度一般遠高于原有雜質濃度。在結面位置的p越小,擊穿電壓越低,當p趨近于無窮大時PN結的擊穿電壓趨近于平行平面結的擊穿電壓。

雜質在硅中的擴散為各向異性,熱過程中雜質沿各不同方向進入硅材料,一部分雜質進入到原窗口位置下方,形成橫向擴散。橫向擴散的擴散量約為縱向擴散的擴散量的85%左右,經橫向擴散形成的球面結或柱面結的曲率半徑p可用橫向擴散量r近似。

下圖1-2反映了球面結及柱面結歸一化擊穿電壓與標準化半徑n的對應關系。

圖1-2 歸一化擊穿電壓與標準化半徑η的對應關系

對于常規制造工藝,一般n的典型值只有0.1或0.1以下。球面結或柱面結對應的擊穿電壓只有理想平行平面結擊穿電壓的10%到20%左右,嚴重影響了高壓器件的可靠性。

2

結終端技術

受實際制造的高壓PN結邊界位置的球面或柱面曲率效應的影響,結的擊穿電壓顯著低于平行平面結的擊穿電壓。為改善結的擊穿特性,可采用場板、場限制環、磨角等技術降低曲率效應的影響,提高PN結擊穿電壓。

其目的為降低半導體表面電場,盡量將雪崩擊穿的可能性從半導體表面移向半導體內部,使PN結的擊穿電壓接近或達到理想平行平面結的擊穿電壓。

場板技術是改善PN結曲率效應最常用的手段之一,如圖1-3 。它是由與N+接觸的金屬延伸至N+P范圍以外構成的。

圖1-3 場板結構示意圖

當PN結反偏時,場板電位相對P型區為高電位。若場板下的絕緣介質厚度合適,高電位的作用使P型硅表面耗盡,結耗盡區擴展至場板以下區域,表面靠近N+P結位置原有的高電場被分散,并在場板的邊緣出現一個新的電場峰值。

最優化的設計要求場板邊緣的電場峰值等于N+P結位置的電場峰值,可通過求場板下解絕緣介質中的Laplace方程和P型硅中的Possion方程計算出最佳場板長度。

當場板電位為獨立的固定電位時,已有的報道表明NP結的擊穿電壓與場板電壓成線性關系。

實際的制造過程中一般不方便為場板提供特定的固定偏置,場板常常與N+區域直接連接并電位相等。

計算表明,在場板下方的絕緣SiO2介質厚度小于0.7um和P型襯底濃度低于107cm^3^時雪崩擊穿發生于場板邊緣。為避免這一現象,場板結構衍生出斜坡場板、階梯場板、電阻場板等新結構。

特別值得一提的是電阻場板(SIPOS)(圖1-4),該結構最早由Matsushita等人提出。半絕緣的SIPOS層導電能力極其微弱,使得其中的電流水平甚至接近PN結的反向漏電流。

圖1-4 電阻場板結構

SIPOS中的電場分布取決于其本身的電阻分壓關系,與半導體耗盡區中電場無關,因此在設計中可根據需要調整SIPOS中的電場分布。SIPOS中的恒定電場迫使與之接近的半導體表面耗盡區中電場與之一致,從而基本上避免PN結的表面擊穿。

理想的電阻場板可以讓PN結的擊穿電壓與平行平面結的擊穿電壓相等,實際制造的電阻場板由于離子沾污等問題常出現漏電流過大等問題。

3

場限制環技術

場限制環技術最早由Kao,Y.C等提出,如圖1-5所示。

圖1-5 場限環結構示意圖

場限制環由擴散區構成,它具有與反偏的PN結高摻雜區相同的摻雜類型,但處于電位浮空的狀態。在制造中場限制環一般也與PN結高摻雜區采用同一道工序制造完成。

優化設計的場限制環與主結之間的距離應保證環與主結的耗盡區在發生雪崩擊穿以前能夠匯合,當PN結反偏電壓進一步增加時兩個空間電荷區便完全合并,這將限制曲面附近電場的進一步增長并使其不能達到PN結的臨界擊穿電場。

場限制環在一定程度上分擔了主結上的壓降,有效降低了主結邊緣位置的曲率效應。

Adler等人對場限制環電場強度進行了計算。

多維分析表明:環實際所分擔的主結電壓要比一維分析的結果偏小,采用場限制環后擊穿一般不在表面發生,而是發生在曲率最大的點上。

分析結果還表明主結與環之間的距離對環的分壓程度有明顯影響,而且存在一個場限制環可起作用的最大距離。

此外,場限制環對PN結的作用要比對NP結的作用要好,這是由于半導體表面有形成N型寄生漏電溝道的趨勢,使用場限制環的N'P結漏電流較大。

以單環結構為基礎又衍生出多環結構,如圖1-5(b)所示。多環結構可以通過改變掩膜窗口圖形的方式實現,并不增加額外的工序。適當設計的多環結構可使PN結的擊穿電壓接近平行平面結的擊穿電壓,但多環將占用芯片更多的面積,這在一定程度上限制了環的數量。

-

PN結

+關注

關注

8文章

480瀏覽量

48647 -

擊穿電壓

+關注

關注

1文章

57瀏覽量

8986 -

功率半導體

+關注

關注

22文章

1131瀏覽量

42885 -

漏電流

+關注

關注

0文章

260瀏覽量

16995

發布評論請先 登錄

相關推薦

PN結曲率效應的產生及其對擊穿電壓的影響

PN結曲率效應的產生及其對擊穿電壓的影響

評論