DRAM制造技術進入10nm世代(不到20nm世代)已經過去五年了。過去五年,DRAM技術和產品格局發生了巨大變化。因此,本文總結和更新了DRAM的產品、發展和技術趨勢。

DRAM 并不是小型化背后的驅動力

在半導體制造技術的發展中,DRAM在2000年之前一直是小型化的推動力。他們也被稱為“流程驅動者”。然而,到了2000年代,情況開始發生變化。NAND閃存(當時的平面存儲器)積極推動了制造技術的小型化。微細加工的主導地位將被NAND閃存取代。

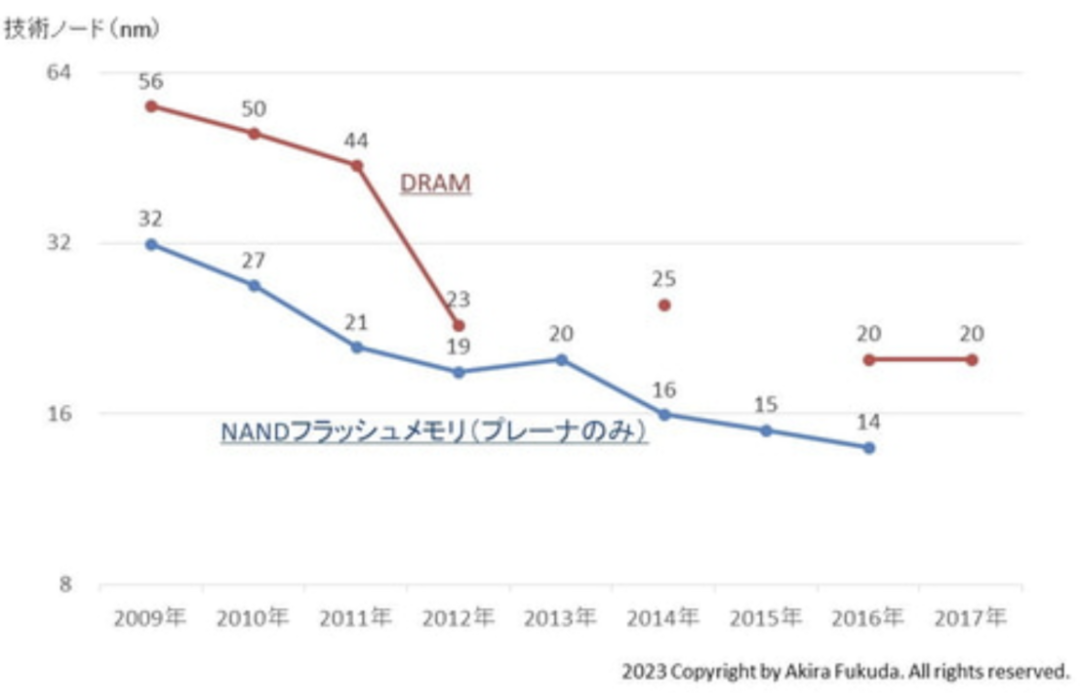

最新的開發成果(原型芯片)在ISSCC(每年二月在美國舊金山舉行)上展示,ISSCC是半導體研發界最知名的電路技術國際會議。2009年至2011年,DRAM的技術節點(最小加工尺寸)為56nm至44nm,而NAND閃存(平面型)約為其一半,為32nm至21nm。

DRAM 和 NAND 閃存的技術節點(僅限平面)。

一直處于小型化前沿的NAND閃存在2015年左右達到極限,之后放棄了加工尺寸的小型化,轉而采用三維層壓。NAND閃存的小型化幾乎已經停止,從2010年代后半段開始,DRAM將再次推動小型化。

在半導體邏輯中,“技術節點名稱”與物理尺寸不同

然而,在2000年之前,DRAM正在推動整個半導體(半導體存儲器和半導體邏輯)的小型化,而在2010年代末到2020年代初,DRAM推動半導體邏輯小型化的進程變得緩慢。主要有兩個原因。

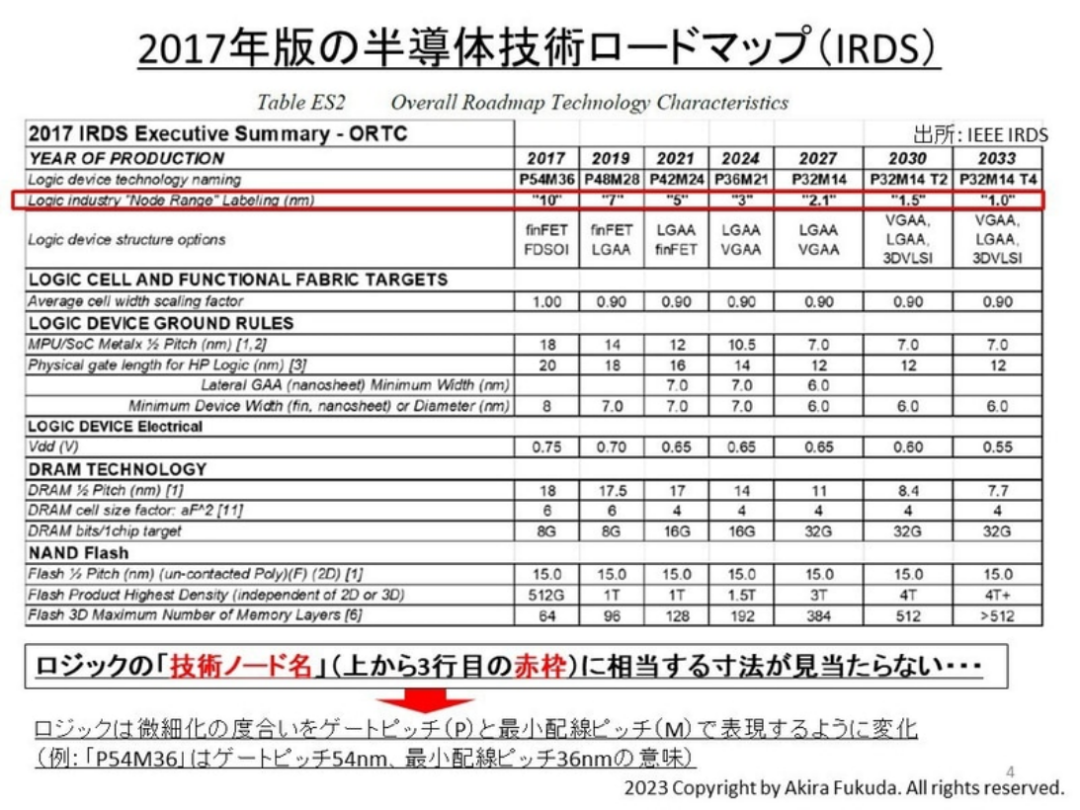

第一個是半導體邏輯中晶體管的三維化。隨著MOSFET從平面結構轉變為三維FinFET,曾經作為小型化指標的柵極長度(或溝道長度)不再具有任何定義意義。相反,小型化程度主要由標準單元(邏輯單元的最小單位)的柵極節距和最小布線節距決定(嚴格來說是兩者的乘積)。“7nm”、“5nm”等數值,作為尖端邏輯的“技術節點名稱”只是一個標簽,在硅芯片中并不存在。

半導體技術路線圖 (IRDS) 2017 版。從上方預測邏輯、DRAM 和 NAND 閃存的壽命和尺寸。可以看到,找不到半導體邏輯技術節點名稱(紅框)對應的維度。

另一個問題是半導體邏輯和DRAM的器件和工藝技術已經變得截然不同。每一代半導體邏輯制造工藝都逐漸改變了晶體管的基本技術,有時甚至是顯著改變。其中包括應變硅、HKMG(高介電常數金屬柵極)、FinFET 和 COAG(有源柵極上的接觸)。對于多層布線,銅(Cu)布線和低介電常數層間絕緣膜的開發和全面采用。

DRAM“技術節點名稱”反映實際物理尺寸

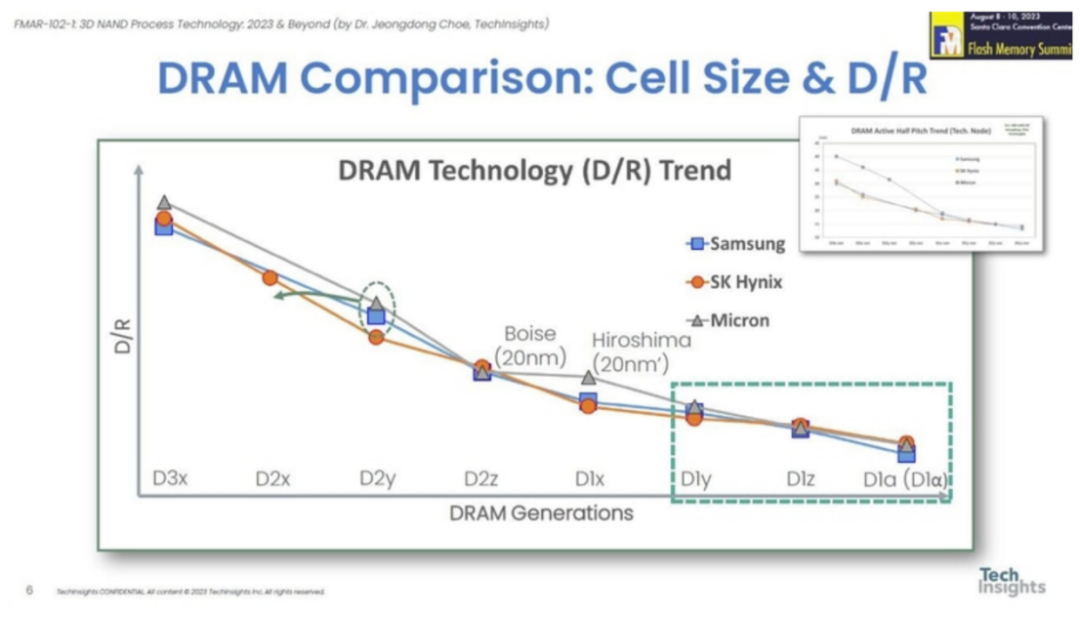

DRAM的“技術負載名稱”與邏輯不同,但更接近其實際尺寸。DRAM技術節點名稱通常使用符號而不是具體數字來表示。技術節點用符號表示,例如 30nm 代的“D3z”和 20nm 代的“D2x”。

D2x估計在28nm左右,D2y估計在25nm左右,D2z估計在22nm左右。雖然各DRAM廠商技術節點符號對應的數值略有差異,但并無大的差異。

主要 DRAM 技術節點名稱與設計規則 (D/R) 之間的關系。可以看出,主要DRAM制造商的

技術節點名稱與實際設計規則之間幾乎沒有差異。來源:TechInsights

技術節點名稱對應的維度存在于存儲單元陣列的有源區域(單元選擇晶體管區域)。有源區域規則排列,排列的一半間距代表技術節點名稱。換句話說,在 D1x 代(也稱為 18nm 代或 1Xnm 代)DRAM 硅芯片中,單元晶體管以約 36nm 的間距布置。

根據半導體芯片分析服務公司TechInsights發布的預估,2018年12月,三大DRAM公司的D1x代(1Xnm代,半間距)最小尺寸分別為三星電子18nm、SK海力士17.5nm、美光為17.5nm,技術為19nm。幾乎沒有區別。

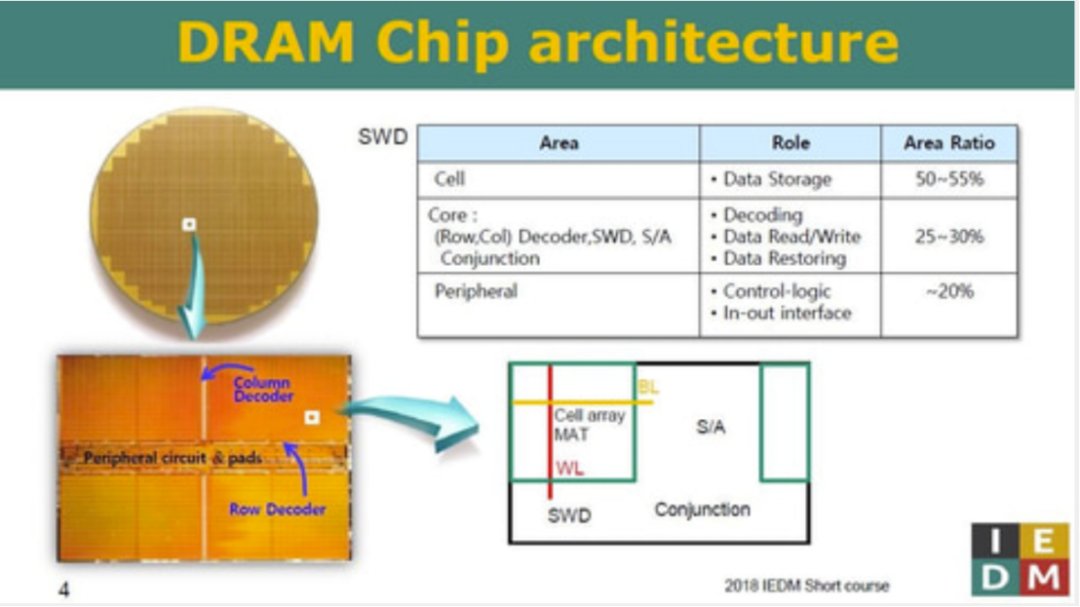

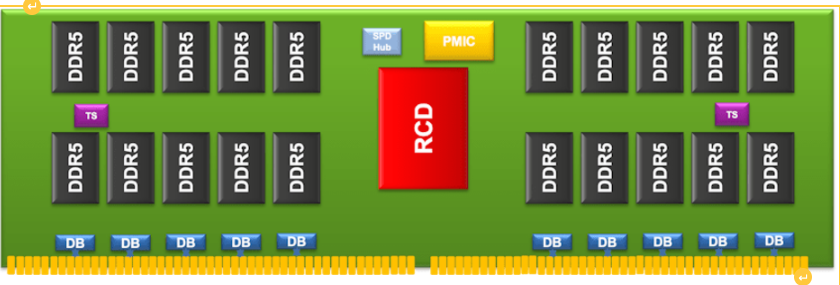

DRAM芯片的基本架構

在DRAM制造過程中,許多DRAM芯片被制造在硅晶圓上。從硅晶圓上切下來的單個DRAM芯片被分為存儲單元陣列(通常由偶數個子陣列組成)和外圍電路(外圍)區域。

存儲單元陣列,即DRAM的存儲區域,邏輯上形狀像一個二維矩陣。由多行和多列組成的矩陣的交集(方格)是一個存儲單元,行號和列號是指定存儲單元(棋盤的方格)的地址。

這里,行號被稱為“行地址”并且列號被稱為“列地址”。存儲單元陣列區域分為“存儲單元”和“核心”。存儲單元是存儲信號的區域,由1個晶體管(MOS FET)和1個電容器(單元電容器)組成。核心是從存儲單元陣列中選擇目標存儲單元并讀取或寫入數據的電路。“字線解碼器”選擇單元晶體管的柵極(字線),“位線解碼器”選擇源極(位線),以及放大用于讀取和讀取的信號的“讀出放大器(S/A)”。寫入數據、各部分的互連(布線)等。

外圍電路(peripheral)由控制電路和輸入輸出電路組成。控制電路根據從外部輸入的命令和地址來操作DRAM內部的電路。輸入/輸出電路負責輸入(寫入)和輸出(讀取)數據。

解釋 DRAM 基本架構的圖。來源:三星

左上是硅片照片(實際直徑估計為300毫米)。左下角是 DRAM 硅芯片的照片。外圍電路、輸入/輸出焊盤和行解碼器位于硅芯片中心的左側和右側,列解碼器位于中心的上方和下方,存儲單元陣列(“子陣列”)位于硅芯片的硅芯片中心的上方和下方。剩余的頂部、底部、左側和右側(方形部分)。)被布置。該圖的右下角表示存儲單元陣列(子陣列)的基本結構。將一個存儲單元放置在紅色字線 (WL) 和黃色位線 (BL) 的交叉點處。字線的末端連接到子字線驅動器(SWD),并且位線的末端連接到讀出放大器(S/A)。該圖的右上方顯示了每個部分與硅芯片面積的比率。存儲單元占50%-55%,核心(解碼器、驅動器、讀出放大器、互連)占25%-30%,外圍設備(控制電路和輸入/輸出電路)占20%左右。

通過在電容器中存儲電荷來存儲邏輯值

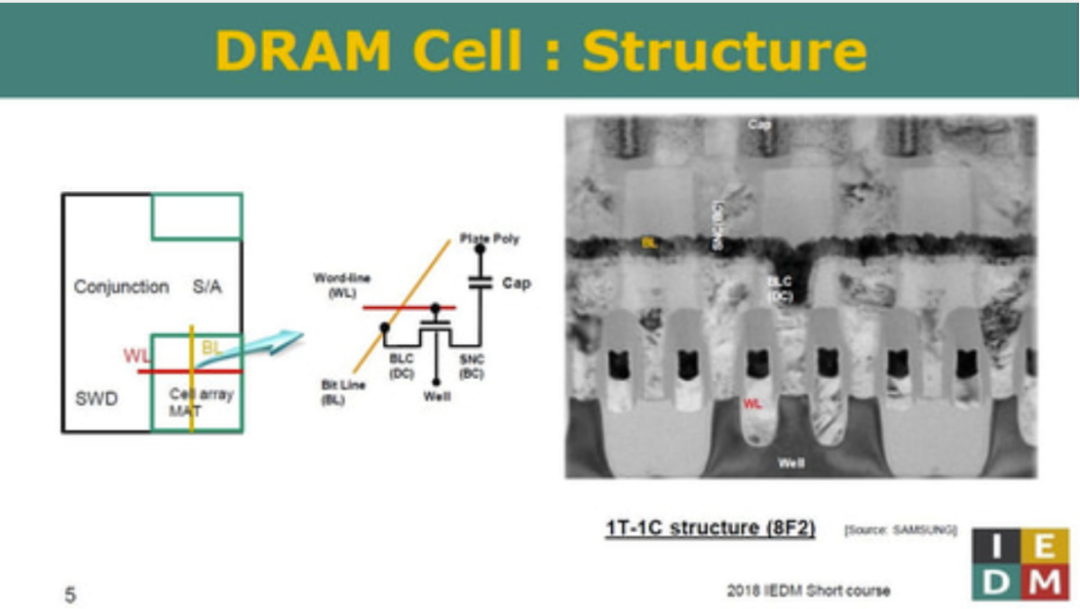

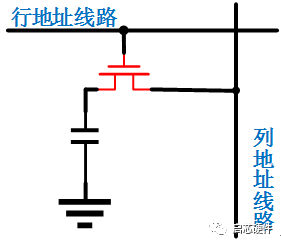

一個 DRAM 存儲單元由一個晶體管(縮寫為“T”)和一個電容器(縮寫為“C”)組成。它在半導體存儲器技術界通常被稱為“1T1C 單元”。晶體管充當選擇開關。也稱為“選擇晶體管”。在讀或寫操作中,位于由字線譯碼器和位線譯碼器選擇的字線和位線交叉處的“選擇晶體管”被導通。

存儲單元電容器(功能與電子元件的電容器相同)存儲信號電荷。也稱為“單元電容器”。如果電容器存儲一定量的電荷,則存儲單元的邏輯值為“高”(或1)。相反,如果僅存儲少于一定量的電荷,則存儲單元的邏輯值將為“低(或0)”。

DRAM 存儲單元電路的示例(左)和使用電子顯微鏡觀察到的存儲單元的截面圖像(右)。

在左邊的電路圖中,選擇晶體管(通常是n溝道MOSFET)的柵極是字線(紅色:WL),源極是位線(黃色:WL)。選擇晶體管的漏極通過單元電容器連接到板電極。在右側的截面觀察圖中,紅色標記為“WL”的部分是選擇晶體管(字線)的柵極,BLC是位線觸點,SNC是存儲節點觸點。SNC 上方連接有一個電容器(圖中的“Cap”)。SNC 字母左側的黃色字母“BL”表示位線。

DRAM存儲單元的基本操作和刷新

當向 DRAM 寫入數據時,解碼器打開指定地址處的選擇晶體管,輸入緩沖器接收外部數據,然后通過讀出放大器將其轉換為電流,對單元電容器進行充電。

充電后,隨著時間的推移,由于電容器放電,寫入的數據(電荷)會丟失。因此,有必要定期重寫數據。該操作稱為“刷新”。2000 年之前,DRAM 由外部內存控制器在適當的時間刷新。最近,很多產品內部都實現了自動刷新操作。

讀取數據時,選擇晶體管導通,單元電容器中的電荷作為電流通過位線。位線電流被讀出放大器(S/A)放大為電壓。電壓信號通過輸出緩沖器發送到外部。

在讀取操作期間要記住的一件事是,單元電容器上的電荷會因讀取操作而丟失。因此,讀出放大器立即恢復(新寫入)讀取的數據。

2000年代,DRAM存儲容量擴張步伐迅速放緩。

2000年之前,DRAM存儲容量迅速擴張,尤其是在20世紀70年代和80年代。半導體存儲器行業稱之為“三年翻兩番”,三年內將存儲容量提高四倍的下一代DRAM商業化已成為半標準做法。盡管主流用戶已經從大型機(1970年代)到工作站(1980年代)再到個人電腦(PC)(1990年代),但情況依然如故:他們期望DRAM制造商在三年內將開發速度翻兩番。

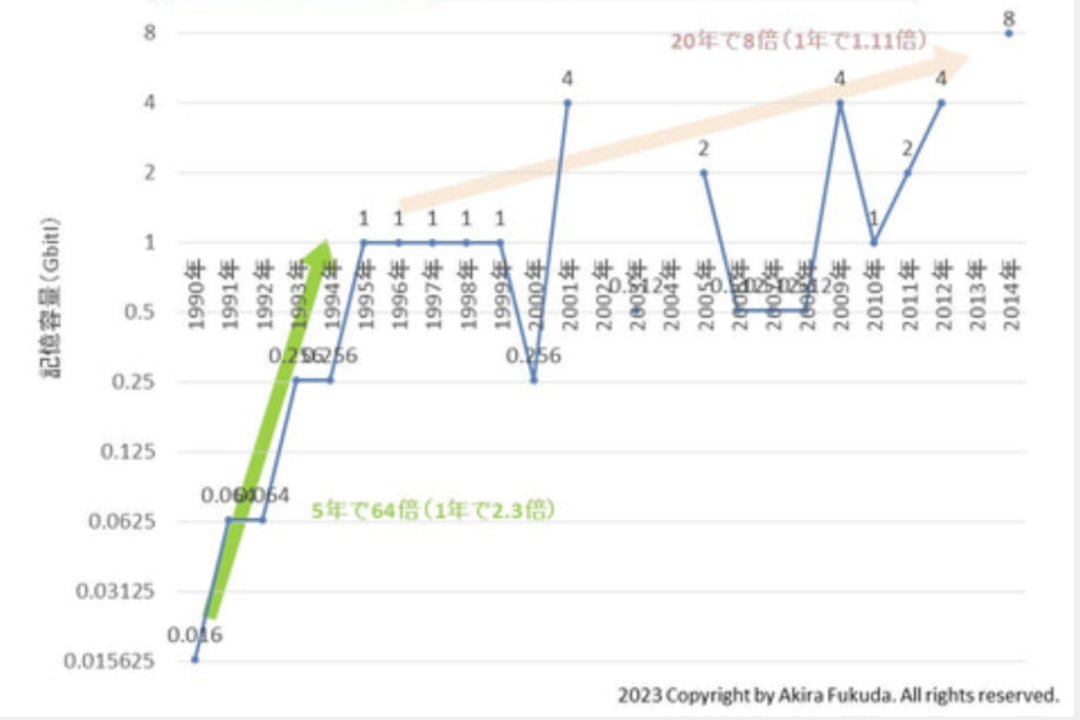

這里我們將從國際會議 ISSCC(每年 2 月舉行)上介紹的硅芯片概述開始,了解 DRAM 的發展狀況。首先是最大存儲容量。20世紀90年代前半期,產能增長速度遠遠超過“3年4倍(1年1.59倍)”。它從1990年的16Mbit迅速擴展到1995年的1Gbit。“5年64次(1年2.3次)”是一個令人難以置信的快節奏。

然而,1995年后,存儲容量擴張的步伐突然放緩。直到 1999 年,最大容量仍保持在 1Gbit。之后在256Mbit、512Mbit、1Gbit、2Gbit、4Gbit之間來回切換。向下一代 4Gbit 的過渡是緩慢的。隨著2014年和2016年8Gbit硅芯片的發布,我們現在可以清楚地說,容量的增加比1Gbit一代已經進步了約1.5代。事實上,產能繼續以 DRAM 發展史上從未見過的速度擴張,20 年內增長了 8 倍(1 年內增長了 1.11 倍)。

DRAM 最大存儲容量(每個硅芯片)的變化(1990-2014 年)。可以看出,從1996年到2012年,增產并沒有太大進展(每年擴張1.11倍)。

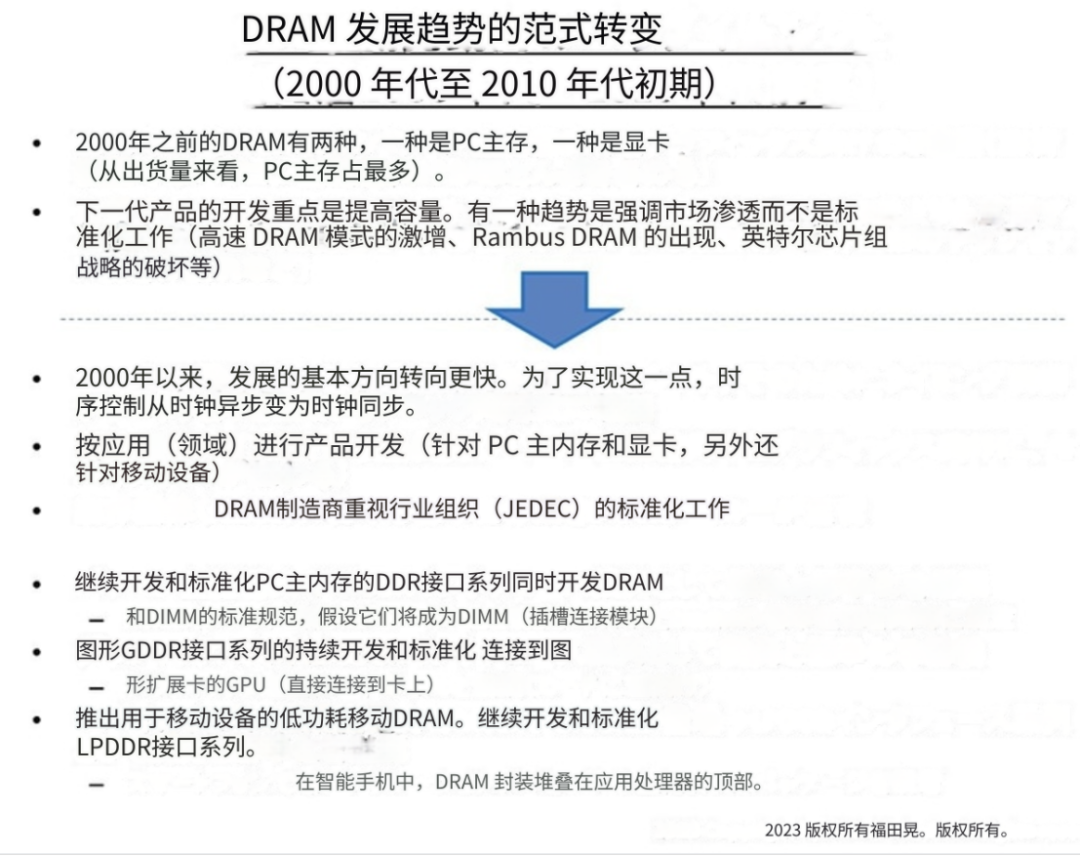

DRAM開發的范式轉變

從20世紀90年代末到2010年代初的20年間,DRAM的發展發生了什么?總的來說,可以說開發方向發生了很大變化。DRAM開發的方向從大容量,走向高速化。

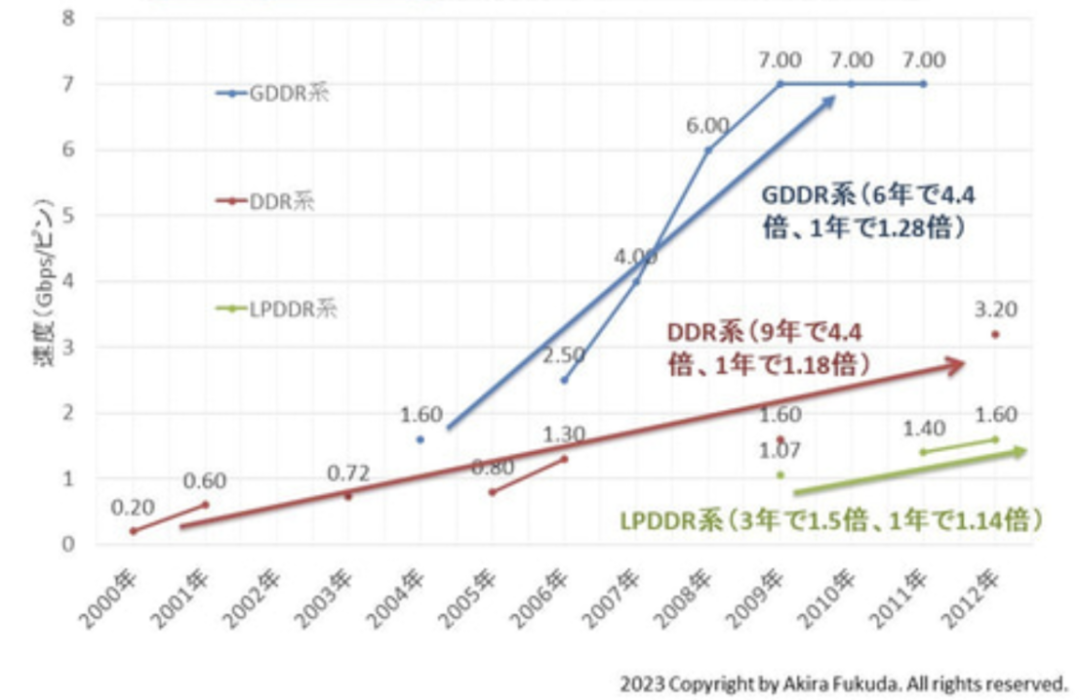

DRAM數據傳輸速度的推移。

為了高速化,在動作定時控制中采用時鐘同步式。最初,為了與傳統的DRAM(無時鐘異步式DRAM)區別,被稱為同步DRAM(SDRAM)。現在,如果簡單地記述DRAM,則意味著同步式(或者不知道是同步式還是異步式)。嚴格來說,DDR、LPDDR、GDDR等DRAM的表述為“SDRAM”是正確的,在產品目錄和學會論文等中也有“SDRAM”的表述。

SDRAM的下一代標準規格是出于高速化的強烈意識而制定的。最初的SDRAM以與時鐘相同的速度輸入輸出數據。此時的時鐘頻率為133MHz.SDRAM的下一代產品成為能夠以時鐘速度的2倍輸入輸出數據的規格。這就是所謂的“雙數據速率(DDR)SDRAM”。時鐘頻率提高到200MHz,數據的輸入輸出速度是時鐘的2倍,即400MT/s/輸入輸出引腳(這里T(transfer)是傳輸次數的意思)。一次傳輸中發送接收1比特等于bit/秒)。

DDR系列的SDRAM之后,每代數據的輸入輸出速度都會提高一倍。在國際學會ISSCC上發表的DDR類SDRAM的數據傳輸速度在2003年至2012年的9年間提高了4.4倍。

圖形DRAM也采用DDR,積極推進高速化。這就是“GDDR(圖形DDR)SGRAM(同步圖形RAM)”。GDDR類SGRAM的高速化正在迅速推進。在國際學會ISSCC上發表的GDDR系SGRAM的數據傳輸速度在2004年至2010年的6年間增加了4.4倍。年增長率為1.28倍。

隨著移動電話終端和智能手機等的普及,開發了低功耗版SDRAM。最初被稱為“移動DRAM”,但后來以“LP(Low Power)DDR SDRAM”的名稱進行開發和標準化。2009年,國際學會ISSCC首次公開了LPDDR系的試制硅芯片。由海力士半導體(Hynix Semiconductor)開發的1Gbit芯片,數據傳輸速度為1.066Gbps/pin。到2012年,LPDDR系統的數據傳輸速度提高了1.5倍(年速率為1.14倍)。

DRAM開發動向的范式轉變。

通過引入時鐘同步式設計來實現高速化、不同用途的產品開發,以及考慮不同領域的安裝形態(封裝和模塊)的標準規格的制定等是2000年代以后的DRAM開發策略。大容量化的主要部分將由NAND閃存承擔。2005年,根據ISSCC,NAND閃存的存儲密度超過了DRAM的存儲密度。可以說,這是“大容量為NAND閃存,高速為DRAM”的角色分擔越來越強的時代。

-

芯片

+關注

關注

450文章

49636瀏覽量

417188 -

DRAM

+關注

關注

40文章

2282瀏覽量

182972 -

半導體制造

+關注

關注

8文章

378瀏覽量

23982

原文標題:DRAM的范式轉變歷程

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DRAM存儲器的基本單元

DRAM的分類、特點及技術指標

NAND閃存的發展歷程

DRAM內存操作與時序解析

DRAM在計算機中的應用

DRAM合約價一季度漲幅預計13~18%,移動設備DRAM引領市場

dram和nand的區別

DRAM選擇為何突然變得更加復雜?

ADI電源管理芯片使用歷程及心得

芯片設計中DRAM類型如何選擇

DRAM的工作原理 DRAM存儲數據和讀取數據過程說明

DRAM的范式轉變歷程

DRAM的范式轉變歷程

評論