一、FAB工藝流程入門

?1.這里的FAB指的是從事晶圓制造的工廠。半導體和泛半導體通常使用"FAB"這個詞,它和其他電子制造的“工廠”同義。在平時溝通的語境中,FAB還可以被指代為“車間”,比如:在FAB工作的工程師上班時說:我進FAB了,其實指的是我進車間了。業界對于多個FAB,通常使用FAB1、FAB2…這樣的編號來擴展。?2. FAB的車間是潔凈室,進去要穿無塵服和專門的無塵鞋(配套的還有一次性網帽、口罩、手套),因此每個潔凈室外面都會配套一個衣帽間,衣帽間和車間中間有風淋門隔擋,進去車間要測靜電和過防護門吹掉身上的灰塵才可以進入。

上次去產線是真的。

?3. 車間里面都是各種設備,每臺設備會貼有設備ID,用以唯一識別它是它自己。總體上面可以分為兩種:?一種是加工類:就是對晶圓進行增材、減材、改性的設備;?另一種是檢查類:包括檢查缺陷、量測參數和測試電性。?檢查其實可再細分為檢測、量測和目檢三種,?檢測主要是針對缺陷進行掃描,比如顆粒、圖形缺陷這些;?量測主要是量出參數值,比如:膜厚、應力、電阻值、套準偏差這些;用顯微鏡和人眼看通常歸到目檢。?4.加工設備和檢查設備配套組合在一起為工藝加工服務。工藝是車間內資源的有序組織形式,晶圓制造是一個循環加工的過程。主要是把立體的電路圖形在襯底上給制造出來,因為是立體的所以就會有層(Layer)的概念,但是每一層的工藝是差不多。這些差不多的工藝,通常被概括為四大模組:薄膜、光刻、刻蝕、注入(擴散),每次工藝過后通常都會搭配量測或者檢測工序,用以確定工藝的結果,比如,薄膜后就會要量一下膜厚,光刻和刻蝕后會要量一下線寬,擴散后會量一下片阻值之類,有些關鍵層還會要掃缺陷。全部做完,要測電性。

二、四大模組

模組是分工的產物,旨在讓人能夠聚焦于特定的一些工藝而不是全部工藝,達到熟能生巧,以確保工廠的穩定。

模組,其實就是把類似和相關的工序組成一個集合的概念,這樣就可以分配給相對的部門去負責,他們只做這一部分對應的工作。比如:刻蝕工藝工程師就專門做刻蝕這一部分工作,不要做薄膜的工作。

模組是一個基于工廠管理的概念,而不是一個嚴謹的科學分類,因此四大模組顯然是不能夠概括所有工序,只能大體上用于了解制造的過程。要對晶圓制造過程有一個相對結構化的理解還得去分析這個產品本身。

在電子世界里,二進制是萬物的基礎,通過1和0可以表征復雜的控制和運算邏輯,而二進制與物理世界的對應關系就是“開”和“關”,一臺計算機就可以理解成是由一系列開關組成的電路的集合。

一按開機鍵,就改變了電流,它被芯片翻譯為0和1的的指令到存儲器進行轉換(通過門電路),然后輸入到CPU的控制單元進行轉換,再輸入到CPU的運算單元(一堆門電路組成的電路,實現讀取指令,分析指令,讀取指令值(如開機) ,執行指令),算完之后,輸出給外設(輸出指令結果),比如顯示器,顯示器里面的每個晶粒通電,于是屏幕亮起。

其他的各種指示燈同理,依次亮起。這就是為什么計算機啟動的起點一定是要開機,通過外部給予一個觸發的原因。同樣,很多軟件的運行,也一樣至少需要一個外界給予觸發,觸發之后就可以通過事先組合好的“0和1指令”(開關)去自運作。

這些開關顯然不是一個一個裝上去,而是一個模塊一個模塊組合好之后作為部件再組合在一起的。所謂,芯片就是把這些開關(實際上還有其他元器件,但是理解時可以忽略括號里面的這句話)集成在一起的模塊,也就是集成電路。為了配合開關更好運作,還要有一些電壓,電阻,電感,電容的界限值控制,確保其功能ok和壽命足夠。

集成電路里面的一個開關,通常就是一個晶體管,比如MOSFET。

開關與開關之間還要有金屬互聯才能作用,這就是電路。

一堆開關通過金屬互聯組成一個復雜的網,就形成了復雜的邏輯電路和控制電路,于是電腦就可以通過觸發后就自動運作,各種電器就可以通過觸發后就自動運作。

當然,如果要存儲數據的話還要有電容,電容在微觀世界里,就是兩片金屬板,充電就是1,放電就是0,一系列的電容搭配上mosfet就形成了內存芯片。

FAB廠干的活就是在襯底上來制造出這樣的電路:開關(晶體管)+其他器件(如電容)+連接導線(金屬互聯),做完之后,不能裸露,因此還需要有個保護層,就是鈍化處理。

做好之后就交付給下游封測廠去切割和封裝與測試,變成可交付給電子廠的部件,比如CPU(包括控制單元,運算單元等)、內存條等等。

襯底是制造電路的原材料,它是光滑的原片,FAB廠會在上面進行圖形化,然后通過增材減材和改性處理,把一堆類似的電路立體式地制造在上面,變成可出貨的成品。

開關有兩種,一種是通電就打開,一種是斷電才打開,我們要同時做兩種開關,就是所謂的CMOS(CMOS能耗比單純的PMOSFET和NMOSFET這是工程演進的一個結果。

從電子管到晶體管鍺晶體管,Si晶體管,PMOSFET和NMOSFET,CMOS,是對性能和應用側場景問題不斷解決和迭代的過程,現在先進制程大部分是采CMOS工藝加工),其大致晶體管制造、金屬層堆疊、鈍化層保護的工藝流程如下:

a 晶體管制造(CMOS)

STI:隔離出一個一個井的邊界,讓開關只在這個邊界里面加工。

NW/PW:注入離子,形成N井和P井

柵極制造:形成N井和P井的柵極

源極和漏極制造:注入離子形成源漏極,N井注入P,P井注入N,形成兩個PN結。

N是negative,P是positive,N就是引入負電荷,也就是多余的電子,P是引入多余的正電荷,就是空穴。

電子和空穴稱之為載流子。源極到漏極的方向是載流子的運動方向,也就是載流子是從源流入到漏(源頭流入一個漏洞,再通過漏洞流到電源)

?PMOS就是正(P)電荷從源流到漏,?NMOS就是負(N)電荷從源流到漏

電流是正電荷的流動方向,因此NMOS和PMOS的電流方向相反。

而NMOS和PMOS里面的N和P指的是溝道里面載流子是電子還是空穴來定義的,溝道的作用是聯通源和漏,因此源和漏極里面填充的是啥和溝道內的電性又是一樣的,所以,源極和漏極是引入N的就是NMOS,是P的就是PMOS。

bravo !

因為PMOS和NMOS電流方向是相反的,所以,把它兩的漏極連起來,就會得到一個從PMOS的源極到漏極再從NMOS的漏極到源極的CMOS電路。

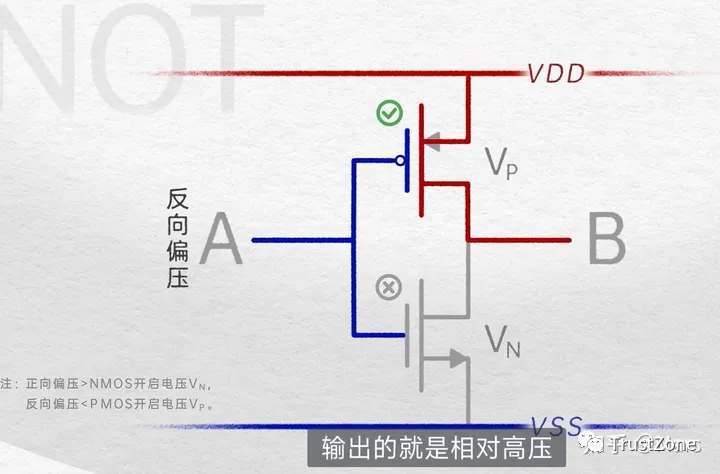

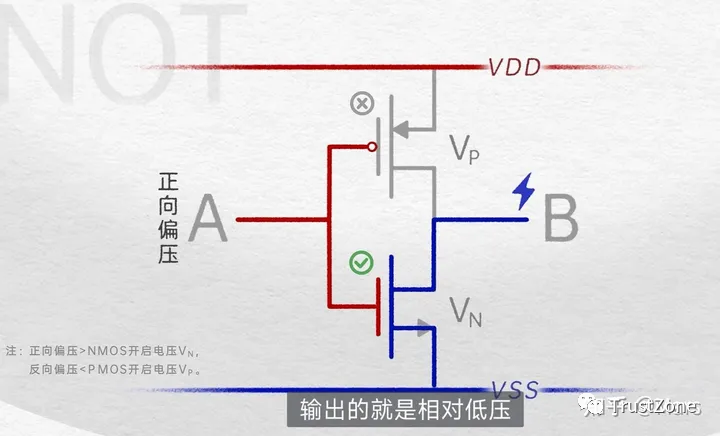

也就是一個非門電路:輸入端A低壓,輸出端B就是高壓;輸入端A高壓,輸出端B就是低壓。

?不同的連接和組合方式,形成基本的門電路,?不同門電路組合可以實現四則運算,構建起電子世界運算的基礎,?再加上電容器的使用,則存儲的問題也被解決。

能計算又能存儲,那么運算器和存儲器就可以被制造出來。它們不同的組合和連接,就可以得到不同的芯片,比如內存芯片,CPU芯片。

低阻值層:柵極、源極和漏極表面要生成一層低阻值物,用于后續金屬互聯層的鏈接點。

上面的加工過程并不是一個一個開關去加工的,而是全部一起加工,因此以sti邊界為例,就是先涂滿膠,再把邊界要加工的邊界顯示出來,然后去掉邊界的膠,再整個處理。

這樣沒膠的是我們要的,有膠的是我們不希望被加工到井邊,用膠覆蓋住的井里,加工完再把膠去掉,這樣邊界就加工出來了,后續再在這個邊界里面用類似的批量處理方法去一起加工出出一堆由源極、漏極和柵極組成的開關,一堆比如可以是幾千萬個或幾億個,乃至百億個。

這些晶體管連在一起就形成一個die(一個井),也就是所謂的裸芯片,也叫管芯。

STI是Shallow Trench Isolation的縮寫,意思是淺槽隔離。STI邊界是指相鄰STI結構之間的界限或分界線。較光滑和均勻的STI邊界可以減少電場濃度和電流泄漏,提高芯片的可靠性和性能。

一個die有多少個晶體管以及它們怎么連,通常是芯片設計公司會做好,變成版圖,然后再交給FAB廠,這就是所謂的"集成"電路的概念。

b 金屬層堆疊

底部器件制造完成之后,晶圓上就有非常多的MOSFET,它們彼此之間被絕緣氧化物隔離開,密密麻麻,但是又彼此獨立。

為了讓它們能夠彼此協作進行工作,就要將這些MOSFET鏈接起來,這些鏈接物通常是鎢,銅,也可以是其他金屬。

連起來的這些晶體管,導通就是1,不導通就是0,由柵極進行控制。電路越復雜堆疊層數就會越多,比如幾層到十幾層。die就是一個芯片,根據尺寸不一樣,一片晶圓上可以做幾十到幾萬個die,最后要切下來封裝。

6寸,8寸,12寸不同,還和溝道長度有關系,尺寸越大,做得越小,就可以產出越多,成本就越低。si基現在8寸,12寸為主,6寸及以下要慢慢淘汰,第三代半導體,比如SIC和GaN目前8寸能夠量產的廠商還是個位數,6寸和4寸還有市場。

這里的寸指的是晶圓的尺寸,是用來表示晶圓大小的一種單位。不同尺寸的晶圓可以用來生產不同的芯片,而不同尺寸的芯片則具有不同的性能和成本。

c 鈍化層保護

制造完成前面的器件層和金屬層之后,還要加一層保護,比如SiO2或者SiN將其包裹起來,再開幾個金屬鏈接點用于后續封裝使用(用于外部觸發)。基本上Wafer制造過程就完成,可以交給封測廠進行切割和封裝測試。

總體而言,晶圓來料表面是光滑平坦的,要在上面加工出錯綜復雜的器件和金屬互聯線路,需要經過增材、減材和改性處理才行。

這些過程主要和化學腐蝕與離子轟擊有關。

?其中增材就是薄膜相關工藝,?減材就是刻蝕,?改性就是注入相關工藝,

還有就是上述三個處理過程發生的具體位置通常要在晶圓上畫出來,以指示加工的范圍,則是光刻的工作。

?ET:刻蝕,用化學或物理的方法做減材處理,分為干刻和濕刻,要刻得剛剛好,不能過刻也不能不足,刻蝕率和選擇比就很重要。選擇比越大越好。刻蝕速率通常是固定值比較好,為了得到這個值就要經常做monitor,前量后量,再用公式算出來。刻蝕前通常會長一層氧化膜做阻擋層。刻蝕考慮的指標通常有:?Etch rate(刻蝕速率),?selectivility(選擇比,相對刻蝕速率),?uniformity(均勻度,坑坑洼洼),?profile(刻蝕圖形規則度:斜著刻,弧形還是垂直刻) ,?end point(終點的選擇,到了就停止再刻,比如要sio2)?TF:薄膜,在晶圓上面長膜,分pvd和cvd兩種,膜厚,均勻度,平坦度很重要。要獲得好的均勻度和平坦度,要在真空環境下來完成,為什么呢?因為真空環境,把金屬氣化之后就會變成無序四面八方去運動,就會更均勻。?DF:擴散/注入,擴散通常是把離子打到比較淺,再高溫加熱讓它擴散到深處,注入是直接用能量打進去,不要加熱,屬于可以常溫下下處理的一種工藝。要控制能力,劑量和角度。?PH:黃光,車間里面這個區域的燈都是黃色的,包括涂膠,曝光,顯影三大工序,膠分為正膠和負膠(負膠是曝光部分顯影后會留下來,正膠則相反,可以把負當作“附”著來輔助記憶),

原理是:光刻膠中含有感光劑,被照射后會發生化學反應,使得被照射部分和未被照射部分,接觸到顯影液時候的溶解速度相差三個數量級(比如3000)倍左右。

曝光時候,能量,焦距和曝光時間很重要,會影響尺寸和圖形的品質,在確定參數時,都會先做FEM(focus enerage matrix)。

光刻比較在意的有這樣幾個結果參數:

?分辨率,也就是一毫米寬的距離可以畫多少條清晰的線;?Overlay,也就是不同層之間的對準;?缺陷,做完光刻,不能有殘留。還有就是感光速率,太慢效率就低了,成本會變高;?另外就是膨脹,溫度會熱脹冷縮,影響對準。

如前文所述,四大模組制造產品,過程當中也是要穿插檢測進行測量,防止不良造成后段工序出現問題,比如:

?光刻不同層之間要確定套準偏差在規格以內,?刻蝕要關注刻蝕后的臺階,?薄膜要量膜厚等等。

做完之后,看產品,有些還有背金,就是把整個Wafer背面做減薄處理。

最后出貨前,還要進行電性檢測,以評價器件特性。

電性無外乎就是,電容、電阻、電流、電壓,一講就知道,只是把這些參數放到MOSFET的場景去而已。

如果把一個晶體管想象成一個開關,分為源,漏,柵極。柵極加電壓,電流就會從源極流到漏極。這樣一個簡單場景,它的理想狀態是:

?a.我要知道施加到柵極的電壓是一個固定值,同一個開關不能變來變去,這個是Vt,另一個是Vt+n,否則容易出現,開關沒打開的情況,這個Vt就是所謂的閾值電壓(Threshold Voltage),也就是產生強反轉所需的最小電壓。這個值是客戶根據使用場景設計時候就定好的,比如手機和汽車上用的MOS(開關),肯定就不一樣。因此,FAB做出來的結果要接近客戶的設計值。?b.當Vt確定后,往柵極加電壓,就要可以控制電流,這個加上去的電壓和被控制的電流它們之間的關系以及自己的穩定性也要被規范。柵極電壓叫Vg,v是電壓,g是GATE,柵極的意思。

根據原理,當柵極電壓Vg

?c.那加了一個固定的Vg電流是不是穩定的呢,不是的,實際會受環境影響漂來漂去,比如溫度高溫度低之類。那就卡一下最大電流,就是所謂的飽和電流。

也就是在柵壓(Vg)一定時,源/漏(Source/Drain)之間流動的最大電流Idsat,這里I是電流的意思。

?d.開時候有電流,關時候就要沒電流,這才是一顆正經開關,可是實際上也是很難的,所以只能追求它越小越好。Ioff,這里I是電流的意思,ioff叫關態電流。

Vg=0時的源、漏級之間的電流,一般要求此電流值越小越好。Ioff越小, 表示柵極的控制能力愈好, 可以避免不必要的漏電流(省電)。

?此外,還有Vbk(breakdown)、Rs、Rc等等用以評價器件特性。而這些特性其實與前面工藝過程息息相關,比如Vt就與poly CD、Gate oxide Thk. (柵氧化層厚度)、AA(有源區)寬度及Vt imp條件有關。

測量電性的是Wat和CP,其中,WAT是抽測(模擬器件,選幾個點),CP是全檢,會用到的探針卡,測到的ng的芯片,要用墨點掉,就是把晶圓上ng的那一些芯片打一個墨點,這個工步叫ink,封裝廠到時候就不會去封裝這些帶墨點的die,以及外觀檢驗和Packing真空包裝出貨。

后道和前道的信息流要確保通暢,才能有效防止不良品不會流到最終消費者手中。因此工廠里面就要有CIM系統來做制造輔助管理。

NG是指不良的芯片,而INK是指對不良芯片進行標記或識別的過程。

?CIM系統:計算機集成制造系統,它不是一個系統,而是與制造過程強相關的一系列系統的總稱,包括:?MES系統、?EAP系統、?RMS系統、?PC系統、?SPC系統、?YMS系統、?RTS系統、?RTD系統、?AMHS系統等。?MES:生產執行系統,用于管理車間的生產過程,起到防呆和追溯的作用,是工程師使用最多的系統,工藝,設備和制造崗位幾乎每天都要用到它。?EAP系統:設備自動化控制,上料后,系統會自動從上位系統,比如MES、RMS、APC獲取run貨信息給設備下指令加工,加工后把機臺數據采集起來傳給不同的系統進行統計分析和控制。?SPC系統:每次加工完成會有量測值,要進入到這個系統去進行分析,分析結果有異常就會自動限制機臺和lot的流動與運行。?APC:參數調優,比如根據光刻套準偏差計算補償值,實現自動調整機臺參數。?YMS系統:不同的Layer,要系統來進行疊圖分析,形成最終MAP圖,喂給機臺進行加工,實現MAP Control。?RTS和RTD:實現算法自動派工,達到車間效率最佳和平準化生產。?AMHS:自動物料搬運,用天車實現Lot運送。

晶圓廠體現的是制造的最高水準,每天海量的數據,靠人工無法處理,基本上都需要IT系統來完成,通過人機系統的協同,實現穩定和高質量的交付。

晶圓廠體現的是制造的最高水準,工業化目前最高水準的體現。

工業軟件追求的是一個穩定和防呆,通常技術比較舊,難用,界面密密麻麻一堆參數,功能模塊有幾百個。

曾經去產線,看到的ATE的機臺上面有個一個極簡的指導文檔被粘貼在機臺上,每個案件也被標注了step。

一個FAB通常要配一個一定規模的IT團隊對其進行維護和不斷地二開。

半導體廠追求的full auto,日常工作很多都要通過系統來完成,比如做實驗,就要在系統開單,解Hold也要在系統做動作等等。

因此模組工程師除了學習工藝和設備相關技能外,還要學習不同的系統操作。這些系統有些是國產,有些是舶來品,有些是外購有些是自研。

但是好在它們都是圍繞著晶圓制造的業務在服務,因此,功能服務對象是差不多,術語也大體一致,比如Secsion,你在這一家系統看到和其他家系統看到,它的意思都是一樣的。

一片Wafer從投片到出貨,會經過幾百步驟乃至幾千步。

前面的襯底制備,和后面的成品檢測外,中間的步驟就是一層一層的薄膜、光刻、刻蝕、擴散的循環,每一個層就是所謂Layer,層與層之間要對準,否則就有可能影響器件特性。

而影響層與層對準的可能是工藝參數,比如涂膠時候的轉速導致涂膠不均勻進而影響曝光之類。大概工藝影響的鏈條是這樣:

?工藝參數(Recipe參數)、?工藝特性(cd/ovl、profile…)、?器件特性(Wat可檢出電性:Vt、Ron、Loff、Rcvia、Rsheet、Continuty…;CP可檢出電性:RT/HT、Vt、Ron、Ioff…)、?產品使用性(可靠性),

日常分析的理想狀態就是要去把握它們之間的Corelation分析。

如果在具體產品的制造過程中,如果我們知道機臺的某個參數,比如:壓力、功率,它會影響到最終CP的哪個具體器件特性,比如擊穿電壓之類。

就可以將其集成到CIM系統里面進行卡控。日積月累形成制造系統知識庫,讓車間的抗擾動能力不斷加強,以提高良率、效率和降低單件成本。

基于這樣的目的,要有一堆人用系統的術語理解,從事不同的崗位,共同努力才能實現。

三、術語總結

3.1 與人相關

3.1.1 工作崗位

?CE:負責對接客戶的工程師?TD、RD:技術研發部門?PIE:制程整合工程師,類似產品經理和PM的角色,和客戶對接了解客戶需求帶回廠內,協調各個部門,評估量產可行性,關注最終產品的電性是否符合。?PE:工藝工程師,簡稱工藝根據規格要求設定機臺的Recipe,提升生產效率和良率。?工作日常:刷郵件有沒有被highlight,有沒有領導或者別部門的待處理事項;?夜班交接事項:Hold lot處理、機臺、產品相關事項的處理;?開會:Issue的處理、action item的進度;?處理 Hold lot、異常、各種項目協助工作;?hold 比例下降項目、良率提項目等?EE:設備工程師,簡稱設備 保持機臺的穩定:日常保養,確保不發生問題 發生問題了,去找出原因并解決。Down機要寫報告,新機臺的安裝和調試 hold lot reduction,cip continue improve plan,parts 管理 ,sop制作,fdc 監控逐漸衰退的trendchart,提前更換零件等等。

這些都是一些管理、維護和改善系統的概念,可能涉及到生產、運營、維護等多個領域。以下是對這些概念的基本解釋:

?Hold Lot Reduction:這是指減少庫存的一種策略。通過精確地預測需求,并保持合理的庫存水平,可以降低庫存持有成本并提高資金的流動性。

?CIP Continue Improve Plan:這可能是指持續改進計劃(Continuous Improvement Plan)。這通常是一種不斷優化流程、減少浪費、提高效率的策略。

?Parts Management:這是指零件或部件的管理。包括零件的采購、存儲、分發等環節。有效的零件管理可以確保生產的順利進行,同時還可以降低庫存成本。

?SOP (Standard Operating Procedure) Creation:這是指制定標準操作程序。SOP是指導員工如何進行日常工作的文件,可以確保工作的標準化和一致性。

?FDC (Failure Trend Chart) Monitoring:這是指對失敗趨勢圖的監控。通過追蹤和分析故障模式的趨勢,可以提前發現問題,并采取相應的措施防止故障的發生。

?Replacement of parts in advance:提前更換零件是預防性維護的一部分。這通常涉及到預測設備或系統的壽命,并在其達到壽命之前提前更換零件,以避免生產中斷或設備故障。

?PP:生產計劃?IE:工業工程師?廠務工程師?MFG:制造部?YE:缺陷改善工程師 工作日常:Defect Map,Defect trendchart分析,Setup KLA Recipe,hightline Module,追蹤process產生的問題,進行early Alert:DN以減小impact scope。比較關注缺陷,發現問題highlight Module,請他們改善。缺陷改善工程師(YE)的工作日常包括以下內容:

Defect Map分析:這是一種可視化工具,用于顯示缺陷的分布情況,可以幫助YE了解哪些區域或產品線存在更多的缺陷。

Defect trendchart分析:通過分析缺陷趨勢圖,YE可以了解缺陷隨時間的變化情況,從而確定是否需要采取措施來解決這些問題。

Setup KLA Recipe:這可能涉及設置或優化自動檢測缺陷的腳本或程序。KLA(Key Laboratory of Advanced Technology)可能是一個實驗室或研究機構,其研究的技術可能涉及自動化檢測。

hightline Module:這可能是一個系統或工具,用于高亮顯示或標記缺陷,以便更容易地識別和解決問題。

追蹤process產生的問題:這意味著YE需要找出是什么導致了這些問題,以及如何在生產過程中預防它們再次發生。

進行early Alert:DN以減小impact scope。這可能涉及到盡早發現并報告問題,以便有足夠的時間來制定和實施解決方案,從而最大限度地減少對產品或服務的影響。

?TO:生產技術員 線上作業員,按照SOP進行作業。

SOP指的是標準操作程序

3.1.2 職位

臺廠在高端電子代工占據全球半壁江山,公司都很大,幾萬人到幾十萬人不等,整個職位等級比較規整,他們貌似基本上實現了全行業標準化,一個協理出來,大概就知道是什么層級的管理層。

相對而言,大陸企業的職位體系就各個公司都有很大差異,一個經理你就不好知道他是什么樣的管理層。

半導體行業受臺灣影響比較大,整個職位體系就與臺廠相近。

臺廠典型職位等級是:線長(班長)、組長、課長、部長、專理、副理、經理、處長、協理、副總、總經理、副總裁、總裁(臺)。

大陸半導體廠基本上也是裁剪使用這一套,基本上會有這些職務:班長、課長(科長、課經理)、經理(部經理)、處長、總裁這樣,其中省去了一些大陸不習慣的專理和協理這種稱呼。

3.2 與設備相關

?Equip:機臺?Equip Group:機臺組,代表的是一種加工的能力(Capability),比如:AA層 Photo 涂膠,代表這個能力組的設備可以加工此層的涂膠,它具備這個能力。能力組的屬性還有許多,比如Recipe等。設備和能力組是多對多的關系,代表一個機臺用不同的參數就可以完成不同的加工,也就是具有不同的能力,按S95標準是使用Capability比Group更準確。?Recipe: 配方/菜單,用以定義機臺某一組加工參數和job process的集合。比如:感應到片子、抽最上面一片,進腔體1,抽真空至xx,過2min,移動到腔體2,使用xx參數加工xx時間,破真空…,把片子放回原Slot(槽位)。這樣一個包含傳動、流程和過程參數組成的集合就叫Recipe。?subEquip: 子設備,如chamber和loadport?Chamber: 腔體?Loadport: 上料口?job: 機臺內部的加工過程,包括步驟以及每個步驟的腔體和對應參數和時間等的一個集合?打標機: 用激光技術在Wafer上面刻上ID?刷洗機: 打標會產生顆粒,因此需要進行刷洗?顯微鏡: 洗的干不干凈,可以用顯微鏡看?涂膠機: PR Coat,通過旋轉在Wafer上勻膠,分正負光刻膠兩種,正膠見光死,負膠見光活?曝光機: 給光刻膠曝光,將Mask的圖形轉移到光刻膠上,光刻膠是高分子有機物,叫光致抗蝕劑。比如負膠被光照到地方會發生交鏈反應,原本線型結構變成網狀結構,到顯影液中就不會去掉而被保留。正向光刻膠,則被照的地方會發生降解,而更容易被顯影液溶解。?大面積透光為明場光罩板(Clear Mask),大面積不透光為暗場光罩板(Dark Mask),GDSII定義的圖形區不透光則對應為Clear Mask,反之則為Dark Mask?顯影機:給光刻膠顯影,讓圖形顯示出來?DUV、EUV***,是讓圖形縮小的設備。?Season片: 機臺啟動后,投個Season片進行暖機。不同機臺或者Chamber的暖機機制差別很大,有些是For Recipe的,比如從A Recipe切換到B Recipe就要暖機; 還有是For idle時間的暖機,比如停機多久就要暖機。當然,出了暖機還有冷機,就是比如切換到某個Recipe 必須冷卻一段時間才能Run貨。?Constraint:機臺限制,包括有正向約束,反向約束,goloden,唯一正向約束,其中,黃金約束是同組設備哪些可Run,哪些禁Run。?parts:零部件?ring:環,零部件的一種?target:靶材

3.3 與物料相關

?Substrate: 襯底,是由半導體單晶材料制造而成的晶圓片,是FAB廠從供應商采購的原材料,它也可以進行外延工藝加工生產外延片。?背面刻號: 襯底來料背面通常會有供應商刻的追溯ID,是一串數字和字母組成的流水碼,叫T7 Code?Spec: 參數,來料關注的一些技術參數,比如厚度,電阻率之類的關鍵參數信息。還有工藝加工過程的參數也是叫Spec。參數通常會設置規格,超規格一般的處理是Hold?PN: 料號,不同供應商,不同材料參數的襯底會有不同的料號,和Raw material一樣的意思,站在供貨方角度叫PN,站在收貨方角度就叫原材料。?EPI: Epitaxy外延片,經過MOCVD工藝,可以在襯底上長一層幾微米的單晶,可以與襯底為同一材料,也可以是不同材料(同質外延或者是異質外延),由于新生單晶層按襯底晶相延伸生長,從而被稱之為外延層。?Wafer: 晶圓,口語叫片子,是一個統稱,應該是包含外延,加工過的襯底和裸片?DIE: 晶圓上面的一個芯片,也叫管芯,比如一片6寸的晶圓上可以制造3000個Die?Lot:若干個晶圓組成的一個批次叫Lot,比如8片一個Lot,25片一個Lot這樣,通常根據產品,這個數量有一個常規值。通常會用一個ID進行標識。?NPW片:非產品片的總稱,包括:結構片、監控片(Monitor)、QC片、Season暖機片、Dummy片?QC片: 定期檢測機臺參數是否OK,比如刻蝕速率、顆粒是否OK,就會投QC片子進去加工來檢測參數?offline:與Lot加工處理不相關的定義為offline,比如設備PM、NPW的處理過程、輔助工具的處理過程的一些數據監控?Inline: 與LOT加工直接相關的或者是監控LOT的參數屬于Inline。?SPC:統計過程控制,用以監控生產過程的穩定性,是一套IT系統。包括:控制圖查詢、異常查詢等。比如膜厚,會監控單點規格和均值。超管控(OOC/OOS)會觸發郵件報警和Hold,還有一些判異規則:比如連續七點上升或下降之類也會有相應處置。

SPC Rule通常要結合實際使用,比如tf的工藝特性是隨著時間推移,某些參數會逐漸下降,那么就可以啟用連續下降的Rule。但是有些是非正態分布和連續的值,比如缺陷數,這些就卡一個spec就行。在應用spc的時候,終極目標是持續減少普通原因,抓住特殊原因,但是也要兼顧工程師loading。

客戶給一個規格,比如99~100,工廠能不能做到,就要去抓在線數據,算出中心值和分布情況標準差,然后和客戶要求的上下限放在一起形成控制圖。天天這樣算太麻煩,于是就有指標來協助,比如cp和cpk。

?cp常識理解就是制程能力,能力越強,波動范圍越小,也就是cp值越大,波動范圍越小。純公式理解也是這個結論,客戶要求的規格Range/實際的6西格瑪。波動小,代表分母小了,因為分子不變所以cp就大。一般大于1.33是好的。

但是波動大小之外還要考慮中心點均值,所以還要看cpk值。

?OOC/OOS:針對規格或控制圖的兩對控制線,比如目標值是100,ooc是-99.5和100.5(管控線)、oos是-99和101(規格線),OOC和OOS主要是Range的不同。理論上oos就要報廢的,可是實際工作中,由于人性,大家設置規格時候都會層層給自己buffer,所以也會出現超過之后,還往下放的情況,只是開一個DRB做監控。?Batch:若干個lot和NPW組成的集合,產品+非產品一起進去加工,出來后,把NPW拿去測顆粒(Particle),用來判斷產品上的顆粒水平,NPW是光片上面沒圖形測得更準。比如:爐管通常都是多個Lot一起組成Batch放在晶舟投進去加工。?Hold: 把片子鎖住不讓往后流片,執行此動作的系統是MES?Hold Ratio:hold lot占WIP的比例,用來考核Module處理Hold lot的指標,通常會有不同部門都有自己的target,不能高于多少?wip:work in process,在制品?Release: 解鎖,片子可以繼續往后流?skip:跳步?ship:出fab的最后一步?Future hold: 提前設置好片子要Hold在未來的哪個工序?MES: 生產執行系統,用于管理生產過程的IT系統, 包括:?對生產過程和物理設施的建模、?過程監控和追溯等功能,對下連接EAP、橫向對接WMS、SPC系統和物流系統、對上連接ERP系統,也會和OA系統對接?issue: 產線出現的問題,Triger Issue的因素很多,大概包括以下幾個來源:工程師發現、系統發現、客戶發現。通常系統發現的影響程度最小、工程師次之,客戶發現最受重視,大部分是這樣,不一定全是。?OP meeting:跨部門的生產會議。參會成員包括:Module、制造部、質量、TD、PIE、YE、MPC、計劃、市場、廠務等,一般是一級領導參會。每天議題固定,主要包括:投片和產出進展、重點批次的進展和提前準備通知、昨晚的Down機情況以及一些AR的跟進。其他部門的一些重要議題等。發生重大Issue一般要準備報告來op匯報。是工廠里面重要的拉通對齊和highlight會議。?Particle: 顆粒,就是金屬顆粒,灰塵這些附著物,會影響器件性能,這是半導體殺手。?OTD:on Time delivery,準時交貨率

3.4 工藝方法相關

?PWQ:為了更好地回避晶圓之間工藝參數的漲落對確定工藝窗口的影響,可以在同一片晶圓上改變曝光能量和聚焦度,再用缺陷檢測的方法來確定最佳曝光條件。這一工作被稱為工藝窗口的再驗證(process window qualification, PWQ)?split:分批?merge:合批?optimize?parameter 的 correlation確認?SRC:split runcard,分片單,做實驗時候要從主FLOW上開分片單,跑不同條件?PRS:process Release standard,工藝放行標準,開發新工藝時候,Release要有一個標準。?Str:split testing release,小批量驗證?mstr:mass split testing Release,大批量驗證?BSL:baseline,基線,基準,baseline機臺指的是作為基準的設備,比如第一臺研發成功的設備,后續的就屬于擴機設備,而baseline spec就是確定了作為基準的規格,這個是一個形容詞,可以用在很多場景,這里只舉例兩個而已。?CD:關鍵尺寸?inspection:檢查?ADI:after develop inspection,顯影后檢查?AEI:刻蝕后檢查,e是刻蝕,ai和adi一樣?monitor:監控,比如做QC監控機臺長膜是否正常

3.5 工作場景相關

?測機 做Daily Monitor,用以監控機臺的THK(厚度)、PA(顆粒)、U%(均勻度),并形成offline Chart。?缺陷監控 用KLA缺陷檢測機臺掃發現Defect,于是Highlight defect 給PE owner,工程師就要確認SPC 有沒有OOC和OOS,或確認FDC的log有否異常,若發現機臺有問題,就會PM,PM時可能要Calibration 某些部件,PM之后,要確認BaseLine后,才可以Release給MFG。?Prob Card:探針卡,Wafer生產完成之后,出貨前要做CP測試,用于連接Wafer和測試機臺(tester)的治具。?MAP:晶圓制造是By Layer制造,中間生產的關鍵層會去掃Defect,最后成品會測Wat和CP,最終結果會把幾層的結果做疊圖,形成Map,再Ink掉fail Die。?解Hold lot 產線出現Issue,MES hold lot,工程師確認發現是Q time 超 ,初步判定不會產生Defect,也不會影響良率,于是做Release 處理,避免影響Hold Ratio?PCRB:Program Change Review Board,項目變更審查委員會 FMEA、PSM、DOE、SPC、Hold Rate、Rework Rate、PCRB、YE、8D Report?weekly:一周一次?bi-weekly:兩周一次?MO:Miss operation double confirm?cip:continue improve plan?bsk:best known method 最佳方法?AI/AR:action item/request 應執行項目?fyi:For your information?ndr:non-conforming disposition report 異常單,全稱忘記了 有問題開單處理?OCAP:out of control action plan失控行動計劃,比如EDC OOS了,第一步是確認量測數據有沒有錯,第二步是重新量,第三步是針對機臺和片子的處理等等,這樣的一個流程方案。?DRB:Disposition Review Board,針對lot,比如超Spec了往下放就要開drb進行追蹤。?Event abnormal review:重大的品質事件要開EAR,比如某個工序持續出現同樣的defect map。?mrb:material review board,重大物料異常要開MRB,大批量用錯原材料,用錯光刻膠等等?DRB,EAR、MRB:大概就是異常的處理流程,DRB是確認要不要追蹤電性,比如介質厚度便薄可能會影響電容,就要追蹤一下子,這個lot owner層級可處理。出現重大事件,就要啟動EAR和MRB處置流程,這個流程層級更高,要提交8D報告。?FMB:Factory Monitoring Board

3.6 術語應用進階

一個Lot,通常沒一層都要做鏡檢、掃Defect,測CD、Defect會出MAP圖,比如刻蝕不凈和殘膠等,CD可監控OOC、OOS進而知道在線工藝穩定情況,WAT會模擬器件測值,CP全測,為ink做數據支撐,defect疊圖分析也可支撐ink,最終得到shipping Yield。

?Lot:在半導體制造中,一個Lot通常指的是一批經過相同處理步驟的晶圓。鏡檢:這是一種通過顯微鏡對半導體表面進行仔細觀察的方法。它用于檢測各種缺陷,如刻蝕不凈和殘膠等。?掃Defect:這可能是一種使用激光或其他能量源來檢測和識別半導體表面或體內的缺陷的技術。?測CD:這里的CD可能是指關鍵尺寸(Critical Dimension),它是一個衡量半導體結構尺寸的參數。通過測量CD,可以監控在線工藝的穩定性,以及判斷是否符合設計要求。?Defect會出MAP圖:MAP圖可能是一種表示缺陷分布的可視化工具,類似于地圖。它可以幫助分析和理解工藝中可能出現的問題。?WAT:半導體硅片在完成所有制程工藝后,針對硅片上的各種測試結構所進行的電性測試。通過對WAT數據的分析,我們可以發現半導體制程工藝中的問題,幫助制程工藝進行調整。?CP全測:這可能指的是對每個芯片進行全面的晶圓測試,以確保其符合規格和性能標準。?為Ink做數據支撐:這里的Ink可能指的是在晶圓上標記或識別不良芯片的過程。數據支撐可能指的是為這個過程提供必要的數據或分析,以幫助確定哪些芯片需要被標記或隔離。?defect疊圖分析也可支撐Ink:這意味著通過對缺陷進行詳細分析,可以進一步支持芯片的標記或隔離過程。?最終得到Shipping Yield:這是指最終產品的良品率或出貨率。經過所有這些步驟和分析后,就能確定最終產品的質量和良品率。

-

半導體

+關注

關注

334文章

26171瀏覽量

209193 -

模組

+關注

關注

6文章

1346瀏覽量

29861 -

FAB

+關注

關注

1文章

28瀏覽量

9797

原文標題:三、術語總結

文章出處:【微信號:半導體封裝工程師之家,微信公眾號:半導體封裝工程師之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FAB工藝流程入門

FAB工藝流程入門

評論