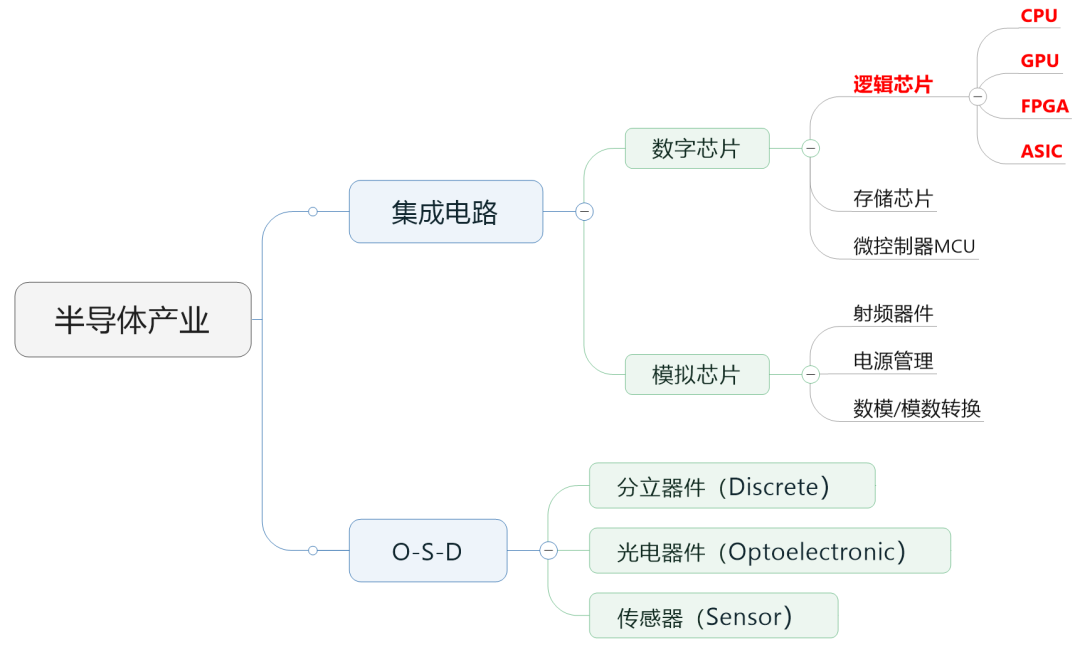

芯片設計這個行當,從大的方面講,主要分模擬和數字兩大塊,而每大塊又分前端和后端,我想大部分同學對這個肯定是非常清楚的,下面就數字電路聊聊芯片設計的一些事情,就是芯片設計有哪些活要做,這并不是全面完整的系統介紹,只是個人的了解和總結, 希望拋磚引玉,也許不全面,不正確,歡迎大家指正和補充。

說到數字芯片,不能不說FPGA,這種是可編程的數字電路,用法原理也不說了,數字電路設計的目標就是把這些功能做成我們自己專用的ASIC/SoC,這樣無論面積、成本或者安全性等都能有保證。

從流程上講,數字芯片設計的大致步驟就是系統與功能定義、RTL實現驗證、 綜合及可測試性設計、ATPG仿真、時序分析到自動布局布線(APR),直至交付fab的GDS網表。

這個流程是可以反復迭代的,對于不同類型芯片,如純數ASIC或混合電路(mix-signal)及系統級芯片(SoC),每一步的方法和具體實施流程上可能又有所差異。下面就這些基本流程分步談一些主要問題。

系統設計主要涉及到功能定義及架構設計、總線架構的配置、模塊設計、數據流的分配、時鐘的設計等問題。總線包括模塊之間,模塊與MCU核之間,外部主機和芯片之間通信,或者測試需要等等一系列因素。時鐘涉及到數據流的規劃、通信接口或內部MCU的時鐘約定、工藝條件、功耗等因素。模塊需要明確接口和定義。

在系統級設計上, 特別是很多數模混合電路中或對功耗有特別要求的電路中,還要有電壓域的設計,不同模塊之間,功能模塊和接口之間可能都需要根據工藝條件、功耗要求設置不同的電壓。

無論是時鐘,還是電壓,都可以通過控制開關來實現功耗的要求,時鐘實現比較簡單,在大部分電路中都可以實現這種時鐘控制。電壓控制一般是實現在集成有電源管理芯片的較大規模芯片上,但未來趨勢是即使沒有電源管理芯片,電壓的gating也需要納入考慮范圍。

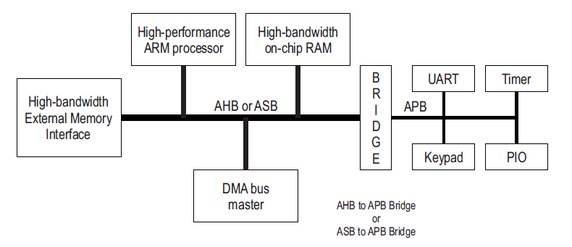

在 SoC系統設計上,一個重要的環節是MCU 內核的選型,現在常用的內核一般是ARM、較老的ARM7、ARM9等系列,較新的是三大系列Cortex -A 、R、M,具體的用途不做詳細描述,選定好后,根據需要進行設置,一般做硬件的人不需要對它的指令集了解太多,但是需要了解它的總線接口、數據總線、指令總線, 以及存儲系統的設計,一般需要安排ROM、 RAM分別作為指令和數據存儲器,由于ROM是不可更改的,一般也需要加入flash作為補丁程序寫入地,也可能需要外部存儲器或者DMA控制器來增加外部存儲空間。地址的分配是按照功能需要來進行的,現在有很多工具如synopsys的DesignKits可以產生外部總線代碼及進行地址分配。

第一步完成系統和功能定義后,要實施的就是RTL, RTL是專門描述硬件電路的工具語言,有Verilog和VHDL。RTL的特點就是硬件上的同時觸發性,不同于軟件的按順序執行,電路由時序邏輯和組合邏輯組成。時序邏輯在物理構成上就是一些寄存器,這些寄存器受時鐘控制,寄存器代表了電路中的數據或控制信號,這些信號受時鐘的驅動流動。組合邏輯是不受時鐘控制的電路塊,組合邏輯顧名思義通過一些信號的組合直接生成一些邏輯結果。

RTL設計中,一大問題是異步設計問題,異步數據的處理根據不同情況有很多方式,最簡單的對異步的電平信號,可以直接在新的時鐘域中加2級寄存器來隔離,避免不定態的發生。對于總線的處理或者脈沖的處理,則需要同步模塊。同步模快一般是指需要握手信號,就是前一級時鐘告訴采樣的時鐘——信號ok了,采樣的第二個時鐘再去采樣,采好后再告訴前一級時鐘,我搞定了~那樣前一級時鐘就可以換數據或做其他處理。

有一種情況就是前一級時鐘太快,造成第二級來不及傳遞信號,則需要加入FIFO作為隔離,就是讓那些數據先放好,我在慢慢來取。這個FIFO的設計涉及到讀寫地址的判斷,寫滿或讀空都需要作相應處理,讀寫地址之間的判斷只能在其中一個時鐘域中進行,這本身又涉及異步信號的處理問題。一般用格雷瑪解決,或者有些地方直接可以判斷地址高位, 這些方法的目的就是不能讓地址在比較的時候不穩定。

RTL設計中,時鐘本身的設計問題也要注意,我們在一個芯片中,盡量把時鐘產生電路放在一塊,主要是從綜合DFT的角度去考慮的,讓這些時鐘統一管理和約束。時鐘的分頻、切換也要專門處理,否則容易產生毛刺等事情。

RTL設計中還有很多需要注意的問題,比如可綜合性,還有要考慮到電路的面積,以及響應速度等等,這些問題是RTL coding的基礎問題。代碼寫完后,需要進行的是驗證工作,下面談談這方面的事情:

芯片驗證一般有這幾個層面,一個是RTL級或者Netlist( pre or post PR with SDF ),這個也是一般意義上的芯片驗證工作, 一個是FPGA級的,也是RTL,只不過download到FPGA中,借助硬件環境,也可以直接做應用實驗。

芯片驗證的工作量在芯片設計中占據了大部分的時間和精力,無論是哪種驗證,都需要搭建測試平臺(testbench),驗證平臺從軟件結構上模擬芯片的工作環境。既有清晰的連線結構,也有完成這些測試所需要的非結構性的函數或任務包。測試平臺中的被測試芯片是RTL級的,測試向量或者說施加的激勵可以是 verilog/VHDL,HDL語言本身就具有比較完善的行為級描述功能,也可以滿足絕大部分測試平臺的搭建和測試激勵的產生,當然我們面對更復雜的設計,或追求更高效率,也可以使用其它被編譯器兼容的語言, 如C/C++、SC、SV等等。

很顯然,測試激勵是有時間概念的,是按順序進入和流出芯片的,使用的這些非電路描述語言和功能和軟件幾乎是沒有區別的,所以驗證中也越來越多地使用軟件的一 些技術, 如面向對象的編程技術、SystemVerilog、 Specman E等。

無論傳統的驗證還是最新的驗證方法學,都需要追求驗證的收斂性,即驗證完全是自動化的檢測,除非debug, 我們無需通過波形判斷測試通過與否。

驗證系統中,使用的一般是存儲器的模型加上文本格式的代碼文件, 一般實現是直接通過系統讀入指令把文件讀入到存儲器模型中。(有些仿真工具可以直接通過選項導入,類似SDF文件,如工具nscim)。

仿真器可以直接寫出指令執行的log,以用于debug,不過現在有更先進的方式用于復雜SoC驗證, 如Codelink工具,能夠在原仿真器的基礎上,建立起MCU和HDL電路已經軟件的關系,通過展示波形和固件(firmware)源碼的鏈接進行更方便的debug。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5317瀏覽量

120001 -

芯片設計

+關注

關注

15文章

1001瀏覽量

54811 -

RTL

+關注

關注

1文章

385瀏覽量

59697 -

SoC系統

+關注

關注

0文章

52瀏覽量

10665 -

電源管理芯片

+關注

關注

21文章

719瀏覽量

52567

原文標題:芯片設計有哪些活要做?

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

活細胞的“聚光燈”——前沿活細胞成像的案例分享

活柱激光熔覆修復技術

cyw43012的低功耗保活是如何應用的?

封裝對高頻芯片設計有何影響嗎?

聊聊AMBA協議的evolution過程

聊聊芯片設計有哪些活要做?

聊聊芯片設計有哪些活要做?

評論