今天,小弟和大家談一談某國產(chǎn)FPAI芯片的AI系統(tǒng)方案以及參考設(shè)計實例。

1)FPAI芯片架構(gòu):博采眾長、兼容并蓄

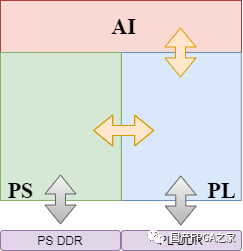

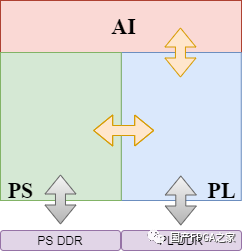

首先,我們簡單了解下FPAI(Field Programmable AI)芯片。FPAI芯片,創(chuàng)新性地采用了異構(gòu)融合架構(gòu),即在一顆die上集成了高性能SOC(PS)、大容量FPGA(PL)、AI加速引擎(AI)三大模塊。該異構(gòu)融合架構(gòu),可謂“博采眾長、兼容并蓄”,融合了各異構(gòu)模塊優(yōu)勢,特別適合AI計算。其中,高性能SOC優(yōu)勢在于控制和通用計算,使得能在單芯片上運(yùn)行完成完整的AI計算;大容量FPGA優(yōu)勢在于可重構(gòu)和高速接口,解決了長尾算子的難題,適應(yīng)了AI算法不斷的迭代升級趨勢;AI加速引擎優(yōu)勢在于高性能、低功耗地完成卷積等計算密集型算子的計算。

圖1 FPAI芯片架構(gòu):異構(gòu)融合

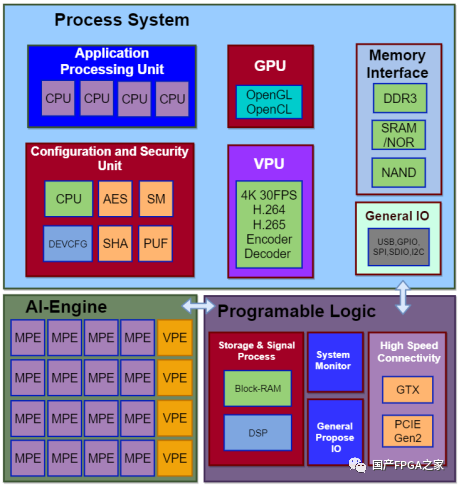

具體的,以下是某款國產(chǎn)FPAI芯片,該芯片資源很豐富。PS部分,有四核處理器CPU、視頻編解碼模塊VPU、圖像處理模塊GPU等;PL部分,有444K的邏輯資源,16個高速接口GTX;AI部分,有高達(dá)27.52TOPS的int8算力,精度支持int8和int16,配合AI編譯器支持快速部署

圖2 某國產(chǎn)FPAI芯片資源

綜上,該顆FPAI芯片支持豐富的AI應(yīng)用場景,特別適合邊緣融合端的AI應(yīng)用場景。

2)FPAI系統(tǒng)方案:好馬配好鞍,好船配好帆

從芯片到系統(tǒng)產(chǎn)品,還需設(shè)計硬件,開發(fā)FPGA程序,開發(fā)軟件程序,部署AI網(wǎng)絡(luò)等。系統(tǒng)方案及對應(yīng)的參考實現(xiàn),提供了一整套完整的解決方案參考,能夠幫助用戶方便、快速、高效、可靠地完成自己產(chǎn)品的設(shè)計。 所謂“好馬配好鞍,好船配好帆”,不同芯片需要適合的系統(tǒng)方案以及對應(yīng)的參考設(shè)計。

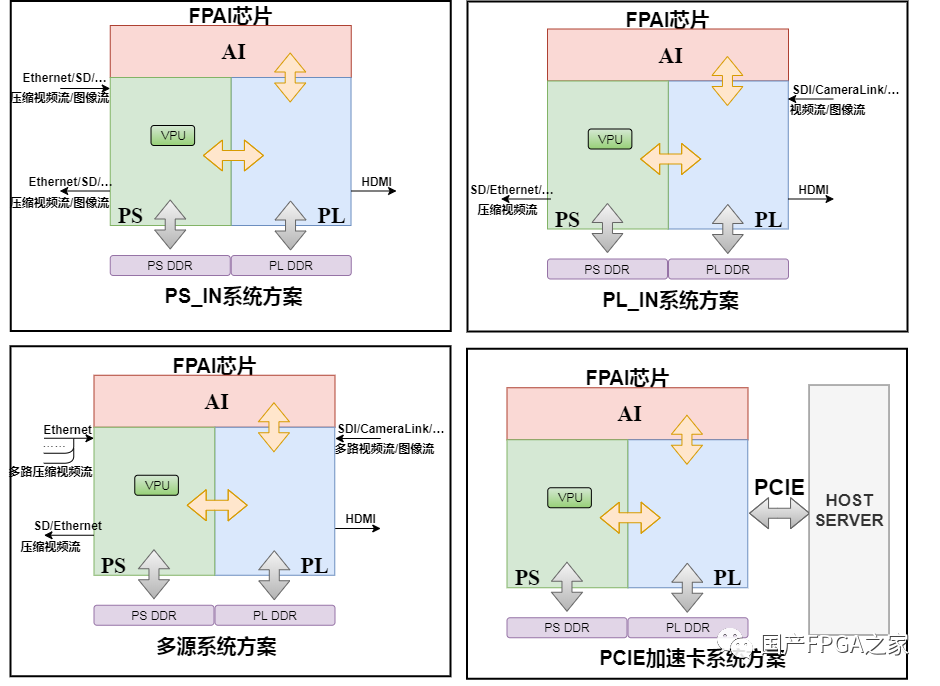

首先,F(xiàn)PAI芯片是PS+PL+AI的架構(gòu),對外接口管腳位于PS、PL模塊,因此依據(jù)外部數(shù)據(jù)流輸入的管腳,設(shè)計了PS_IN、PL_IN的系統(tǒng)方案,以此對應(yīng)不同的內(nèi)部控制流數(shù)據(jù)流方案;然后,F(xiàn)PAI芯片的AI峰值算力達(dá)27.52Tops,能夠支持多路數(shù)據(jù)流的不同的AI計算,視頻編解碼模塊能支持多路視頻流的壓縮,可編程邏輯資源也支持多輸入的高速數(shù)據(jù)流接口,因此依據(jù)以上算力特點(diǎn),設(shè)計了多源的系統(tǒng)方案,以此也符合了邊緣融合端的AI應(yīng)用特點(diǎn);此外,PCIe加速板卡的系統(tǒng)方案,配合主機(jī)服務(wù)器,完成AI的推理計算加速。

綜上,基于FPAI芯片的架構(gòu)、算力、資源、輸入數(shù)據(jù)流來源、應(yīng)用場景等特點(diǎn),分別制定了如下4種系統(tǒng)方案,基本能夠涵蓋FPAI單芯片下的各種應(yīng)用場景。

(1)PS_IN系統(tǒng)方案

(2)PL_IN系統(tǒng)方案

(3)多源系統(tǒng)方案

(4)PCIe加速卡系統(tǒng)方案

圖3 FPAI芯片的系統(tǒng)方案 一個系統(tǒng)方案可能有多個具體的參考實現(xiàn),但對應(yīng)的設(shè)計架構(gòu)是一致的,可能只是具體內(nèi)部實現(xiàn)有區(qū)別。參考設(shè)計會提供一整套參考方案,包括硬件設(shè)計、FPGA設(shè)計、軟件設(shè)計的代碼和相應(yīng)文檔。因此,想要基于FPAI設(shè)計系統(tǒng)的朋友,可以依據(jù)自身的應(yīng)用場景需求,選擇上述系統(tǒng)方案的參考設(shè)計。

3)多路PL_IN+VPU編碼的參考設(shè)計實例

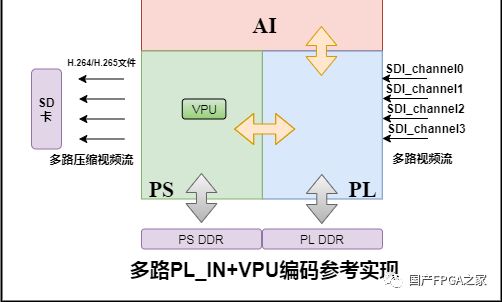

好了,說了這么多,大家等不及要看具體的參考設(shè)計實例吧。以下會介紹多源系統(tǒng)方案的一個參考設(shè)計實例:多路PL_IN+VPU編碼的參考設(shè)計,分別從參考設(shè)計概述、硬件板卡介紹、FPGA工程介紹、軟件工程介紹、實例功耗介紹等5部分來介紹該實例。

3.1 參考設(shè)計概述

輸入:4路SDI攝像頭,默認(rèn)分辨率和幀率設(shè)置1080p@30Hz;

輸出:SD卡,H.265/H.264格式文件格式;

VPU:分辨率1080p,YUV422輸入, 輸出 H.265/H.264,默認(rèn)編碼幀率設(shè)置30Hz;

檢測:運(yùn)行示例網(wǎng)絡(luò)Yolov5s AI檢測,帶檢測結(jié)果的視頻壓縮到SD卡。

性能:4路1080p@30Hz輸入,AI+VPU編碼,每一路30fps。

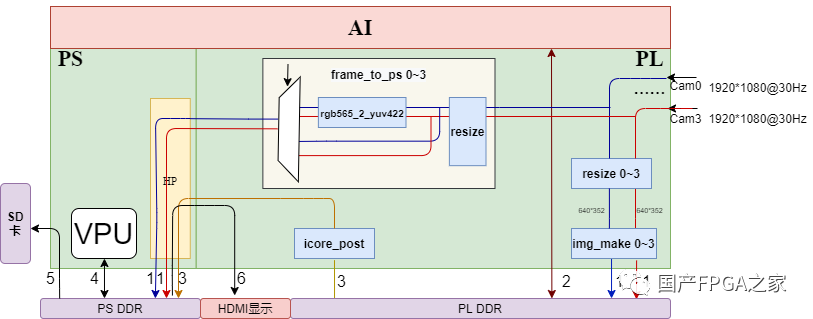

圖4 多路PL_IN+VPU編碼的參考實現(xiàn)框圖

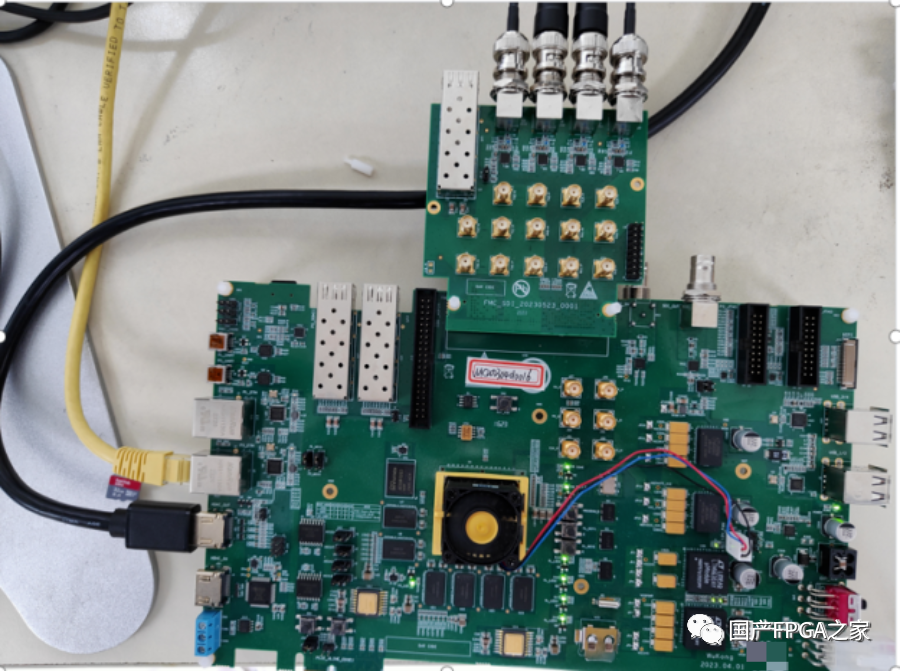

3.22 悟空硬件開發(fā)板簡介

如下圖,采用SDI接口攝像頭輸入4路視頻到板卡,悟空硬件板卡上主芯片F(xiàn)PAI芯片;SD卡,儲存和啟動Linux操作系統(tǒng)啟動文件和根文件系統(tǒng);1GB PS DDR和2GB PL DDR,用于運(yùn)行操作系統(tǒng)和AI;通過子卡接入的4路SDI視頻接口;網(wǎng)口、串口、JTAG調(diào)試接口等。

圖5 悟空硬件開發(fā)板

3.32 FPGA設(shè)計介紹

首先,整體數(shù)據(jù)流如圖所示:

圖6 多路PL_IN+VPU編碼的數(shù)據(jù)流

Step1:對應(yīng)圖中的數(shù)據(jù)流1,Cam0~Cam3為4路不同的SDI攝像頭視頻流,幀率1080p@30Hz。對于每一路SDI攝像頭視頻流,復(fù)制成兩路,一路經(jīng)過resize、image_make模塊完成AI預(yù)處理后存入PL_DDR,供AI檢測使用;另一路經(jīng)過resize、rgb565轉(zhuǎn)為yuv422(可選)通過HP接口存入PS_DDR,供后續(xù)畫上檢測結(jié)果后VPU壓縮用或者HDMI顯示用。

Step2:對應(yīng)圖中的數(shù)據(jù)流2,啟動AI訪問PL_DDR完成AI的計算。

Step3:對應(yīng)圖中的數(shù)據(jù)流3,最后一層特征圖,經(jīng)過icore_post模塊處理后,通過HP接口寫入PS_DDR。PS完成剩余后處理計算,得出AI檢測結(jié)果,畫在PS DDR上的視頻幀上。

Step4:對應(yīng)圖中的數(shù)據(jù)流4,啟動VPU,對含有結(jié)果的視頻幀壓縮成H.264/H.265格式。

Step5:對應(yīng)圖中的數(shù)據(jù)流5,將壓縮視頻流寫回SD卡。 Step6(可選):對應(yīng)圖中數(shù)據(jù)流6,將檢測框的視頻顯示到HDMI顯示屏。

其次,介紹以下子數(shù)據(jù)流通路的實現(xiàn)

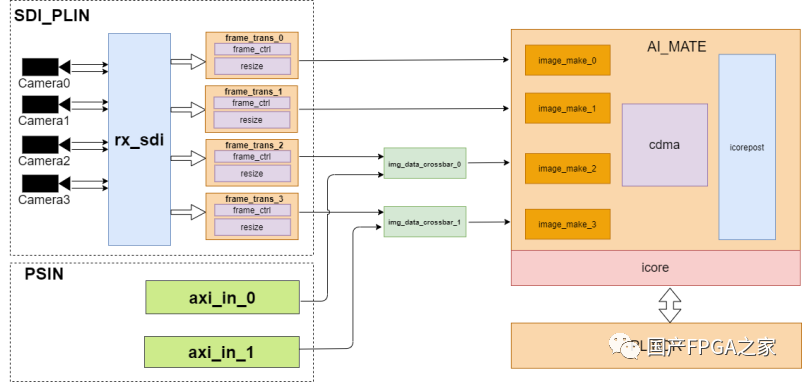

(1)Camera -> PLDDR的邏輯通路實現(xiàn)

圖7 子邏輯通路Camera -> PLDDR

輸入的4路視頻流幀率為1080p@30Hz,均以serdes 差分對接入FPGA端口,通過rx_sdi模塊解析為rgb888數(shù)據(jù)格式。然后經(jīng)過frame_trans模塊resize成AI計算所需要的尺寸。 在一些應(yīng)用場景中,輸入數(shù)據(jù)可能預(yù)先存儲在了PS DDR中,因此本工程也預(yù)留了2路獨(dú)立的PSIN數(shù)據(jù)通路,通過HP口讀取數(shù)據(jù),轉(zhuǎn)變成AI_MATE接口規(guī)范好的數(shù)據(jù)總線格式。這兩路PSIN數(shù)據(jù)通過img_data_crossbar_0/1模塊分別與CAM2/3視頻流數(shù)據(jù)進(jìn)行仲裁,各自選出1路輸入給AI_MATE端。

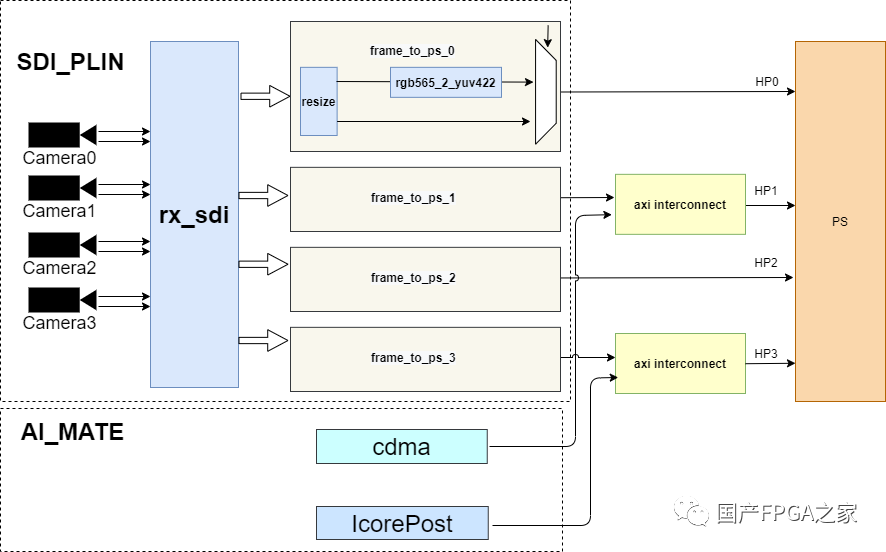

(2)Camera -> PSDDR的邏輯通路實現(xiàn)

圖8 子邏輯通路Camera -> PSDDR 將CAM視頻流數(shù)據(jù)resize成VPU壓縮需要的尺寸,注意此處的resize與CAM->PL DDR通路中的resize相互獨(dú)立,即AI計算尺寸和VPU壓縮尺寸獨(dú)立配置。為了減少寫入PS DDR的數(shù)據(jù)量,這里將rgb565數(shù)據(jù)格式轉(zhuǎn)為yuv422(16bit),相比于rgba(32bit)格式,數(shù)據(jù)量可減少50%,而圖像色度分量完整保留,基本不影響圖像質(zhì)量。

每一路CAM數(shù)據(jù)均需要通過HP口寫入PS DDR,PS端共有4個HP口,有很多模塊會對它發(fā)起請求,因此工程中在BlockDesign中調(diào)用axi interconnect IP進(jìn)行仲裁。

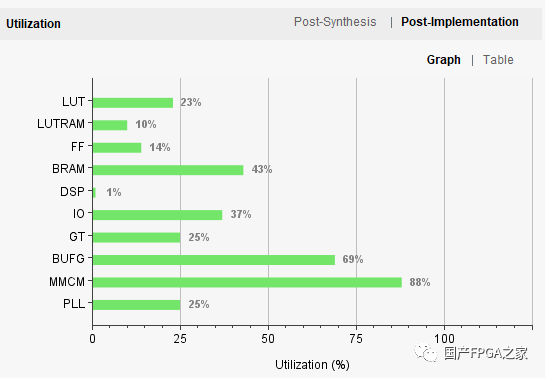

最終,實現(xiàn)的FPGA資源占用情況如下所示:

圖9 FPGA實現(xiàn)資源占用情況

3.42 軟件設(shè)計介紹

參考實現(xiàn)軟件整體流程可以歸結(jié)如下: 攝像頭輸入視頻數(shù)據(jù) > AI檢測 > AI結(jié)果繪制 > vpu編碼h264/h265視頻 > 輸出數(shù)據(jù)流

軟件中按功能將代碼封裝為多個模塊:攝像頭模塊、神經(jīng)網(wǎng)絡(luò)模塊、VPU模塊。則在實現(xiàn)一次完整數(shù)據(jù)流通路對應(yīng)的模塊調(diào)用為:攝像頭模塊取幀 > 神經(jīng)網(wǎng)絡(luò)模塊計算與后處理 > 攝像頭模塊得到圖像數(shù)據(jù) > vpu模塊壓縮 > vpu模塊輸出數(shù)據(jù)。

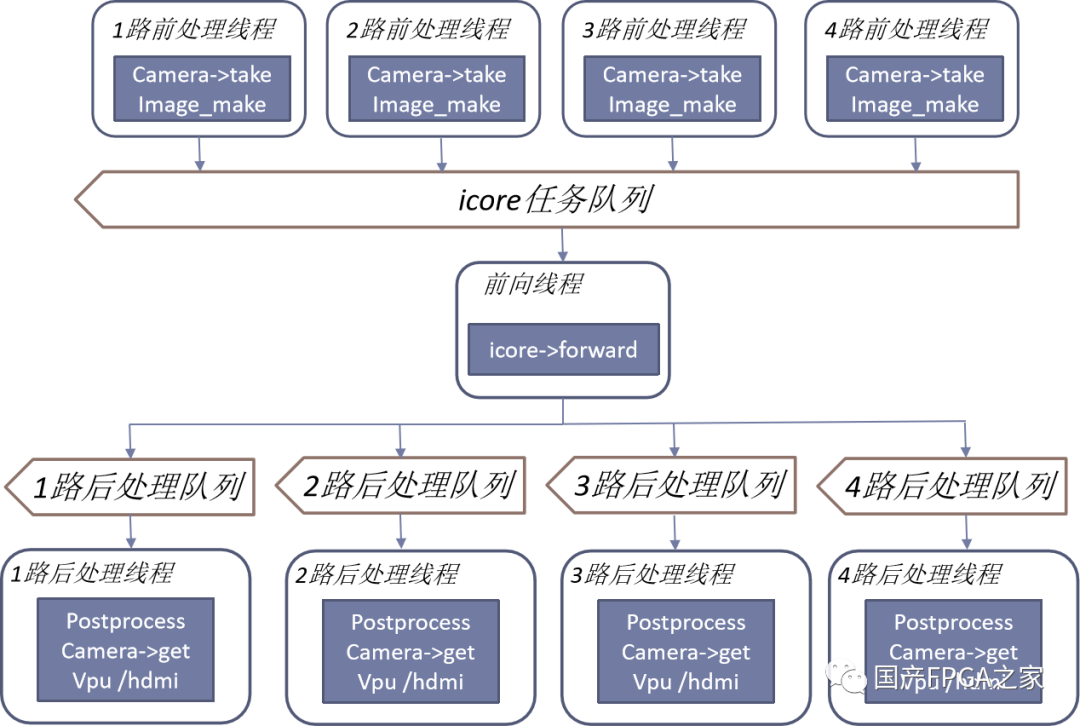

在AI調(diào)度過程中,采用了任務(wù)隊列的實現(xiàn)方式。主要參考了生產(chǎn)者消費(fèi)者設(shè)計模式,前處理、icore前向、后處理運(yùn)行在各自的線程中,互相之間通過任務(wù)隊列的方式通信。

對于多路的情況,則會使用多個前處理線程與多個后處理線程,以4路為例,4路不同的輸入圖像數(shù)據(jù)、icore推理結(jié)果會存放在ddr的不同位置,不同路之間數(shù)據(jù)不會相互干擾。任務(wù)隊列還提供了可以控制不同路是否做AI或者設(shè)置優(yōu)先級的功能。

圖10 軟件任務(wù)隊列調(diào)度框圖

具體的AI神經(jīng)網(wǎng)絡(luò)部署,基于icraft編譯器,直接編譯生成json和raw文件,就能夠更新參考設(shè)計的AI網(wǎng)絡(luò)部署。

3.52 實例結(jié)果介紹

性能:能夠穩(wěn)定完成4路1080p@30Hz視頻的AI檢測和視頻編碼。

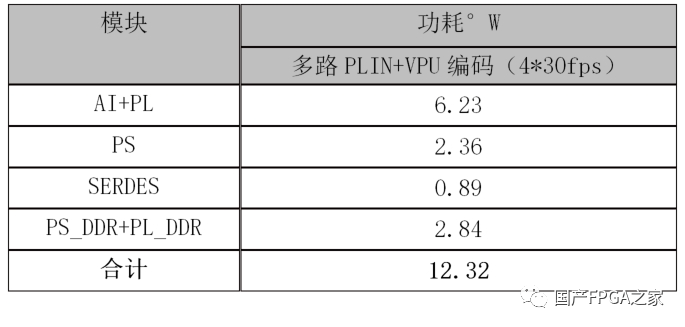

功耗:整體芯片功耗(含DDR)是12.32W。

表1 多路PL_IN+VPU編碼的功耗

4)小結(jié):海闊憑魚躍,天高任鳥飛

好了,經(jīng)過以上的參考設(shè)計實例的介紹,相信大家對FPAI芯片的系統(tǒng)方案以及參考設(shè)計有了更深層次的了解。

近幾年,邊緣端AI計算的市場份額逐年增長明顯,越來越多的落地應(yīng)用需求提出。“海闊憑魚躍,天高任鳥飛”,如何選擇一款A(yù)I芯片及系統(tǒng)方案,能夠滿足邊緣融合端的各種應(yīng)用場景,能夠適應(yīng)算法迭代的需求,能夠解決長尾算子的問題,形成高性能、低功耗、靈活可靠的產(chǎn)品?相信FPAI芯片及系統(tǒng)方案,會是一個不錯的選擇!

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19178瀏覽量

229200 -

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602004 -

soc

+關(guān)注

關(guān)注

38文章

4124瀏覽量

217964 -

編譯器

+關(guān)注

關(guān)注

1文章

1618瀏覽量

49057 -

GPU芯片

+關(guān)注

關(guān)注

1文章

303瀏覽量

5781

原文標(biāo)題:漫談FPAI芯片的AI系統(tǒng)方案

文章出處:【微信號:國產(chǎn)FPGA之家,微信公眾號:國產(chǎn)FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

談一談FPAI芯片的AI系統(tǒng)方案以及參考設(shè)計實例

談一談FPAI芯片的AI系統(tǒng)方案以及參考設(shè)計實例

評論