此次,我們將報道旨在實現光互連的光器件的最新研究和發展趨勢。

光學技術有望有助于實現可組合分解系統或大規模節點計算系統,從而促進 AI(人工智能)、ML(機器學習)和 HPC(高性能計算)的新趨勢。特別是,為了構建能夠經濟地安裝和運行具有與超級計算機相同數量的節點的系統的系統,需要光互連技術。

這次我們主要介紹以實現光互連為目的的光器件的學術會議報告。

在此之前,我想先講一個值得注意的消息。2023年10月,有消息稱英特爾將其光收發器業務出售給捷普公司。

我們相信,這意味著硅光子技術的轉變將真正開始。也就是說,“硅光子2.0”將如火如荼地進行。下面介紹的硅光子示例都是研發的一部分,將為硅光子2.0提供提示。

當考慮多通道化在AI/ML/HPC光互連的實際應用時,多陣列高集成技術是關鍵,VCSEL和半導體(Si和InP)光子集成電路(PIC)是我認為我們需要加強的。我們希望英特爾的最新舉措能夠加速和振興這一方向的研發。

高速串行數據多通道化和光互連

新的光學互連具有多通道高速串行數據。

xPU(CPU、GPU、TPU)等)正在被追求。當ASIC的工作時鐘頻率飽和時,適合提高性能的接口是高速串行。事實上,標準化 SiP 中小芯片之間接口的 UCIe(通用小芯片接口 Express)也使用串行信號的線束 (BoW) 中進行了定義。串行信號為16路多通道并行,在UCIe中已擴展至64路。

串行信號為32Gbit/s,與PCIe 5.0(BoW-512 for BoW)相同,并且其開發已經開始。未來,預計PCIe 6.0的速度將提高到64Gbit/s,PCIe 7.0的速度將提高到128Gbit/s,與CXL(Compute Express Link)類似。

現在,如何實現新型光互連所需的多通道化?最簡單的方案是使用與通道一樣多的光纖。

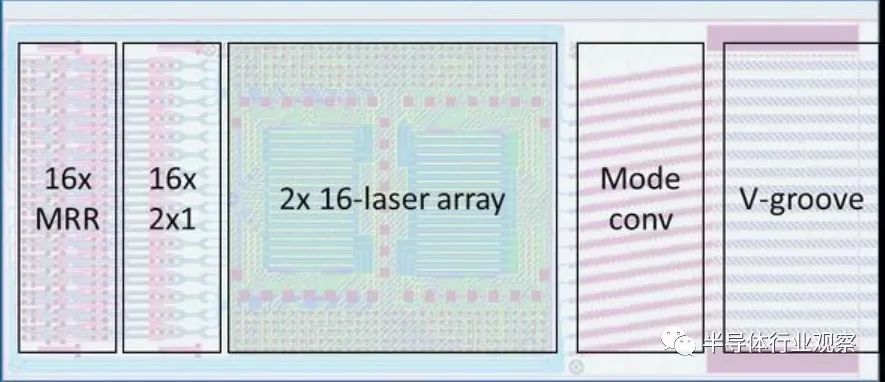

圖1是Intel 16通道PIC的布局圖。由于在實際芯片照片中很難看到波導,因此顯示了布局圖。

圖1 16通道硅光子芯片示例

圖中“V型槽”所示區域為光纖陣列的連接部分,其節距據認為為250μm,與光纖陣列相匹配。調制器(微環諧振器:MRR,稍后描述)、模式轉換元件(Mode conv)等都是為了匹配這個間距而設計的,并且32個冗余激光區域也布置在這個寬度內。我可以看到該設計最大限度地減少了海岸線(海灘)密度(Gbit/mm),這是光學互連中的一個重要參數。

為了避免增加芯片的寬度,電極焊盤將放置在內部而不是外圍,建議采用倒裝芯片或背負式安裝。獨創性可見一斑,例如連接高速電子IC (EIC) 和PIC 芯片的調制器周圍的小焊盤,以及用于控制大電流激光器的大焊盤。假設V形槽間距為250μm,則芯片寬度可估計為約5mm。雖然只是Tx,但海岸線密度為100Gbit/s×16÷5mm = 320Gbit/s/mm。

這樣,光互連不僅具有高速度和傳輸距離,而且還具有重量輕、光纖陣列間距僅為高速細同軸線(例如1.27毫米)的幾分之一的優勢。這對于機箱內的光纖布線也是有利的。

典型的光纖陣列是基于為公共通信網絡開發的250μm間距12芯光纖陣列,標準是相應的MPO連接器。因此,它與使用2的冪構建系統的計算機應用不兼容,并且已經采取了對策,例如使用12個核中的8個。

為此,最近開發了16 光纖陣列和將其連接在一起的光連接器。此外,有許多建議縮小光纖陣列間距以增加布線密度。還開發了一種光纖陣列,它使用相同的纖芯和包層直徑,但光纖涂層更薄,節距為 200 μm。此外,還出現了一種可以同時連接 16 根光纖陣列的緊湊型光連接器,這似乎與此兼容。還提出了具有較小纖芯和包層直徑的光纖和光纖陣列。新光纖的引入需要仔細考慮,包括與已安裝的大量光纖和光連接器的兼容性。然而,它在后端網絡這個新領域的應用可能會很快。

多通道和光復用技術

在光通信中,有一種技術叫做“波長復用技術”,可以通過一根光纖傳輸多個不同波長的信號。CWDM-4方法從被稱為路線波分復用(CWDM)的世界標準波長中選擇四個波長,在40G及以后的SMF(單模光纖)光模塊中擁有最大的市場份額。利用這一點,用傳輸4芯CWDM-4的光纖陣列可以實現16個通道,用16芯CWDM-4可以實現64個通道。

這樣,波長復用作為多通道的方法是有前途的。CW WDM MSA 的成立也是為了定義新的波長標準,著眼于進一步的多通道化[8]。定義了最多 32 個波長復用,并于 2021 年 6 月發布了規范 1.0。增加波長數量可以增加容量,但需要解決波長穩定性等技術問題、不同波長的庫存管理等制造問題以及增加波長數量帶來的成本問題。

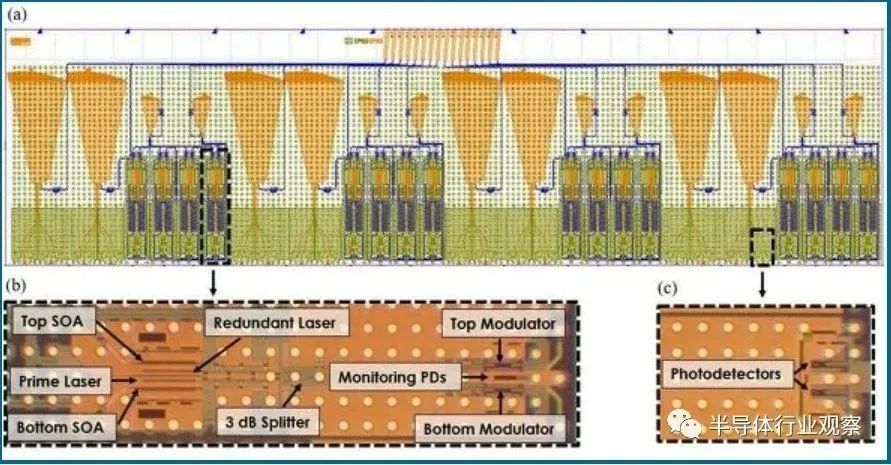

圖 2顯示了 32 通道硅光子收發器芯片,該芯片使用 8 芯光纖陣列以每波長 100 Gbit/s 的速度傳輸 CWDM-4(以太網 400GBASE-FR-4)。由 Skorpions 開發。上半部分是布局圖,下半部分是芯片照片。扇形部分是CWDM-4波長復用/解復用電路。大風扇是接收波長解復用電路,小風扇是發送波長復用電路。有4組不同波長的發射/接收電路(圖2底部照片中為一組)和8組波長復用/解復用電路,以約460 um的間距排列,芯片寬度為30.1毫米。海岸線密度為3200Gbit/s÷30.1mm=106Gbit/s/mm,二段為212Gbit/s/mm。

圖2 Skorpions的32通道(8光纖x 4波長復用)收發器硅光子芯片

演示中表明,通過改變發送器/接收器電路和 CWDM-4 解復用器的布局,可以將芯片寬度增加到 19.2mm。雖然寬度會減少,但長度會增加約1mm。此時的海岸線密度為167Gbit/s/mm,分兩段提升至333Gbit/s/mm。

順便說一句,雖然這是標稱值,但該芯片的能源效率為 2.1pJ/bit。然而,每個傳輸塊中的片上激光器和光放大器占據了大部分功率,為 1.8 pJ/bit,并且存在一些可以看到的問題。

增加密度的另一種方法是使用微環諧振器 (MRR) 作為波長選擇性調制器和接收濾波器。AyarLabs 很有名(據報道得到 DARPA CHIPS、DARPA PIPES 和 ARPA-E 的支持)。

顧名思義,圖 1 所示的 MRR 是光波長(頻率)級別的環形諧振器。當MRR和光波導光學耦合時,當穿過光波導的光的波長與諧振波長匹配時,MRR吸收該光。由于MRR的諧振波長可以通過電信號改變,因此可以通過將諧振波長與通過的光的波長對齊(光信號關閉,因為MRR吸收光)或將其移除(光信號開啟)來進行調制。到。接收時,MRR和光波導進行光耦合,將MRR設置為在通過的光(接收光)的特定波長下諧振,并且該波長的通過的光被吸收并進行光電轉換以獲得電信號。

圖 3顯示了[10]中描述的 AyarLabs 方法的原理圖。右側的片外激光器輸入五種不同波長的復用光。在發射器中,對應于五個波長的 MRR 在單個波導中串聯排列。每個 MRR 均設計用于諧振調制五個輸入波長之一,而其他波長不受影響。類似地,對于接收,五個 MRR 串聯排列在一個波導上。它只吸收各個諧振波長的光信號(其他波長通過),進行光電轉換,獲得電信號。

該方法的優點是MRR的尺寸較小,直徑為10μm,通過將它們串聯排列,可以大大提高集成密度(相比于其他方法的數百微米)。

圖3 使用AyarLabs MRR的收發器原理圖

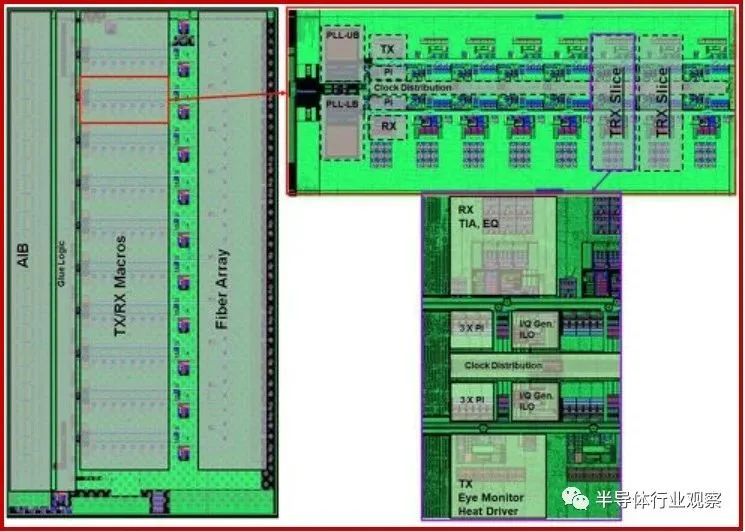

圖 4顯示了 AyarLabs 使用該技術的 80 通道收發器芯片。該芯片有10個塊,每個塊可以使用8波長MRR發送和接收8個波長復用通道,并連接到單根光纖。此外,用于傳輸和接收的電子電路(包括接口)也集成在同一芯片上。由于每根光纖256 Gbit/s,每通道32 Gbit/s,因此該芯片的傳輸容量為2.56 Tbit/s。

圖4 AyarLabs 64通道(8光纖x 8波長復用)收發器硅光子芯片照片

據報道,芯片寬度為8.86mm,芯片岸線密度為289Gbit/s/mm,二分部為578Gbit/s/mm。最新網站顯示光纖數量為8根,海岸線密度為228Gbit/s/mm。此外,據報道能量效率<5pJ/bit,但尚不清楚是否包括片外激光器的功耗。

該方法作為增加海岸線密度的方法而受到關注,但由于與諧振相關的主要問題,例如諧振波長的溫度依賴性、制造變化以及諧振波長周圍的頻帶減小,該方法繼續受到挑戰。

新選擇:多芯光纖

執行復用以增加光傳輸的容量。它們是時分復用(串行化)、波長復用(CWDM、CW WDM)和空間復用。使用多芯光纖(MCF)的空間復用最近成為一個熱門話題。通過在單根細光纖中嵌入多芯(Multi-Core),每根光纖的傳輸容量可提高N倍。在這種情況下,利用了將光信號限制在纖芯中并減少串擾的能力。在典型示例中,芯直徑為9μm,芯之間的距離為30至40μm。

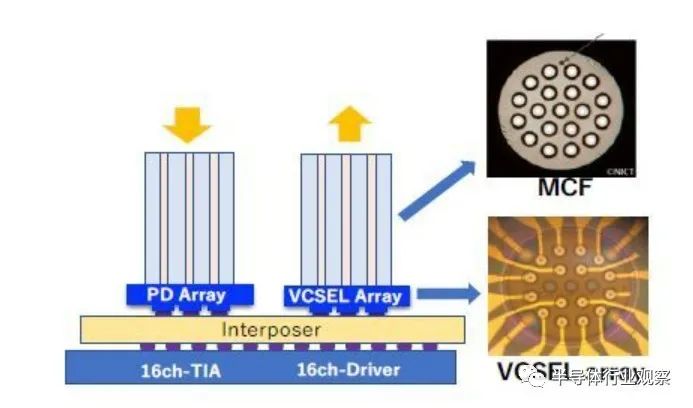

使用MCF的16通道光傳輸已成為熱門話題[11]。這是由東京工業大學小山實驗室領導、日本國立信息通信技術研究所(NICT)委托進行的研究成果。

概述如圖 5所示。我們使用 16 芯光纖 (MCF),其中有 19 個單模芯。信號通過光學耦合到集成了每個位置對應的16個VCSEL和PD的二維陣列芯片,并傳輸數據。VCSEL使用InGaAs QW(量子阱)作為有源層,具有金屬孔徑(MA)結構,并以1060 nm的振蕩波長從背面發射光。發射的光為單模,模直徑約為5um。它耦合到單模芯(簡正模直徑 9um),無需透鏡。接收側也是背照式 InGaAs PD 的二維陣列,與光纖直接進行光耦合。

圖5 使用MCF的16通道光互連

此外,如圖所示,光學元件安裝在中介層的一側,驅動器等IC安裝在另一側,實現了高密度布線。這實現了 25Gbit/s x 16 通道和 400Gbit/s。海岸線密度很難評估。如果觀察至少一根光纖(從照片來看,包層直徑約為 200-250um),考慮到涂層,該值將從幾百 GB/s/mm 到接近 1Tbit/s/mm材料。在此方法中,海岸線密度由內置 IC 和安裝結構的寬度決定。

對于實際應用,仍然存在許多問題,包括適用于光學互連的 MCF 的標準化,例如纖芯截止波長、VCSEL 與纖芯之間的模式匹配以及高度可靠的薄型結構。盡管如此,它作為一種新的多通道系統仍然引起了人們的關注。

多通道化和光學器件總結

如上所述,能夠實現16個以上的多通道數的裝置的開發正在變得活躍。關于硅光子學的公告已經很多,但我認為 VCSEL 也有機會,它可以很容易地制成一維或二維陣列。

硅光子學可以利用硬硅襯底和穩定的集成工藝,使其適合多通道應用。目前量產的Mach-Zehnder調制器的實用頻段據稱為35G至40GHz,而且調制段長且限制為100Gbit/s PAM-4(50GBaud),不適合更高速的信號. 據說 Intel和AyarLabs推出的MRR調制器預計將具有優越的性能,但在將每個MRR的諧振波長與傳輸光信號的波長匹配的技術上存在一個主要問題。

另一方面,引起關注的是異質硅光子學,它集成了由硅以外的電光材料制成的高速調制器。集成方法有多種,但均采用適合高速光調制的材料和芯片。此次推出的Skorpios在Si襯底上的Si光子學上集成了InP高速EA(電吸收)調制器。此外,還有許多關于使用EO-聚合物、LN(氮化鋰)、BTO(鈦酸鋇)和PLZT(鈦酸鉛鑭鋯)等電光材料的>100GBaud高速調制器的會議演示。盡管實際應用存在問題,但我們正在密切關注。特別是,我們希望看到有關適合大規模生產的器件結構、材料和工藝的討論,這些器件結構、材料和工藝可以與允許微加工的 CMOS 工藝共存。

傳統的 GaAs 基 VCSEL 具有 850nm 多模振蕩(發光),并且已經發布了能夠以 100Gbit/s PAM-4 傳輸 100m MMF 的產品。相比之下,東京工業大學在此推出的基于InGaAs的VCSEL具有波長為1060 nm的單模振蕩,并且具有更高速度和更遠距離的潛力。另外,有報道稱,與MCF結合可以在單根光纖上傳輸16個通道。雖然挑戰很多,但這是一項有潛力的技術,我對它寄予厚望。

上面,我們介紹了針對多通道光互連的光學器件。我很高興看到未來各機構的研發將更加積極地走向實際應用。

文章來源:半導體行業觀察

審核編輯:湯梓紅

-

gpu

+關注

關注

28文章

4703瀏覽量

128723 -

人工智能

+關注

關注

1791文章

46896瀏覽量

237658 -

光器件

+關注

關注

9文章

94瀏覽量

15750 -

光學技術

+關注

關注

0文章

48瀏覽量

9682

原文標題:光器件最新研究和發展趨勢

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

光器件的最新研究和發展趨勢

光器件的最新研究和發展趨勢

評論