PCB(Printed Circuit Board)是電子設備中的重要組成部分,用于連接和支持電子元件。走線是將電子元件之間的電路連接起來的過程。在PCB設計中,過長的走線可能會導致一些問題,包括以下幾點:

*信號衰減:電路中的信號在傳輸過程中會受到衰減,過長的走線會增加信號衰減的可能性。信號衰減可能導致信號失真、噪聲增加和通信錯誤。尤其是對于高頻信號和快速信號傳輸,過長的走線會更加明顯地引起問題

*信號延遲:電路中的信號傳播需要一定的時間,過長的走線會增加信號傳播的延遲。在一些應用中,如高速通信和時序敏感的電路,信號延遲可能會導致系統性能下降或功能失效。

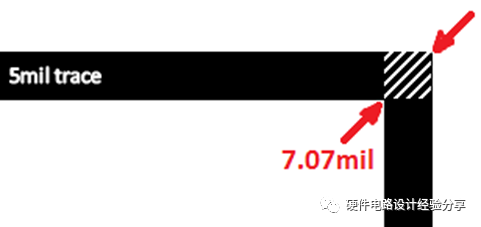

*串擾干擾:過長的走線會增加電路之間的串擾干擾的可能性。串擾干擾是指一個信號線上的信號對其他信號線產生的干擾。當走線過長時,信號線之間的電磁相互作用可能會導致信號的串擾,從而引入錯誤或干擾。

*PCB布局困難:過長的走線可能導致布局上的困難。PCB布局時需要考慮信號的路徑、電源和地線的分布、元件的布置等因素。如果走線過長,可能會增加布局的復雜性,使得設計更加困難。

因此,在PCB設計中,通常需要盡量控制走線的長度,以確保信號的可靠傳輸和系統的性能。這可以通過合理的電路布局、信號線的路徑規劃、使用適當的層間連接等方法來實現。

PCB走線太長,最終綜合的寄生電容會增加

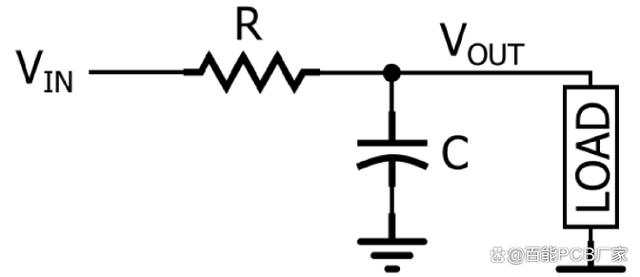

不用到微觀層面去分析。我們根據電容的定義就知道:兩個間距保持不變的平面,面積越大,電容值越大。所以走線越長,則會導致綜合的對地容性會持續增大。電容的容值越大,則相當于低通濾波器,會衰減掉高頻分量。

我們不需要到微觀層面去分析,就知道走線太長,在接收端肯定影響高頻分量。

當PCB走線過長時,寄生的電容會變大。這是因為走線的長度增加會增加電路元件之間的物理距離,進而導致電容的增加。以下是導致寄生電容增加的幾個主要因素:

走線長度增加:走線的長度是電容值的一個關鍵因素。根據電容的定義,電容值與電場中的電場強度以及物體之間的距離成正比。當走線的長度增加時,物體之間的距離增加,導致電容值增加。

走線寬度和厚度:走線的寬度和厚度也會對寄生電容產生影響。通常情況下,走線寬度越大,走線之間的電場強度就越小,從而減小了電容值。而走線的厚度增加則會導致電容值增加,因為走線厚度的增加會增加走線的表面積,從而增加了電容的效果。

周圍環境和臨近走線:寄生電容的大小還與周圍環境和臨近走線的位置有關。當走線過長時,與其他走線之間的距離可能變得更近,這會導致臨近走線之間的電容增加。此外,周圍環境中的其他導體或地平面也會對走線之間的電容產生影響。

需要注意的是,寄生電容的增加可能會對電路的性能產生負面影響。它可以影響信號的傳輸速度、引入干擾和串擾等問題。因此,在PCB設計中,需要合理規劃走線長度和布局,以控制寄生電容的大小,確保電路的可靠性和性能。

PCB走線太長,最終綜合的寄生電感會增加

當PCB走線過長時,寄生的電感會變大。這是因為走線的長度增加會增加電路元件之間的物理距離,進而導致電感的增加。以下是導致寄生電感增加的幾個主要因素:

走線長度增加:根據電感的定義,電感值與電路中的線圈(走線)長度成正比。當走線的長度增加時,線圈的長度也增加,導致電感值增加。

走線寬度和厚度:走線的寬度和厚度對寄生電感也有一定影響。較寬的走線和較厚的走線會減小走線的電感值,因為它們提供了更多的導體表面積和截面積,從而減少了線圈的長度。

走線形狀和布局:走線的形狀和布局也會影響寄生電感。例如,蜿蜒曲折、盤繞或環繞式的走線形狀會增加走線的電感值。此外,如果走線與其他走線或導體之間存在臨近或相互耦合,也會增加走線的寄生電感。

寄生電感的增加可能對電路產生負面影響。它可以導致信號傳輸速度減慢、引入串擾、降低電路的帶寬等問題。因此,在PCB設計中,需要合理規劃走線長度、寬度和布局,以控制寄生電感的大小,確保電路的可靠性和性能。

PCB走線太長,增加寄生電阻

這個按照電阻的定義就想得通,此處不做解釋。

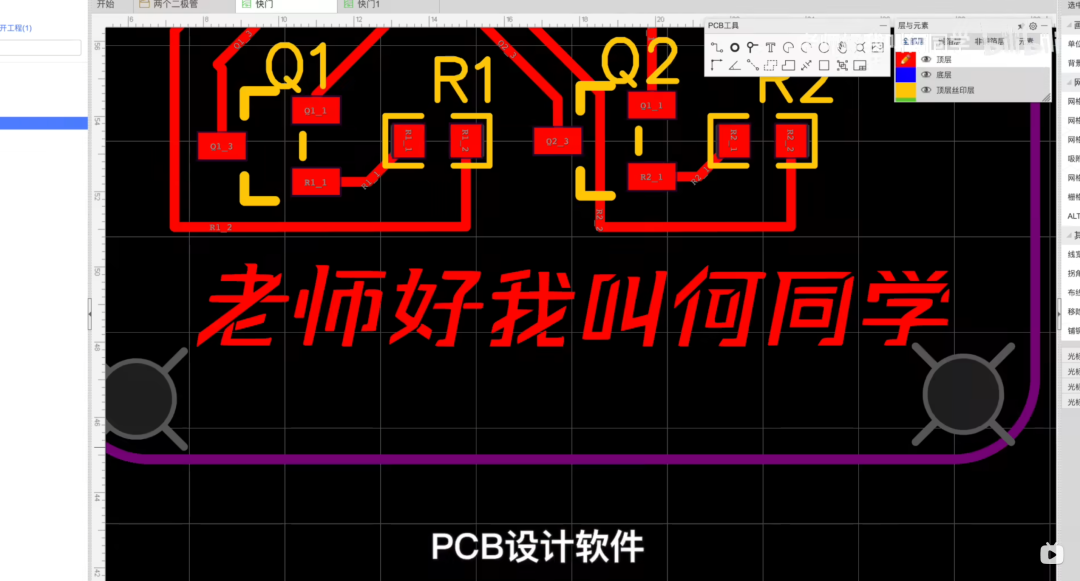

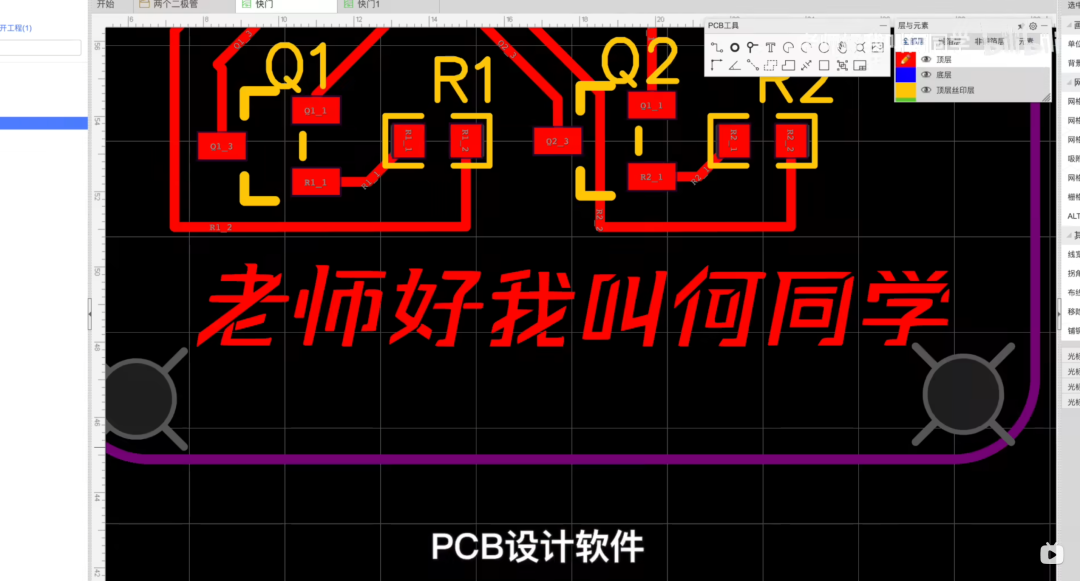

通過布局優化走線長度

在設計中,布局是一個重要的環節。布局結果的好壞將直接影響布線的效果,因此可以這樣認為,合理的布局是PCB 設計成功的第一步。簡單的理解,PCB布局就是把所有的元器件按照功能結構、模塊化、滿足DXF的要求、滿足順暢布局、布線等原則進行。

考慮整體美觀,一個產品的成功與否,一是要注重內在質量,二是兼顧整體的美觀,兩者都較完美才能認為該產品是成功的。在一個PCB 板上,組件的布局要求要均衡,疏密有序,不能頭重腳輕或一頭沉。

合理的布局,才能優化整理的走線最短路徑。布局不合理,就會導致不必要的走線長度。

**我們把還沒連接的PCB,用細線表示連接關系的線,叫做鼠線,又叫飛線。鼠線指兩點間表示連接關系的線。如你在原理圖上設定的兩個焊盤之間有連接關系,那么導入LAYOUT后就會在兩個焊盤間生成一根鼠線以指導你布線。

**

鼠線也是幫助你初步判斷會不會走得太繞線。所以,這種樸素的知識也就是人人都知道:一個器件布下去之前,轉幾個90°,看看怎樣走線最短。

例如一些大型的處理器的電源管腳的分布,是考慮到你的走線的。所以你在設計電源模塊的擺放的時候,也要考慮各個大電流電源供電走線不要交叉。所以一開始就要規劃好,電源怎么供電、時鐘怎么布放、接口怎么出,其實除了為了布局階段“布進去”,還為了布線階段“走得順”。

既然PCB走線要走得短減少寄生參數,為什么會有“蛇形走線”

蛇形走線最主要是為了保證電路時序約束的正確。數字電路中高低電平相互翻轉的時候是需要時間的,為了保證在接受端電平能被正確的采樣,通常會預留一點時間給信號電平建立起來,同樣,正確的采樣也需要一點時間,就需要信號翻轉到某個電平后保持一段時間。

這就是所謂的建立時間(setup time)和保持時間(hold time)。

建立時間、保持時間模型展現;建立時間余量、保持時間余量的計算;以及系統允許時鐘頻率的最大頻率計算。

建立時間(Tsu):在時鐘采樣沿之前,數據必須保持穩定的時間,該時間量稱為建立時間。

保持時間(Th):在時鐘采樣沿之后,數據必須保持穩定的最短時間。

理想最優的建立時間和保持時間出現在數據中間采樣的位置,如下所示,實質就是使觸發器在采樣沿得到穩定的數據,如果數據在時鐘上升沿的建立保持時間內{latch edge-setup,latch edge+hold time}發生跳變,則會產生亞穩態輸出,即輸出值在短時間內處于不確定態,有可能是1,有可能是0,也可能什么都不是,處于中間態。

在現在的高速數字設計中,其實串行總線的接口已經大行其道了。在我們剛工作的階段,其實還是大量的并行總線在大量使用:包括DDR、PCI、LPC、LocalBus,這些并行的接口需要時鐘去采樣數據,基本原理就是大家數字電路去學習的“D觸發器”。

所以,現在還在用"蛇形走線"繞等長來滿足建立保持時間的設計主要應用于DDR相關的設計。大量的并行接口已經被PCIe、USB、SATA……這樣的串行總線代替了。所以在高速數字設計上,大家非常關注“眼圖”。

-

低通濾波器

+關注

關注

14文章

473瀏覽量

47341 -

PCB設計

+關注

關注

394文章

4671瀏覽量

85319 -

寄生電容

+關注

關注

1文章

291瀏覽量

19195 -

PCB走線

+關注

關注

3文章

133瀏覽量

13903 -

信號衰減

+關注

關注

0文章

57瀏覽量

8922

發布評論請先 登錄

相關推薦

PCB走線為什么不能太長?線間距為什么不能太近?

PCB走線為什么不能太長?線間距為什么不能太近?

評論