數(shù)字脈沖升級功能

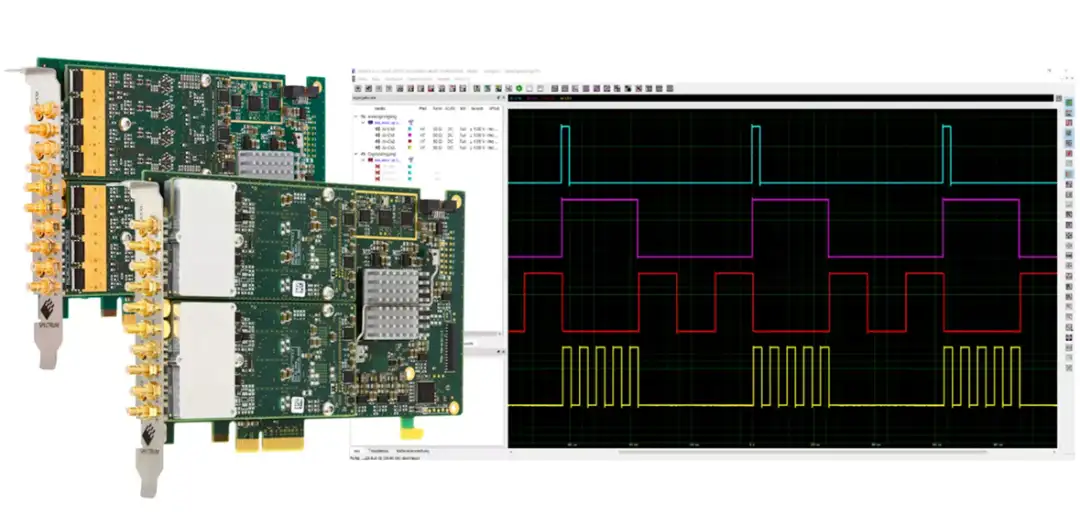

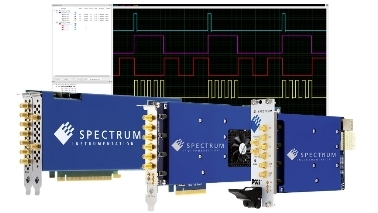

德思特Spectrum系列全部在售數(shù)字化儀和AWG產(chǎn)品(包括TS-M2p,TS-M4i,TS-DN2,TS-DN6型號產(chǎn)品),發(fā)布了新增的數(shù)字脈沖(DPG)升級功能,于11月15日正式推出。用戶購買后,可自行通過對產(chǎn)品內(nèi)置FPGA進行固件升級獲取相關(guān)功能,無需返廠。該功能可以為原本的數(shù)字化儀或AWG產(chǎn)品增加3~4個獨立的數(shù)字脈沖發(fā)生器通道,幫助用戶實現(xiàn)測試系統(tǒng)中的一系列控制功能,為客戶的產(chǎn)品升級和系統(tǒng)擴建提供了一種較低成本的選項。

數(shù)字脈沖發(fā)生器技術(shù)淺析

#01 數(shù)字脈沖發(fā)生器是什么

數(shù)字脈沖發(fā)生器(Digital Pulse Generator, DPG),DPG的主要功能是產(chǎn)生可編程的數(shù)字脈沖信號,可以通過控制其頻率、占空比、上升時間、下降時間等參數(shù)來模擬各種不同的數(shù)字信號,從而滿足不同應(yīng)用場景的需求。通常情況下,DPG的輸出信號可以直接接入DUT或進行測試和分析。

#02 DPG可以干什么?

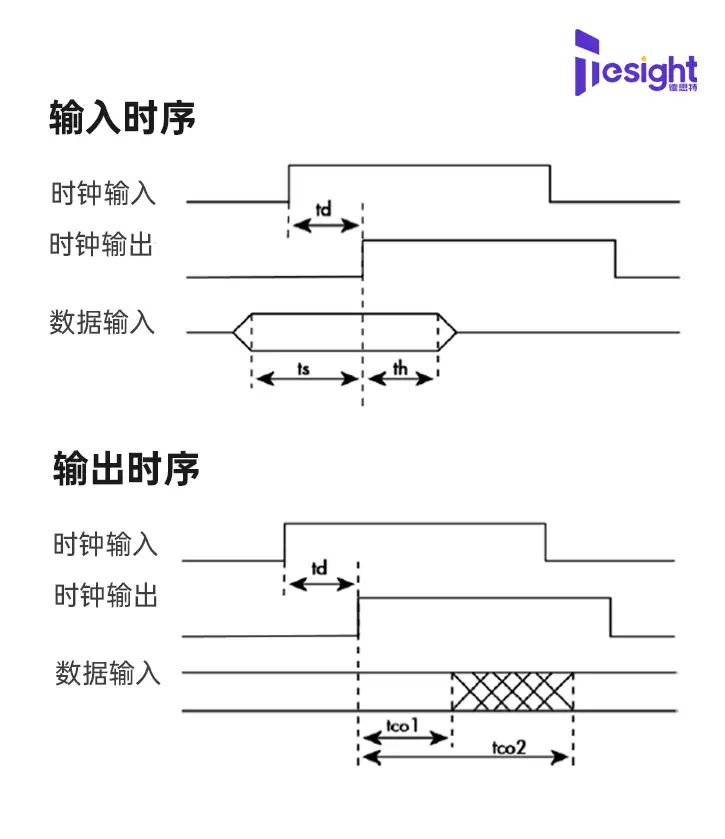

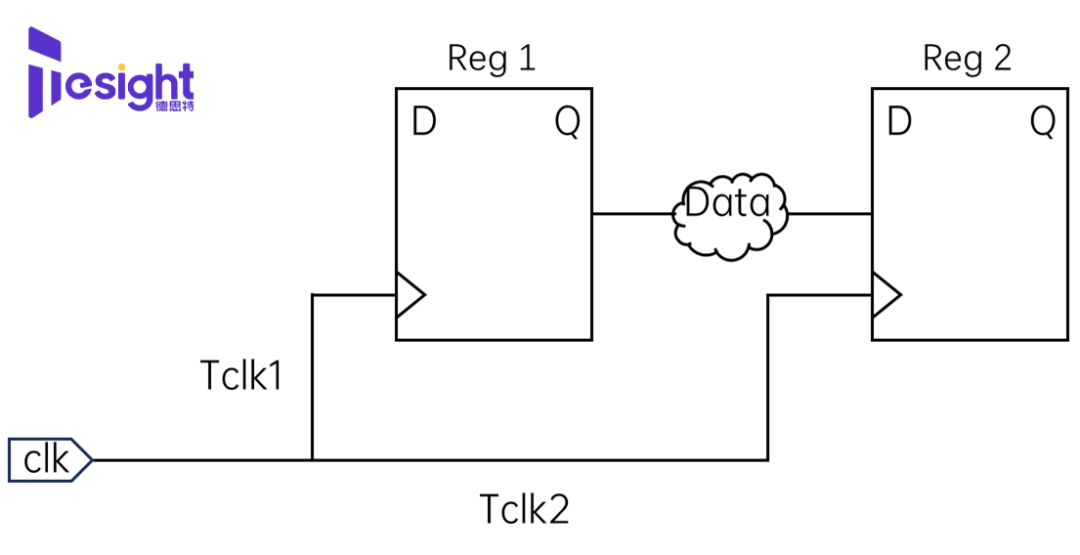

● 時序測試:DPG可以產(chǎn)生各種不同頻率、占空比、上升/下降時間等參數(shù)可編程的數(shù)字脈沖信號,可以用于測試各種電子設(shè)備和系統(tǒng)的時序特性,如芯片、接口、總線、存儲器等。比如,常見的時序頻率測試,精確可編程的時鐘信號輸入到待測器件中,可以評估不同時鐘頻率下的器件性能表現(xiàn),通過調(diào)節(jié)時鐘頻率確定器件設(shè)備的最大工作頻率。

● 對外觸發(fā)控制:對于部分外部儀器或邏輯器件,需要有簡單的時鐘或復(fù)位信號進行觸發(fā)或驅(qū)動,才能正常輸出我們想測試的信號。加入DPG功能后,我們就能通過簡單的設(shè)置,在不增加額外儀器的情況下,完成這個觸發(fā),在降低測試系統(tǒng)的復(fù)雜度和成本同時,不用為觸發(fā)信號和采集卡之間的同步協(xié)調(diào)問題而煩惱。

德思特數(shù)字脈沖發(fā)生器解決方案

德思特數(shù)字脈沖發(fā)生器(DPG)功能都是通過PCIe卡、LXI或以太網(wǎng)儀器的板載FPGA實現(xiàn)的,德思特所有任意波形發(fā)生器板卡(AWG)系列都可以升級搭載DPG功能模塊。

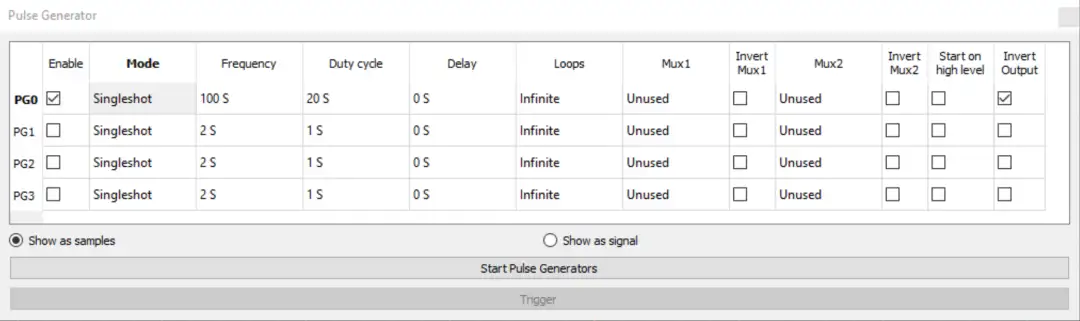

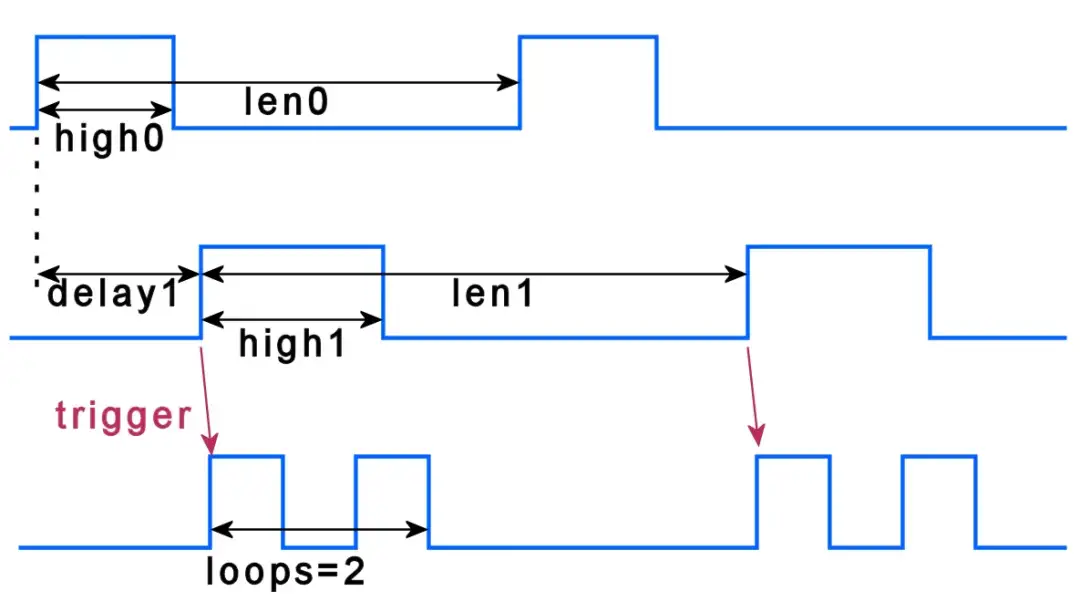

德思特AWG卡增加了4個內(nèi)部獨立的數(shù)字脈沖發(fā)生器,具有可編程占空比、輸出頻率、延遲和循環(huán)數(shù)量。這些脈沖發(fā)生器可以通過軟件、硬件觸發(fā)器觸發(fā),也可以相互觸發(fā),從而形成復(fù)雜的數(shù)字脈沖方案來驅(qū)動外部設(shè)備或測試實驗。

德思特DPG模塊在卡的采集/重放功能與外部設(shè)備之間,提供通用的定時同步接口。DPG模塊由四個脈沖發(fā)生器組成,每個發(fā)生器允許(獨立)獨立地生成單獨的脈沖、脈沖串或連續(xù)的脈沖流,這些脈沖可以在多用途I/O線上輸出,從而大大增強了模塊的功能性。

● 至多四個脈沖發(fā)生器可供配置

● 單次、多次重復(fù)或連續(xù)/無限重復(fù)脈沖

● 脈沖長度/占空比的單獨控制

● 每個脈沖發(fā)生器單獨進行外部或內(nèi)部觸發(fā)/啟動

● 每個脈沖發(fā)生器都有單獨的觸發(fā)延遲,允許相移

● 通過將脈沖發(fā)生器內(nèi)部級聯(lián),可實現(xiàn)多達4倍觸發(fā)時鐘倍頻

● 二次開發(fā)SDK同步更新相關(guān)功能API,支持語言包括C/C++, C#, Python, VB.NET, LabVIEW, MATLAB等

-

FPGA

+關(guān)注

關(guān)注

1620文章

21511瀏覽量

599021 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1351瀏覽量

61456 -

脈沖發(fā)生器

+關(guān)注

關(guān)注

5文章

173瀏覽量

34067 -

數(shù)字化儀

+關(guān)注

關(guān)注

0文章

137瀏覽量

17847 -

任意波形發(fā)生器

+關(guān)注

關(guān)注

0文章

127瀏覽量

15695

發(fā)布評論請先 登錄

相關(guān)推薦

工業(yè)數(shù)字化平臺有什么功能

什么是AWG?AWG和其他信號發(fā)生器的差別

數(shù)字信號發(fā)生器怎么調(diào)有效值

數(shù)字序列信號發(fā)生器如何測量

脈沖信號發(fā)生器的主要功能和作用

Spectrum儀器推出hybridNETBOX,集多通道AWG與數(shù)字化儀于一體

任意波形發(fā)生器與示波器的雙通道有什么區(qū)別

淺談任意波形發(fā)生器及通道合并功能

信號發(fā)生器如何發(fā)出雙脈沖?

Spectrum儀器旗下數(shù)字化儀和任意波形發(fā)生器新增數(shù)字脈沖發(fā)生器功能

高速數(shù)字化儀和AWG在車輛總線(CAN/LIN/PSI5)測試中的應(yīng)用(二)

脈沖發(fā)生器助力雷達系統(tǒng)開發(fā)的關(guān)鍵應(yīng)用

增加3~4個獨立數(shù)字脈沖發(fā)生器通道!數(shù)字化儀和AWG新增DPG功能

增加3~4個獨立數(shù)字脈沖發(fā)生器通道!數(shù)字化儀和AWG新增DPG功能

評論