芯片的功耗主要分為靜態功耗和動態功耗

一、靜態功耗

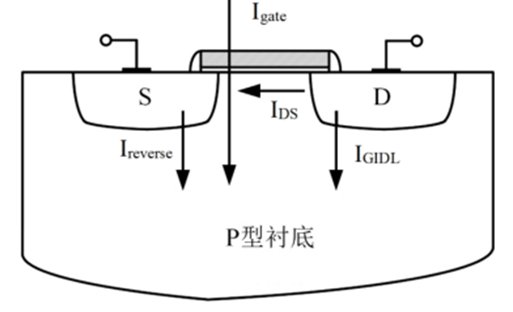

靜態功耗(漏電功耗)是指芯片待機狀態下所產生的的功率消耗,來源于MOS管內部的泄漏電流;泄漏電流有多個組成部分:

? (1)亞閾值泄漏電流,IDS

? (2)柵氧化層隧穿電流,Igate

? (3)反偏二極管電流,Ireverse

? (4)漏極泄漏電流,IGIDL

因此總的漏電流:

Ileakage = IDS + Igate +Ireverse + IGIDL

Pleakage = Ileakage * VDD

二、動態功耗

動態功耗指的是由于MOS管狀態跳變所產生的的功耗;動態功耗又分為開關功耗和短路功耗;

1.開關功耗

開關功耗是由于邏輯門翻轉時對電容充放電所產生的的功耗;

以一個反相器為例,當輸入信號從高電平變為低電平,電源VDD通過PMOS對輸出電容(C L )充電;

輸出電容包括三個部分:門自身的輸出節點電容C drain 、總的互聯線電容C interconnect 、被驅動門的輸入電容C input ;

? (1)這個過程從電源抽取的能量計算如下:iVDD和Vout是隨時間變化的,在dt的時間范圍內,

由于Vout達不到VDD,因此將CL充電至VDD需要無窮大的時間,充電過程的消耗的總能量為:

? (2)對于電容CL來說,在dt的時間范圍內,其消耗的能量為:

在這個過程中,電容CL消耗的總能量為:

由(1)(2)可以看出,電源在一個充放電周期(放電過程中不消耗電源能量)中提供的總能量為C L *VDD ^2^ ;其中一半以熱的形式在充電過程中被消耗在PMOS上,另一半儲存在電容CL中;儲存在電容CL中另一半在放電過程中被NMOS消耗掉;

如果反相器每秒開關favg次,則功耗為:Pavg,sw = EVDD / T = C L *VDD ^2^ *favg

其中T為周期,favg為開關頻率;

1> 引入節點轉換因子α T ,代表單位時鐘周期內邏輯門的翻轉概率,因此實際的開關頻率favg低于時鐘頻率f CLK ,favg = α T *fCLK

考慮到電源網絡的IR drop,邏輯門的電源Vi實際上要小于電源VDD 因此,功耗的公式改寫為:

Pavg,sw = (α T *C L *V i )VDDfCLK

每次充電或放電一次,動態功耗P dynamic,sw :

Pdynamic,sw = 0.5 Pavg,sw = 0.5 (α T *CLV i )VDDfCLK ~= 0.5α T *f CLK *C L *VDD^2^

2.短路功耗

上面的討論中,輸入信號上升和下降時間為0,當輸入信號存在slew時,存在短時間內PMOS和NMOS同時導通的過渡區,從VDD到VSS形成直流通路,從而產生的能量損耗P sc ;

如下圖所示,NMOS在Vin > VTnmos后開始導通;而PMOS在電壓達到VDD – VTpmos之前一直導通,在這段時間內PMOS和NMOS同時導通;

常用三角形脈沖模擬電流隨時間的變化,每經過一個開關周期0 -1 -0所消耗的能量為:

Esc = Escr + E scf ,其中Esc和Escf分別為輸入信號上升和下降期間的由短路電流所消耗的能量;消耗的能量就等于i(t)曲線下的面積和VDD的乘積;

因此, Escr = Escf = 0.5*VDD *I peak *tsc

總能量 Escr = VDD* I peak * tsc

一個周期內的平均功耗為Psc = E sc /T =E sc *f = VDD * I peak *t sc *f = C sc *VDD ^2^ *f

其中,Csc為過渡區等效電容;f為輸入信號Vin的電平跳變頻率;

3.internal power與總功耗

由上述討論可知,

Ptoal = Pleakage + Pdynamic = Pleakage + (Pdynamic,sw + P sc )

在實際應用中將開關功耗分為器件功耗和網線負載功耗兩部分:

Ptoal = Pdevice + Pnet

(1) Pnet為在網線上消耗的功率;對于電容的充放電,實際上只有半個周期會消耗功率,取節點轉換因子αT為0.5,因此:

Pnet = 0.5* CL *VDD ^2^ *Tnet

其中CL為三部分組成的電容;Tnet為net的翻轉率;

在net上消耗的只有動態開關功耗;

(2)其中 Pdevice = Pleakage + Pinternal

其中,Pinternal 包括動態開關功耗Pdynamic,sw的一部分和全部的P sc ;

器件的動態功耗包括短路功耗和動態開關功耗兩部分;

因此,Ptoal = Pleakage + Pinternal + Pswitch

(這里用Pswitch替代P net ,switch power是更通用的說法)

Pinternal 包括動態開關功耗Pdynamic,sw的一部分和全部的Psc

上面的解釋來自《數字集成電路物理設計》,個人理解這句話是沒有問題的,但是此時Pnet中的CL就不是三部分組成的電容了;

見下圖(liberty ug): 如果lib中output pin上沒有capacitance,那么由output pin capacitance帶來的影響已經被考慮到internal power中了;

因此,可以將internal power理解為發生在cell內部的功耗;

4.lib中的功耗

1.漏電功耗

下圖為庫中的漏電功耗,漏電功耗與單元的狀態有關,即stage dependent(SD);

基于輸入電源的leakage信息:

? leakage_power_unit:工具根據Leakage_power_unit屬性確定單位;

? leakge_power:定義狀態相關(when)的漏電功耗,如上圖中的!A&!B表示當A=B=0時,leakage power的值;

? cell_leakge_power:如果某個狀態在leakge_power中未定義,則使用cell_leakge_power的值;

總的漏電功耗,由每個狀態下的漏電功耗乘以該狀態下的總仿真時間的百分比,并求和得到每個單元的總漏電功耗;

由于leakage_power是狀態相關,堆疊效應(stack effect)可以降低leakage_power。

例如將一個MOS管強制拆分成2個堆疊的MOS管,2個堆疊的MOS管有相同的輸入;

2.internal power

internal power與狀態有關,與路徑有關,即即stage dependent path dependent(SDPD)

? (1)單輸入的cell,internal power為input transiton和output load的二維表;

這里的internal power是定義在輸出端的,包括兩部分,rise_power和fall_power;

例如下圖中定義了從A pin到Z pin的internal power;

-(2)對于多輸入的組合邏輯門如nand,xor等;

這類cell在特定條件下某一個或者幾個pin的輸入值對輸出不造成影響,在lib中定義在input pin,input pin的internal power只與該pin的input transition相關(也叫hidden power);

例如當nand的B輸入為0時,不管A的輸出是什么,最終輸出都是0。此時盡管A對輸出沒有貢獻,但是它仍然會消耗一部分功耗;

當B為1的時候,從A pin到Z pin的internal power同樣也是二維查找表;

-(3)對于時序邏輯單元 -CK pin即使在鎖存的數值沒有變化的時候仍然會消耗能量;

3.internal power的建模方式

? 在PTPX ug中有如下描述,PTPX默認lib中的internal power計算公式為formula 1和formula 2;

? 由于switch消耗的總能量switch_energy為C L *V^2^

在這種方式中,0.5 * switch_energy算在了上升沿,0.5 * switch_energy算在了下降沿;而實際上switch_energy只發生在對上升沿電容充電過程中,此時得到的值并不代表真實的internal power值;

-另外一種計算方式如下formula 3和formula 4

?關于如何判斷:如果lib中internal power的fall power多為負值,那么為第一種方式;

4.internal power的單位

lib中internal power不是功率,而是消耗的能量,因此單位是焦耳而不是瓦特;

由3.中的式子可以看出,internal power的單位與CV^2^相同;

在lib中,電容C單位為Pf,電壓單位為V,因此internal power的單位為Pf*V = PJ

-

MOS管

+關注

關注

108文章

2395瀏覽量

66595 -

反相器

+關注

關注

6文章

310瀏覽量

43244 -

靜態功耗

+關注

關注

0文章

17瀏覽量

8927 -

泄漏電流

+關注

關注

0文章

21瀏覽量

6927 -

電容充放電

+關注

關注

0文章

94瀏覽量

5829

發布評論請先 登錄

相關推薦

芯片功耗組成—internal power與總功耗的理解

芯片功耗組成—internal power與總功耗的理解

評論