一、何為clock gating

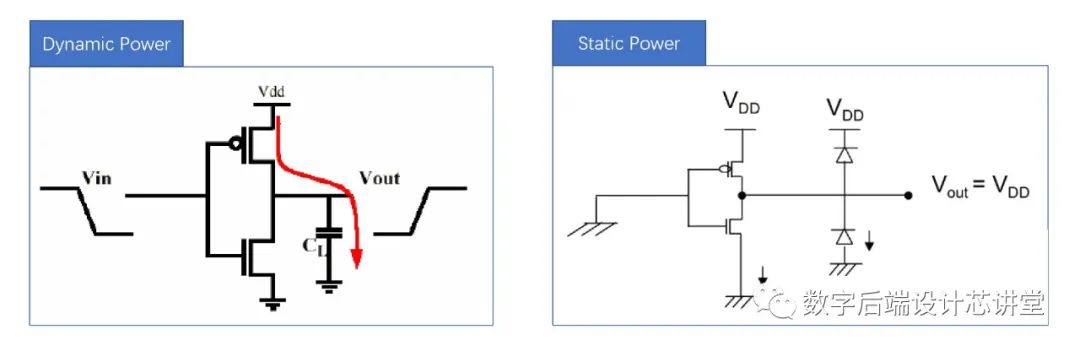

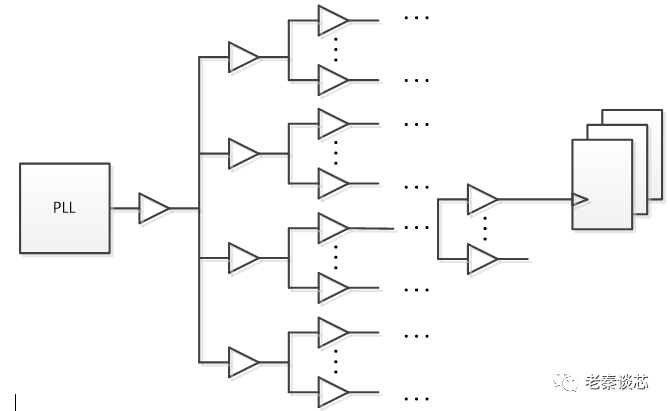

芯片中大部分的動態功耗消耗在時鐘網絡中。這是由于時鐘樹上的單元(cells)有較高的翻轉率、驅動能力較大且數量較多所導致的。

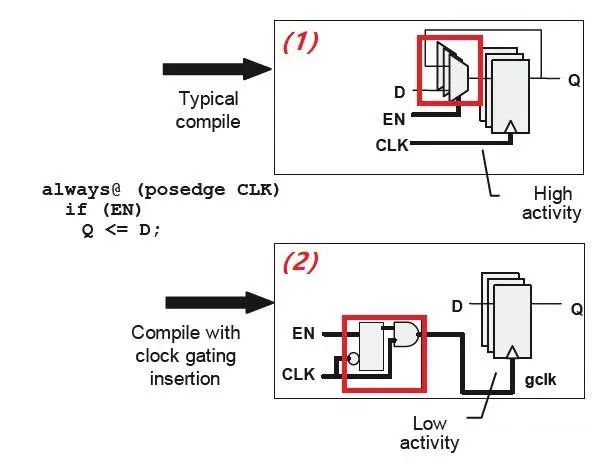

因此,為了有效減小時鐘樹上的動態功耗,人們引入了門控時鐘(clock gating)技術,即用一個控制信號控制時鐘的開啟,在模塊不工作時關閉時鐘,在工作時打開時鐘,從而降低觸發器總的翻轉率,達到降低功耗的目的。

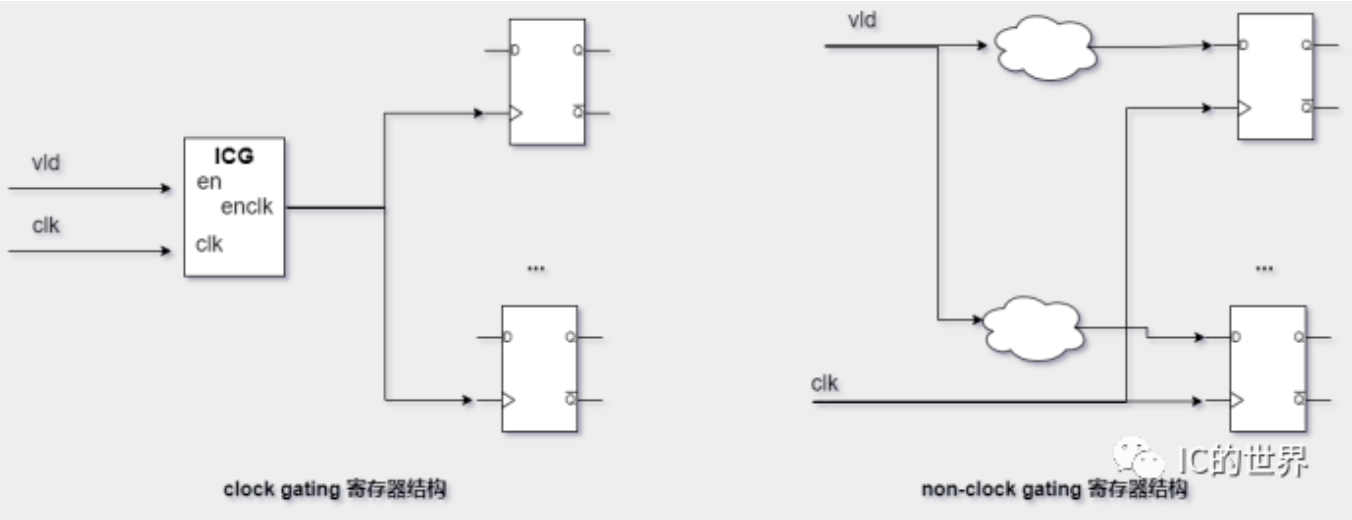

插入門控時鐘單元來降低芯片功耗的效果主要由單個門控時鐘單元所控制的觸發器或鎖存器的數量決定。

? 新增的clock gating單元本身也會增加功耗和面積;當clock gating單元輸出端控制的寄存器數目較少時,可能會導致增加的功耗比時鐘翻轉降低的動態功耗還要大。控制的寄存器數量越多,效果越明顯。在綜合的時候,可以設置采用clock gating的最低RegisterBank位數。

? 降低動態功耗和時鐘關斷的時間比例有關。如果一個模塊關斷的時間很短,那么加入clock gating就用處不大。

? clock gating的效果取決于其在時鐘樹的位置,是靠近clock tree的root還是sink。靠近root時,可以控制更多的寄存器,對功耗降低更有效;而靠近sink時,則timing更容易滿足。

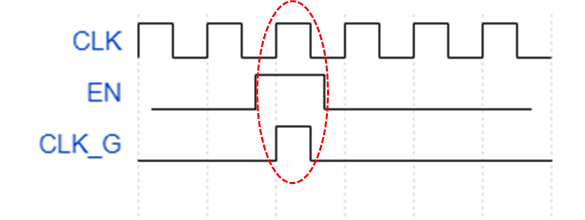

例如,在這個電路中,只有當EN為1時,CLK信號才會重寫DFF的數據,否則的話,所有的翻轉都是無效的。因此,只需要實現CLK_G的波形即可。

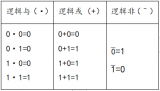

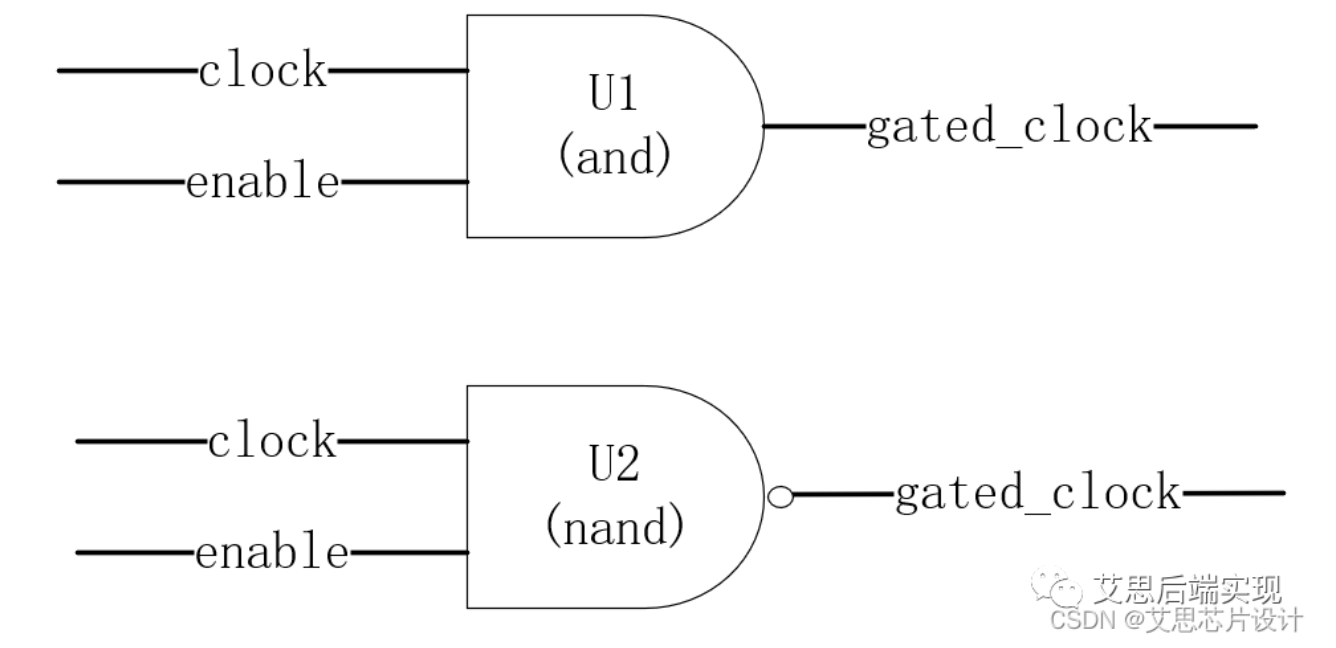

對于簡單邏輯門的clock gating,最簡單的實現方式是使用AND門或OR門來實現,對CLK信號進行與或運算。

1. AND門clock gating

(1)基本概念

對于AND門的clock gating,即高電平有效的gating,當EN為1時,門控打開,CLK_IN信號可以傳遞出去;而當EN為0時,門控關閉,CLK_IN信號則無法通過門控傳遞出去。

如上圖所示,對于AND門的clock gating,EN信號的切換必須發生在CLK_IN的低電平區間,否則在輸出CLK_OUT時可能會出現glitch,如下圖所示。

(2)timing check

1)上升沿觸發

在上圖中,UAND0/B pin是clock信號,而gating信號則由UDFF0/Q經過組合邏輯后輸入到UAND0/A pin中。

在前面的討論中,我們已經得知,如果EN信號來自上升沿觸發的寄存器,則對于setup check來說,要求門控信號在上升沿之前到達;而對于hold來說,則要求門控信號只能在下降沿之后發生變化。

因此,針對上圖電路中的UAND0/B pin,CLKA發出的gating信號只能在5 – 10ns的范圍內達到,才能滿足時序要求。

此時,hold是半周期check,比較難meet;

以下是setup和hold check的timing report:

setup:

hold:

2)下降沿觸發

如果使用下降沿觸發的寄存器產生EN信號,則對于hold來說是0 cycle check,而對于setup來說則是半周期check。因此,在使用基于AND門的gating時,EN信號通常由下降沿觸發的寄存器產生。

如下圖所示,即使使用下降沿觸發的寄存器產生EN信號,對于基于AND門的gating,gating信號依然需要在5 – 10ns之間到達,以滿足時序要求。

setup和hold check的timing report:

setup

hold

2. OR門clock gating

(1)基本概念

對于OR門的clock gating,即低電平有效的gating,當EN為0的時候,門控打開,CLK_IN可以傳遞出去;當EN為1的時候,門控關閉。

需要注意的是,在實現OR門的clock gating時,EN信號的切換必須發生在CLK_IN的高電平區間,以避免在輸出CLK_OUT時出現glitch,如下圖所示。

(2)timing check

1)上升沿觸發

類似于之前的討論,如果EN信號來自上升沿觸發的寄存器,則對于setup check來說,要求門控信號在下降沿之前到達;對于hold來說,則要求門控信號只能在上升沿之后發生變化。

因此,針對MCLK發出的gating信號,在這種情況下需要在0 – 4ns的范圍內到達,才能滿足時序要求。

根據上述時序要求,此時hold為0 cycle check,而setup為半周期check。

setup和hold check的timing report:

setup

hold

2)下降沿觸發

與之前討論類似,如果EN信號來自下降沿觸發的寄存器,則hold為半周期check,比較難以滿足。因此,在基于OR門的gating技術中,建議使用上升沿觸發的寄存器來產生EN信號,以確保時序要求的滿足。

3. 基于latch的clock gating

根據之前的討論可知,在基于基本邏輯門的clock gating技術中,EN信號的時間窗口只有半個周期的時間,因此對于一些時序要求較為嚴格的電路,可能需要使用latch來實現timing borrow,以確保時序的滿足。

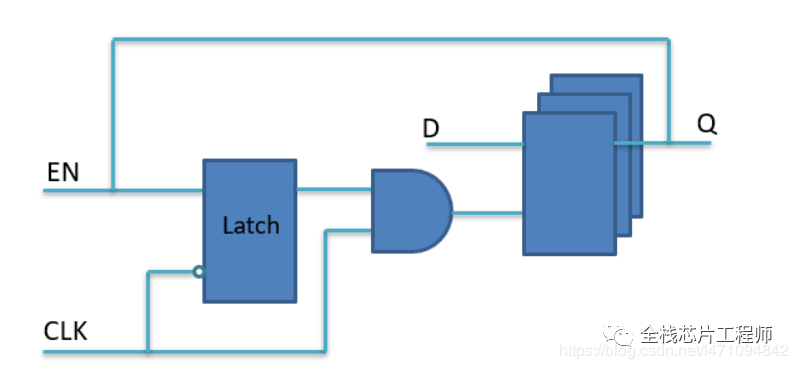

(1) Latch + AND門的gating

如上圖所示,在AND門前面加入low-active latch,EN信號來自上升沿觸發器。

當時鐘信號是低電平時,latch處于透明狀態,根據輸入更新輸出;當時鐘信號從低電平變為高電平時,latch會讀取數據輸入端的輸入信號,并將其保存在鎖存器內部的狀態中;波形圖如下:

由于這種latch是低電平有效的,因此在時鐘高電平期間,即使EN信號存在glitch(如上圖中紅色虛線1所示),也不會影響latch的輸出EN_Latch。

而在時鐘低電平期間,EN信號的glitch會傳遞到latch的輸出(如上圖中紅色虛線2所示),但由于EN_Latch需要與CLK信號做與運算,此時gating信號CLK_Gated仍然不會受到影響。

如上圖所示,無論EN在0-1 ns還是1-2 ns之間變化,CLK_Gated均不受影響,即EN可以在0-2 ns一個周期的時間窗口內到達;此時,hold是0 cycle check,setup是一個周期check;

基于這種結構的clock gating,既可以避免毛刺,同時也避免了EN信號只有半個周期的要求。

(2) Latch + OR門的gating

與Latch + AND門不同的是,需要使用low-active latch,且EN信號來自下降沿觸發的寄存器。

4. ICG

(1)分離時鐘門控

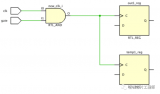

上述討論中提到的基于latch的clock gating結構,指的是分離的時鐘門控單元,當考慮skew時,依然可能會引入glitch的問題(以latch + AND門為例)。

在下圖中,delay是指,當CLK為0的時候,latch透明,數據信號EN要傳輸到latch的輸出端EN_Latch,所經過的一個鎖存器的延遲(CLK to latch/Q delay);

CLK一路送到latch,另一路送到AND/B,當latch和AND在layout中相距較遠時,此時CLK和CLK_B之間就會有skew存在;

CLK和CLK_B之間的skew會引入到CLK_Gated信號中,并可能導致毛刺問題。如果skew的時間差大于delay,就可能會在CLK_Gated信號中引入毛刺,毛刺的寬度大約為skew-delay。

因此,在物理實現的時候,需要設置net weight,將latch和AND門靠近擺放;并且latch/CK需要設置non-stop pin。

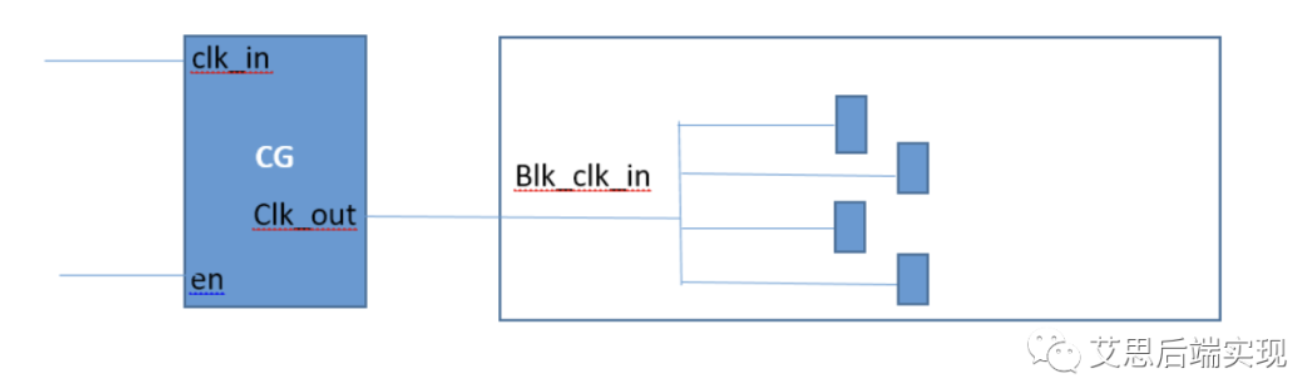

(2)集成時鐘門控ICG

現在幾乎所有的標準單元庫都提供了集成門控時鐘單元(ICG),這種單元將上述所述的latch+ AND門或latch + OR門組合成一個標準單元。

值得注意的是,latch前面的OR門是為了DFT加入的,而控制信號SE可以根據需要選擇test_mode或scan_en。

ICG的應用相對簡單,無需特別的設置,且CTS對于ICG的時序分析更加自動化。ICG的setup和hold時間都已經在庫中進行了建模,并且其CK引腳默認為implicit non-stop pin。

以上內容只是簡單的示例,實際上,根據sequential cell的類型、控制寄存器觸發邊沿和測試控制信號的位置,庫中可以提供多種不同的ICG單元。

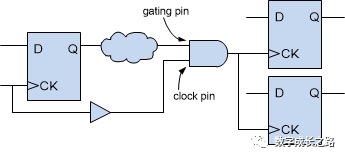

(3)什么情況下會做clock gating check(tool infer)

可以通過經過cell的信號和經過的cell類型這兩個條件判斷:

1)經過cell的信號

? 被gating的clock信號,在下游需要當做clock使用(即達到reg的CK pin、output port);

? gating的EN信號,不能帶有clock屬性;或者原來帶有clock屬性的EN信號,經過gating cell后不再當做clock使用,或者被后面的generated clock打斷了。

如圖所示,在AND門的輸出端,定義了一個generated_clock,其master為CLKA。因此CLKB無法傳播到AND后面,相當于下游不再作為clock信號使用。

在這種情況下,PT會將CLKA視為時鐘信號,CLKB視為門控信號,并對AND門進行clock gating check。

gating的EN信號和被gating的clock信號,要fanout到gating cell相同的輸出pin;如圖中一個EN和CLK,一個faout到了A,另一個fanout到了B,那么工具是不會自動的做clock gating check的。

以上三個條件要同時滿足,工具才會做clock gating check。

2)經過的cell類型

除了上述三個約束條件外,另一個需要滿足的條件是信號必須通過非復雜類型的cell。如果一個cell是non-unate cell,那么這個cell可以被視為復雜類型的cell。

對于復雜類型的cell(如常見的異或、同或和MUX),工具不會自動執行時鐘門控檢查。

append

? 可以通過使用set_clock_gating_check命令來顯式地指定門控單元的時鐘門控關系。

? 如果用戶使用set_clock_gating_check命令設置的時鐘門控檢查類型與工具推斷出的不一致,則通常會報警告,并且以用戶的設置為準。

? 此外,用set_clock_gating_check設置的setup/hold時間值優先級高于庫中定義的值。

? 如果不需要進行某些時鐘門控檢查,則可以使用set_disable_clock_gating_check命令將其禁用。

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

鎖存器

+關注

關注

8文章

905瀏覽量

41448 -

觸發器

+關注

關注

14文章

1996瀏覽量

61057 -

門控時鐘

+關注

關注

0文章

27瀏覽量

8943 -

CLK

+關注

關注

0文章

127瀏覽量

17129

發布評論請先 登錄

相關推薦

FPGA的時鐘門控是好還是壞?

邏輯電路的基礎知識

通常有兩種不同的時鐘門控實現技術

什么是門控時鐘 門控時鐘降低功耗的原理

ASIC的clock gating在FPGA里面實現是什么結果呢?

clock gating基礎知識介紹:基本邏輯門控/ICG

clock gating基礎知識介紹:基本邏輯門控/ICG

評論