在不同的資料上看到關(guān)于MUX 的時(shí)序約束的兩個(gè)示例,分享一下

例子1

一、MUX前沒有邏輯電路的時(shí)鐘結(jié)構(gòu)

時(shí)鐘設(shè)計(jì)的一般原則是在靠近時(shí)鐘源頭的地方將各種所用頻率時(shí)鐘都產(chǎn)生,再引給內(nèi)部邏輯使用,并且最好用一個(gè)模塊單獨(dú)處理,所以兩個(gè)輸入時(shí)鐘一般來(lái)自端口輸入或PLL輸出,在經(jīng)過MUX前不驅(qū)動(dòng)任何數(shù)字邏輯;

首先創(chuàng)建兩個(gè)源時(shí)鐘:

create_clock –name clk1 –period $clk_period $clk1_src_pin –add

create_clock –name clk2 –period $clk_period $clk2_src_pin –add

對(duì)于MUX后面的約束,分為同步異步兩種情況分開討論:

異步

如果MUX的兩個(gè)輸入時(shí)鐘是MUX后都可以不創(chuàng)建生成時(shí)鐘,工具基于兩個(gè)時(shí)鐘分別進(jìn)行時(shí)序分析,只需用set_clock_groups設(shè)定一下兩個(gè)時(shí)鐘的異步關(guān)系:

set_clock_groups –asynchronous –name clk_async –group “clk_1” –goup “clk2”

同步

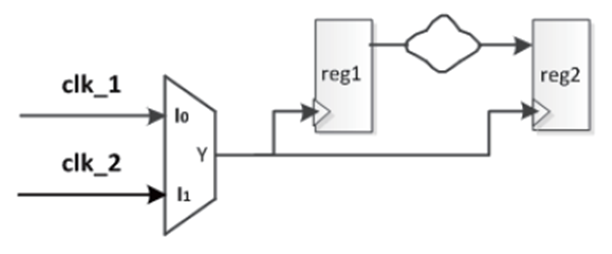

對(duì)于MUX的兩個(gè)輸入時(shí)鐘同步的情況,可以抽象成如下的結(jié)構(gòu):

由于時(shí)鐘只能穿過時(shí)序邏輯,對(duì)于時(shí)序邏輯的輸出,STA工具認(rèn)為是數(shù)據(jù),所以分頻reg的Q端必須要?jiǎng)?chuàng)建分頻時(shí)鐘;

由于該時(shí)鐘定義點(diǎn)是時(shí)序器件,此時(shí)不能加-comb選項(xiàng):

create_generated_clock –name clk_div $clk_div_pin –divide_by N –master clk_src –source $clk_src_pin –add

對(duì)于MUX后面的約束,存在以下幾種約束方法:

1.MUX后面不創(chuàng)建生成時(shí)鐘

由于MUX任何時(shí)候只能讓一路通過,MUX后可不創(chuàng)建時(shí)鐘,此時(shí)將clk_scr和clk_div設(shè)置為logical_exclusive即可;

set_clock_groups –logical_exclusive –name clk_div_logi_async –group “clk_src” –goup “clk_div”

由于時(shí)鐘樹的Last common point在MUX后,PT(prime time)會(huì)自動(dòng)進(jìn)行CRPR補(bǔ)償,即使不設(shè)邏輯互斥,根據(jù)PT的分析結(jié)果看,也不會(huì)引入悲觀分析;

2.MUX后創(chuàng)建一個(gè)生成時(shí)鐘

由于clk_src的頻率更高,所以以clk_scr為master_clock

此時(shí)加與不加-comb的區(qū)別:

(a)加-comb選項(xiàng)

create_generated_clock –name clk_mux0_clk_scr $mux_y_pin –devide_by 1 –master clk_scr –source $clk_scr_pin –add –comb

此時(shí)工具在追clk_mux0_clk_scr的source時(shí)會(huì)強(qiáng)制走組合路徑,即通過MUX/I0,PT計(jì)算clock latency的時(shí)候MUX只分析MUX/I0;

(b)不加-comb選項(xiàng)

對(duì)于clk_mux0_clk_src這個(gè)生成時(shí)鐘,PT計(jì)算其時(shí)鐘樹延遲(clock latency)時(shí),會(huì)分別計(jì)算MUX的兩個(gè)輸入路徑,選擇對(duì)時(shí)序結(jié)果更悲觀的,會(huì)引入過度的悲觀;

在進(jìn)行setup檢查時(shí),對(duì)capture clock latency計(jì)算會(huì)采用ckl_src → MUX/I0這條路徑;在進(jìn)行hold檢查時(shí),對(duì)capture clock latency 計(jì)算會(huì)采用ckl_src → DIV_N → MUX/I1的路徑;對(duì)于launch 時(shí)鐘latency的計(jì)算也會(huì)出現(xiàn)上述情況;

3.MUX后創(chuàng)建兩個(gè)生成時(shí)鐘

MUX后創(chuàng)建兩個(gè)生成時(shí)鐘,并且設(shè)physical_exclusive,這是更常見的做法

create_generated_clock –name clk_mux0_clk_scr $mux_y_pin –devide_by 1 –master clk_scr –source $clk_scr_pin –add –comb

create_generated_clock –name clk_mux1_clk_div $mux_y_pin –devide_by N –master clk_div –source $clk_div_pin –add

set_clock_groups –pysical_exclusive –name clk_mux_phy_async –group “clk_mux0_clk_scr” –goup “clk_mux1_clk_div”

二、MUX前有邏輯電路的時(shí)鐘結(jié)構(gòu)

如下圖:時(shí)鐘源clk_src在MUX前已經(jīng)驅(qū)動(dòng)部分邏輯,又對(duì)此時(shí)鐘進(jìn)行分頻和選擇,后面邏輯reg1、reg2的時(shí)鐘需要切換,而且reg0跟reg1、reg2之間有路徑交互;

1.上述第一種約束方法,即MUX后面不創(chuàng)建生成時(shí)鐘

會(huì)存在將reg0和reg1設(shè)成異步的問題,導(dǎo)致部分同步路徑?jīng)]有進(jìn)行時(shí)序檢查;

當(dāng)MUX/I1選通的時(shí)候,reg0的時(shí)鐘為clk_src,reg1的時(shí)鐘為clk_div,而這兩個(gè)clk是logical_exclusive的;

2.上述第二種約束方法,即MUX后面只創(chuàng)建一個(gè)生成時(shí)鐘

由于生成時(shí)鐘的master_clock設(shè)為I0傳來(lái)的clk_src,會(huì)將I1傳來(lái)的clk_div時(shí)鐘擋住,工具無(wú)法用clk_div時(shí)鐘進(jìn)行分析和優(yōu)化;

此時(shí)所有時(shí)鐘樹的Last common point在MUX前,工具無(wú)法進(jìn)行 CRPR 補(bǔ)償;

此時(shí)加與不加-comb的區(qū)別:

(a)加-comb選項(xiàng)

對(duì)于從reg0到reg1這條timing path的capture clock latecy,工具只會(huì)去分析經(jīng)過MUX/I0的情況;

當(dāng)MUX切換到I1時(shí),由于經(jīng)過寄存器DIV_N分頻的路徑一般比MUX/I0的路徑延時(shí)要長(zhǎng),reg1的時(shí)鐘樹可能變長(zhǎng),這就可能導(dǎo)致setup不滿足時(shí)序要求;

(b)不加-comb選項(xiàng)

同樣對(duì)于reg0到reg1這條timing path,工具按照悲觀原則去分析;

3.上述第三種約束方法,即MUX后面創(chuàng)建兩個(gè)個(gè)生成時(shí)鐘

雖然麻煩,但是最準(zhǔn)確;

4.方法四

除了上述三種方法外,還有一種方法;如下圖所示,在MUX/I0這一路插入一個(gè)buffer,在buffer后面創(chuàng)建一個(gè)生成時(shí)鐘,然后和clk_div設(shè)置logical exclusive即可,MUX后面不需要再創(chuàng)建時(shí)鐘;

create_generated_clock –name clk_buffer $buffer_pin –devide_by 1 –master clk_src –source $clk_src_pin –add

set_clock_groups –logical_exclusive –name clk_buffer_div_logi_async –group “clk_buffer” –goup “clk_div

5.更復(fù)雜的情況

如果是比上述更復(fù)雜的情況,例如下圖,DIV_N還有一路單獨(dú)驅(qū)動(dòng)reg3;對(duì)于這種結(jié)構(gòu),上述方法(4)就不適用了,因?yàn)楫?dāng)MUX選擇I0的時(shí)候,存在reg2和reg3為異步的問題;

總結(jié)

正確的約束,能讓工具看到正確的路徑;

但是當(dāng)clk_src到MUX的兩個(gè)輸入延時(shí)幾乎一致的時(shí)候,工具無(wú)論選擇走哪路,差別都很小,也就幾乎不會(huì)影響時(shí)序檢查的結(jié)果了;所以電路真正實(shí)現(xiàn)還是要靠將兩路做等長(zhǎng);

因此,盡量將時(shí)鐘產(chǎn)生邏輯放在一個(gè)模塊里面,且盡量放在功能邏輯之前;

例子2

如下圖這個(gè)例子:

約束1

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 UMUX/Y -source FFdiv2/CK –master CLK –add

create_generated_clock -name CLKdiv4 -divide_by 4 UMUX/Y -source FFdiv4/CK -master CLK –add

set_clock_groups -physically_exclusive -group {CLK} -group {CLKdiv2} –group {CLKdiv4}

這樣約束會(huì)有幾個(gè)問題:

(a)timing report中缺少master clock的group

這是因?yàn)槊總€(gè)create_generated_clock約束都會(huì)覆蓋該點(diǎn)存在的任何其他時(shí)鐘,除非它們也在該點(diǎn)創(chuàng)建了生成時(shí)鐘并使用 -add 選項(xiàng);

(b)Clock Source Latency Path問題

例如一條從FF1到FF2的setup timing path:launch path經(jīng)過UMUX/C,capture path經(jīng)過UMUX/A,如示例一中所述,悲觀分析了;

這是因?yàn)閏reate_generated_clock的-source選項(xiàng)指定的pin/port處,工具會(huì)查找上面存在的所有Clock以及它的相位關(guān)系,然后來(lái)確定哪個(gè)是master clock以及它的相位和generatedclock是否滿足定義的相位關(guān)系(同相或反相),但它不會(huì)控制source latency path;

盡管我們?yōu)镃LKdiv2_mux指定了“ -source FFdiv2/CK”,但它不會(huì)強(qiáng)制source latency path通過該引腳。相反,PT觀察到在引腳FFdiv2/CK處存在與generated clock同相位的時(shí)鐘CLK。然后,工具將搜索所有可能的同相路徑,使其返回時(shí)鐘源CLK,時(shí)鐘源是名為CLK的輸入端口;

由于這些是setup路徑,因此返回輸入端口CLK的最慢同相路徑是通過FFdiv4的路徑,最快的同相路徑是通過未分頻的路徑;

約束2

引導(dǎo)生成時(shí)鐘的source latency路徑的最佳方法是直接在分頻reg的Q創(chuàng)建生成時(shí)鐘;

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 FFdiv2/Q -source FFdiv2/CK

create_generated_clock -name CLKdiv4 -divide_by 4 FFdiv4/Q -source FFdiv4/CK

set_clock_groups -physically_exclusive -group {CLK} -group {CLKdiv2} –group {CLKdiv4}

約束3(crosstalk問題)

在上面的約束中,CLKdiv2和CLKdiv4不會(huì)同時(shí)出現(xiàn),因此PT也不會(huì)分析他們之間的SI(物理互斥不會(huì)計(jì)算SI);然而在這兩個(gè)時(shí)鐘在MUX前是可以同時(shí)出現(xiàn)的;

修改約束如下:

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 FFdiv2/Q -source FFdiv2/CK

create_generated_clock -name CLKdiv4 -divide_by 4 FFdiv4/Q -source FFdiv4/CK

create_generated_clock -name CLK_mux -combinational UMUX/A -source UMUX/A

create_generated_clock -name CLKdiv2_mux -combinational UMUX/B -source UMUX/B

create_generated_clock -name CLKdiv4_mux -combinational UMUX/C -source UMUX/C

set_clock_groups -physically_exclusive

-group {CLK_mux}

-group {CLKdiv2_mux}

-group {CLKdiv4_mux}

-

Mux

+關(guān)注

關(guān)注

0文章

38瀏覽量

23354 -

SRC

+關(guān)注

關(guān)注

0文章

60瀏覽量

17962 -

時(shí)序約束

+關(guān)注

關(guān)注

1文章

115瀏覽量

13409 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17128 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6397

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

VIVADO時(shí)序約束及STA基礎(chǔ)

請(qǐng)教時(shí)序約束的方法

學(xué)習(xí)時(shí)序約束 遇到的問題,求助

關(guān)于時(shí)序約束

時(shí)序約束與時(shí)序分析 ppt教程

FPGA中的時(shí)序約束設(shè)計(jì)

時(shí)序約束的步驟分析

Vivado進(jìn)行時(shí)序約束的兩種方式

時(shí)序約束中如何精確找到匹配的template?

兩個(gè)例子講解現(xiàn)場(chǎng)壓力變送器應(yīng)急調(diào)校方法,加深理解資料下載

約束、時(shí)序分析的概念

關(guān)于MUX時(shí)序約束的兩個(gè)例子

關(guān)于MUX時(shí)序約束的兩個(gè)例子

評(píng)論