圖像在采集和傳輸?shù)倪^程中,通常會(huì)產(chǎn)生噪聲,使圖像質(zhì)量降低,影響后續(xù)處理。因此須對(duì)圖像進(jìn)行一些圖像濾波、圖像增強(qiáng)等預(yù)處理。為改善圖像質(zhì)量,去除噪聲通常會(huì)對(duì)圖像進(jìn)行濾波處理 ,這樣既能去除噪聲,又能保持圖像細(xì)節(jié)。

FPGA圖像處理方法

1、圖像增強(qiáng)

兩大方法:空間域方法和時(shí)間域方法(以后再詳述)

2、圖像濾波

(1)平滑空間濾波器

(2)中值濾波算法

3、圖像邊緣檢測(cè)

邊緣指圖像局部強(qiáng)度變化最顯著的部分。邊緣主要存在與目標(biāo)與目標(biāo)、目標(biāo)與背景、區(qū)域與區(qū)域(不同色彩)之間,邊緣檢測(cè)是圖像分割、紋理特征和形狀等圖像分析的基礎(chǔ)。

4、圖像目標(biāo)提取算法

(1)相鄰幀差法

對(duì)相鄰的兩幀圖像求差,將圖像中的目標(biāo)位置和形狀顯示出來,差分后的圖像不為零的即為目標(biāo)。在兩幀圖像中,灰度值沒有變化的部分被剪掉,主要是背景和一些小部分目標(biāo)。

由檢出的部分大致可以確定運(yùn)動(dòng)目標(biāo)的位置,但是該方法的確定是當(dāng)物體的位移較小時(shí),難以確定目標(biāo)的運(yùn)動(dòng)方向并且在目標(biāo)的內(nèi)部產(chǎn)生空洞。

(2)光流法

(3)背景幀差法

此方法選取一副圖像作為背景圖像,用采集到的圖像與背景圖像差分,在背景圖像選取合適的時(shí)候,能比較準(zhǔn)確地分割出目標(biāo)物體。速度快,易于實(shí)現(xiàn),并能提供完整的運(yùn)動(dòng)區(qū)域信息。

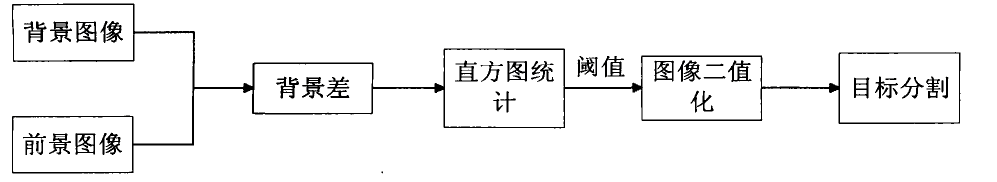

具體原理圖:

如上圖,首先將背景圖像和當(dāng)前圖像進(jìn)行差分,得到兩幅圖像的背景差圖像(從存儲(chǔ)器中提取出亮度分量得到灰度圖像,經(jīng)過圖像的中值濾波等處理后,進(jìn)入圖像檢測(cè)算法模塊;然后只需將兩幅圖像中對(duì)應(yīng)的像素相減后再取絕對(duì)值即可得到背景差圖像),采用直方圖統(tǒng)計(jì)的方法來確定圖像的 二值化閾值(閾值一般設(shè)定為G分量的平均值),最后對(duì)圖像進(jìn)行二值化處理,提取出目標(biāo)的輪廓。

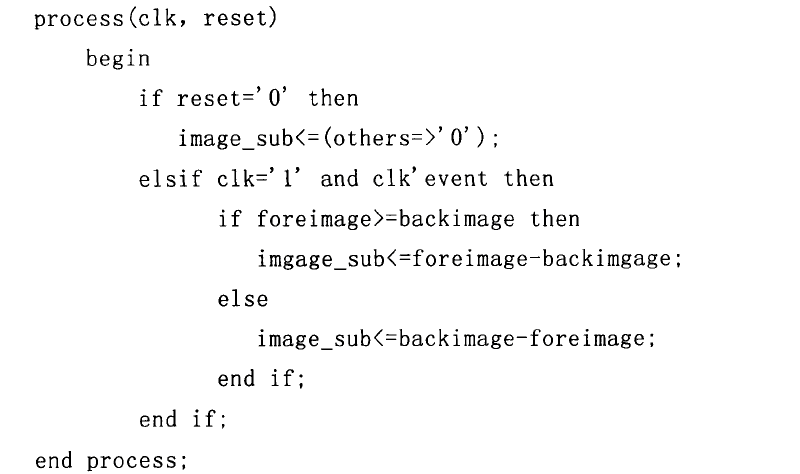

求背景差 VHDL代碼實(shí)現(xiàn):

5、注意點(diǎn)

(1)視頻輸入設(shè)備的采樣頻率和FPGA的晶振頻率通常不一樣,因此會(huì)產(chǎn)生異步時(shí)鐘域的問題,因此可以先將采集的圖像數(shù)據(jù)存入到FIFO中,然后再存進(jìn)SRAM中。

(2)不同時(shí)鐘域之間會(huì)產(chǎn)生亞穩(wěn)態(tài)情況:當(dāng)信號(hào)通過兩個(gè)時(shí)鐘域的交界處時(shí),將會(huì)分別由兩個(gè)時(shí)鐘來控制信號(hào)的值,此時(shí)如果兩時(shí)鐘信號(hào)的敏感延非常接近,將出現(xiàn)數(shù)據(jù)信號(hào)不穩(wěn)定的情況。

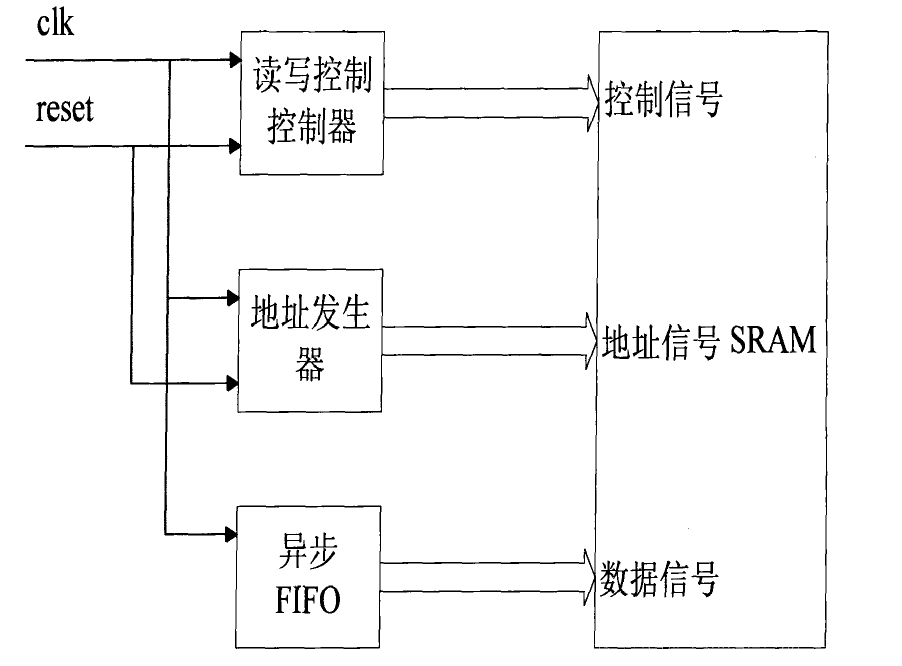

圖像數(shù)據(jù)存儲(chǔ)

從攝像頭采集的數(shù)據(jù)先進(jìn)入FIFO緩沖器中,存滿一行的數(shù)據(jù)后,再由SRAM控制器讀取到SRAM中。注意:采集的視頻圖像數(shù)據(jù)是隔行掃描的,即先傳奇數(shù)場(chǎng)再傳偶數(shù)場(chǎng),為了后續(xù)圖像處理的方便操作,須將兩場(chǎng)數(shù)據(jù)合并為完整的一幀圖像。

具體方法:先將奇數(shù)場(chǎng)的數(shù)據(jù)以隔行的方式存在SRAM中,即奇數(shù)場(chǎng)的第一行存在SRAM的第一行,第二行存在SRAM的第三行,與第一行相隔一行的地址空間,直到行數(shù)據(jù)全都發(fā)送完畢,然后開始存放偶數(shù)場(chǎng),第一行放在第二行等等。

內(nèi)部控制器controller根據(jù)異步FIFO的滿空狀態(tài)來使能SRAM控制器,當(dāng)FIFO滿狀態(tài)有效空狀態(tài)無效時(shí),SRAM開始從FIFO中讀取數(shù)據(jù)。

使用FIFO的目的:避免亞穩(wěn)態(tài)。由于采集頻率和FPGA的時(shí)鐘頻率不同,為異步時(shí)序電路。且數(shù)據(jù)經(jīng)FIFO后時(shí)鐘信號(hào)統(tǒng)一為系統(tǒng)時(shí)鐘。

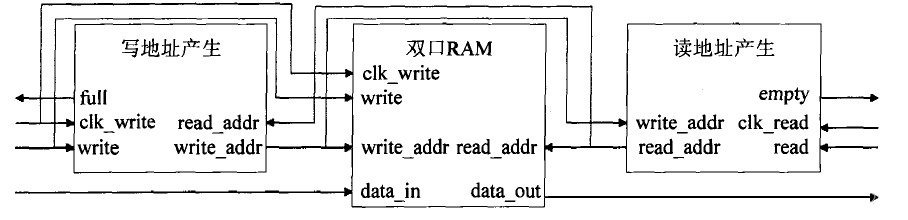

異步FIFOzho中包含:寫地址產(chǎn)生,讀地址產(chǎn)生和一個(gè)雙口RAM。

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:FPGA圖像處理方法

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1620文章

21507瀏覽量

598835

原文標(biāo)題:FPGA圖像處理方法

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ALINX FPGA+GPU異架構(gòu)視頻圖像處理開發(fā)平臺(tái)介紹

FPGA異步信號(hào)處理方法

基于FPGA的圖像采集與顯示系統(tǒng)設(shè)計(jì)

FPGA設(shè)計(jì)經(jīng)驗(yàn)之圖像處理

基于FPGA的實(shí)時(shí)邊緣檢測(cè)系統(tǒng)設(shè)計(jì),Sobel圖像邊緣檢測(cè),FPGA圖像處理

FPGA設(shè)計(jì)中 Verilog HDL實(shí)現(xiàn)基本的圖像濾波處理仿真

FPGA圖像處理—VESA標(biāo)準(zhǔn)與視頻流介紹

機(jī)器視覺之圖像增強(qiáng)和圖像處理

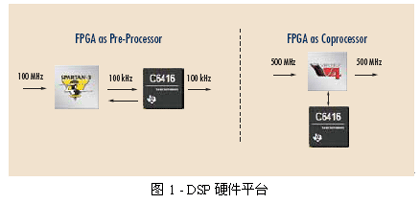

FPGA協(xié)處理的優(yōu)勢(shì)有哪些?如何去使用FPGA協(xié)處理?

機(jī)器視覺:圖像處理技術(shù)、圖像增強(qiáng)技術(shù)

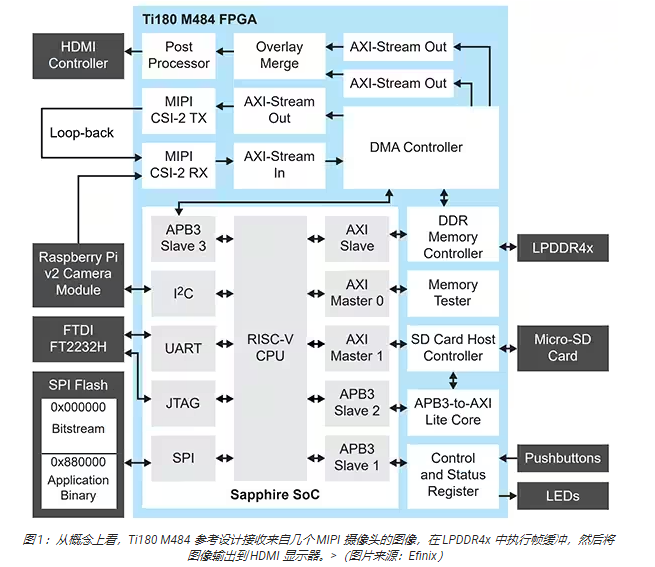

為什么以及如何將 Efinix FPGA 用于 AI/ML 成像第 2 部分:圖像采集和處理

FPGA圖像處理方法

FPGA圖像處理方法

評(píng)論