從7nm到5nm,從5nm到3nm,半導(dǎo)體產(chǎn)業(yè)對于先進(jìn)工藝制程的追求永不停歇。2022年,當(dāng)臺積電宣布已經(jīng)掌握成功大量量產(chǎn)3nm鰭式場效電晶體制程技術(shù)后,1nm開始一步步逼近。

對于先進(jìn)工藝的掌握,意味著更高的性能、更頂尖的技術(shù)。從 3nm跨越到1nm,這其中面臨的技術(shù)挑戰(zhàn)猶如天塹。因此,1nm對于業(yè)界來說也充滿著誘惑。

01 1nm,念念不忘

工藝制成的研發(fā)和生產(chǎn)需要大量的資源,一方面是技術(shù)積累,如晶體管架構(gòu)、材料選擇、制造過程等方面都需要解決難題;另一方面還需要強(qiáng)大的資金、人才和設(shè)備,眾所周知從5nm走到3nm,生產(chǎn)成本也翻了一番。并非人人都有“資格”追求1nm。從28nm跳級到1nm這之間的差距絕對令人望而卻步。

我們來看看,目前有野心追求1nm的機(jī)構(gòu)和企業(yè)分別有哪些。

最新的消息是日本計劃與法國合作開發(fā)1nm制程半導(dǎo)體。具體來看,是日本芯片制造商 Rapidus、東京大學(xué)將與法國半導(dǎo)體研究機(jī)構(gòu)Leti合作,共同開發(fā)電路線寬為1nm級的新一代半導(dǎo)體設(shè)計的基礎(chǔ)技術(shù)。

法國的CEA-Leti成立于1967年,該研究所的前身是成立于1957年的CENG(格勒諾布爾核研究中心)的電子系。在芯片的發(fā)展進(jìn)程中,CEA-leti的也有很多重要里程碑事跡,如其是推動硅上絕緣體場效應(yīng)管(FD-SOI)技術(shù)的重要推動者之一。

日本芯片制造商Rapidus大家應(yīng)該不陌生了。這家企業(yè)成立的時間非常晚——2022年8月,其集合了日本的8家企業(yè)和日本政府提供的700億日元資金。一成立的目標(biāo)就是,要在4年內(nèi)量產(chǎn)2nm芯片。當(dāng)時與IBM建立戰(zhàn)略合作關(guān)系,向著2nm進(jìn)發(fā)。不過目前,日本國內(nèi)最先進(jìn)的制程還停留在45nm。所以日本能否通過這次“豪賭”,從45nm跨越到2nm是業(yè)界還在期待的事。

現(xiàn)在看來,日本的野心并不僅僅止步于2nm,其也想朝著1nm的目標(biāo)前進(jìn)。合作方式是 Rapidus與東京大學(xué)、Leti研究所進(jìn)行一些涉及的人員交流和基礎(chǔ)研究共享。Leti 將探索新型晶體管結(jié)構(gòu),而Rapidus和其他日本合作伙伴將派出科學(xué)家,然后評估和測試原型。

IBM在2021年就推出了全球首款2nm芯片,使用了GAA環(huán)繞柵極晶體管技術(shù),一時震動了業(yè)界。從歷史上看,從5nm走到2nm,IBM使用了不到四年。在2nm之后,IBM自然而然的走向了1nm。在2022年末的 IEDM 會議上,IBM展示了其為通向1nm及以上準(zhǔn)備的技術(shù):互連3.0和VTFET。

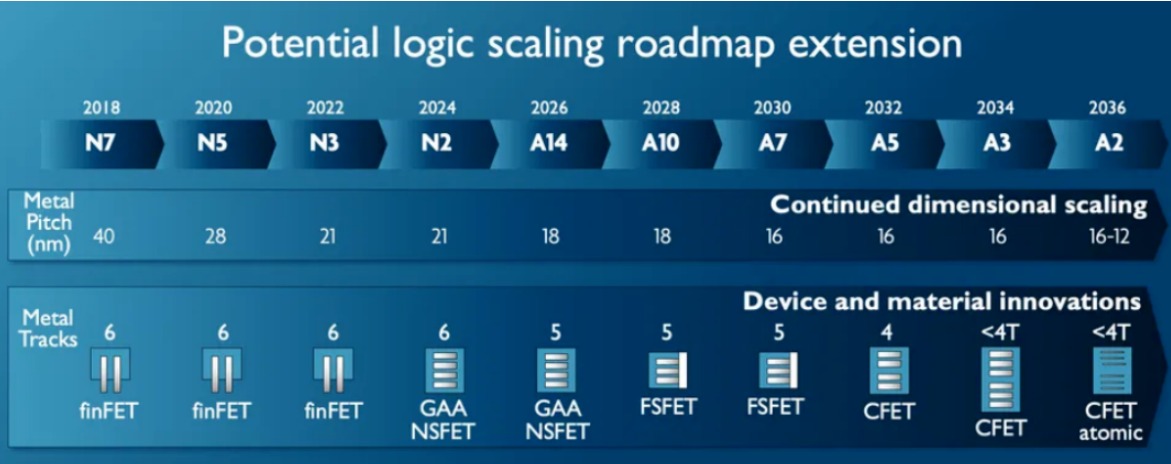

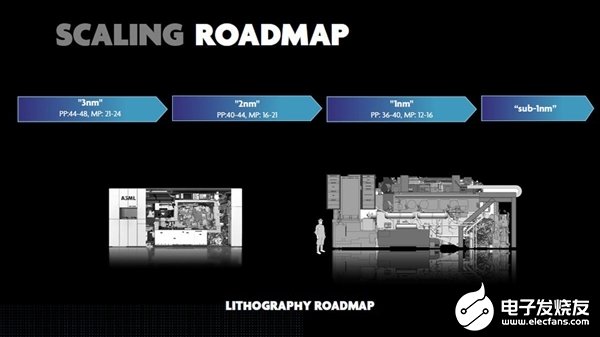

Imec在今年5月公布了1nm以下晶體管的路線圖,在其路線圖中1nm等于10埃。不僅如此,到了6月,Imec更是表示其與ASML簽署了一項重要協(xié)議,與ASML共同合作開發(fā)1nm以下芯片。ASML將提供最新型號 0.55 NA EUV、2nm 和 1nm 工藝開發(fā)關(guān)鍵的 TWINSCAN EXE:5200,以及最新型號 0.33 NA EUV TWINSCAN NXE:3800。

企業(yè)方面,作為目前唯一一家能夠成功實現(xiàn)3nm量產(chǎn)的晶圓廠,臺積電也早早開始研究1nm。臺積電已經(jīng)選定了其1nm新廠的落腳位置,在竹科龍?zhí)秷@區(qū)。從進(jìn)展上來看,若一切順利,竹科龍?zhí)秷@區(qū)三期2026年中即可供廠商展開建廠作業(yè),這也意味著臺積電1nm廠最快能夠在2026年動工,2027年試產(chǎn),2028年量產(chǎn)。實際上,這也符合Imec預(yù)測的1nm以下路線圖。

來源:IMEC

芯片龍頭英特爾對于1nm的誘惑同樣無法抗拒。從工藝節(jié)點來看,英特爾目前準(zhǔn)備將Intel 4,用于Meteor Lake處理器和Granite Rapids,下一步將是Intel 3,它將使用EUV光刻來實現(xiàn)更大的模塊化,PPW增加到18%。而英特爾最新的工藝是20A和18A。Intel 20A本來被稱為Intel 1,但是由于英特爾想要“更好的喚起下一個創(chuàng)新時代”,將其命名為20A 。

現(xiàn)在問題來了:1nm未來,如何實現(xiàn)?

02 2D材料

尋找合適的晶體管結(jié)構(gòu)以及合適的晶體管材料來實現(xiàn) 1 納米工藝幾何結(jié)構(gòu)的工作仍然是一個好的方向。使用非硅材料有利于制造非常微小的晶體管——小至 1 納米。

2019年時,IMEC就在IEEE會議上,展示2D材料可實現(xiàn)1nm以下的工藝節(jié)點。當(dāng)時IMEC已經(jīng)展示了具有微小特征尺寸的二硫化鉬 (MoS2) MOSFET可以為晶體管的極端縮放開辟途徑,遠(yuǎn)低于硅器件短溝道效應(yīng)的水平。

MoS2是一種二維材料,這意味著它可以以穩(wěn)定的形式生長,厚度僅為一個原子,最重要的是,在該尺度上具有原子精度。 麻省理工學(xué)院、南洋理工大學(xué)和臺積電的研究人員發(fā)現(xiàn),二維材料與半金屬鉍 (Bi) 結(jié)合可實現(xiàn)極低的電阻,克服了實現(xiàn) 1 納米芯片的挑戰(zhàn)。

臺積電也同樣宣布,其在2D材料方面取得突破,逼近1 nm。在2022年時,臺積電和麻省理工學(xué)院、南洋理工大學(xué)聯(lián)合發(fā)表了一篇論文,描述金屬引起的導(dǎo)電間隙帶來的制造挑戰(zhàn),以及單層技術(shù)如何受到這些金屬引起的間隙的影響。

這篇文章中建議使用后過渡金屬鉍和一些半導(dǎo)體單層過渡金屬二硫族化物來減小間隙的尺寸,從而生產(chǎn)出比以前小得多的2D晶體管。在實驗中,臺積電嘗試了目前各種低電阻的半導(dǎo)體材料,二硫化鉬(MoS2)、二硫化鎢(WS2)和二硒化鎢(WSe2)。

03

改變銅 (Cu) 互連

在計算機(jī)芯片之中,半導(dǎo)體組件之間的布線被稱為互連。簡單解釋,互連就是電流在芯片中各個晶體管、存儲器、處理單元和其他組件之間的流動方式,如果互連的傳輸越有效,那么芯片的效率就會越高。

在1997年以前,大家往往都在使用鋁互連。之后,IBM又發(fā)現(xiàn)了更有效的銅互連。銅線的導(dǎo)電電阻比鋁線低約 40%,這意味著處理速度提高約 15%。在過去的幾十年里,這種巨大的轉(zhuǎn)變導(dǎo)致銅成為互連的行業(yè)標(biāo)準(zhǔn)。

現(xiàn)在,銅互連也開始遇到了瓶頸。銅互連始終需要阻擋襯里材料來形成適當(dāng)?shù)牟季€結(jié)構(gòu)。隨著器件縮小,可用于銅布線和襯墊材料的空間變得更小。

目前業(yè)界一直在尋找其他金屬可以替代銅互連。

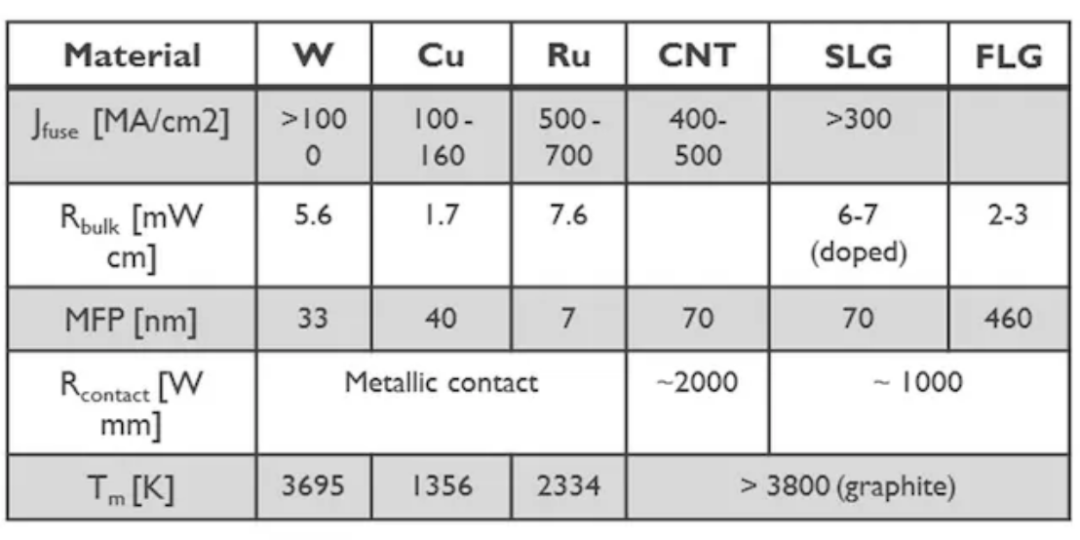

碳納米管 (CNT)、單層石墨烯 (SLG) 和少層石墨烯 (FLG))與其他相關(guān)互連材料(鎢 (W)、銅 (Cu) 和釕 (Ru))的性能比較 來源:IMEC

IBM:使用釕

IBM找的方式是使用釕。釕可以擴(kuò)展到 1 納米及以上節(jié)點,并且仍然是一種有效的導(dǎo)體,因此不需要襯墊,這有助于節(jié)省空間。通過減色圖案化方法形成的釕也有可能用于一種新型互連集成方案,稱為頂通孔集成。在這種情況下,互連通孔形成在導(dǎo)線的頂部,而不是導(dǎo)線的下方,從而允許為最關(guān)鍵的互連層形成連續(xù)的導(dǎo)線和自對準(zhǔn)通孔。此外,通過這種頂通孔集成牢固地形成嵌入式氣隙,從而減少互連寄生電容,也將有助于實現(xiàn)更快、更低功耗的芯片。IBM的研究人員使用極紫外光刻 (EUV) 雙圖案現(xiàn)有的機(jī)器上創(chuàng)建測試結(jié)構(gòu),結(jié)果表明能夠?qū)崿F(xiàn)突破。

IMEC、臺積電:使用石墨烯

與IBM的方式不同,臺積電嘗試使用石墨烯進(jìn)行多層布線。

人們對石墨烯互連應(yīng)用的興趣并不令人意外。石墨烯表現(xiàn)出高本征載流子遷移率(高達(dá)200,000cm2V -1s-1)和大載流能力(高達(dá)108A/cm2)。此外,石墨烯具有高導(dǎo)熱性和抗電遷移的競爭穩(wěn)健性。它還可以制成原子級厚度,這有助于減輕厚度對 RC 延遲的影響。

臺積電表示,當(dāng)制作不同寬度的互連原型并將其電阻與銅互連進(jìn)行比較時,發(fā)現(xiàn)寬度為15nm或更小的石墨烯互連的電阻率低于銅互連的電阻率。石墨烯的接觸電阻率也比銅低四個數(shù)量級。將金屬離子嵌入石墨烯中可以改善互連的電性能,使其成為下一代互連的有前途的材料。

IMEC則認(rèn)為石墨烯和金屬的混合結(jié)構(gòu),非常有希望成為1nm的候選者。此外,IMEC也在考慮釕 (Ru)作為銅互連的替代品。

04

改變器件架構(gòu)

如上文提到,IBM對于1nm的努力除了選擇釕互連外,還有一個就是VTFET架構(gòu)。IBM認(rèn)為,使用 VTFET,晶體管組件垂直堆疊在一起,而不是橫向堆疊,這是自計算機(jī)時代誕生以來設(shè)計芯片的標(biāo)準(zhǔn)。這極大地增加了單個芯片上可以安裝的晶體管數(shù)量,就像摩天大樓城市的人口密度遠(yuǎn)高于聯(lián)排別墅郊區(qū)的人口密度一樣。IBM的研究表明,VTFET 設(shè)計的規(guī)模可以遠(yuǎn)遠(yuǎn)超出 IBM Research 于 2021 年首次推出的最先進(jìn)的 2 納米節(jié)點納米片設(shè)計的性能。

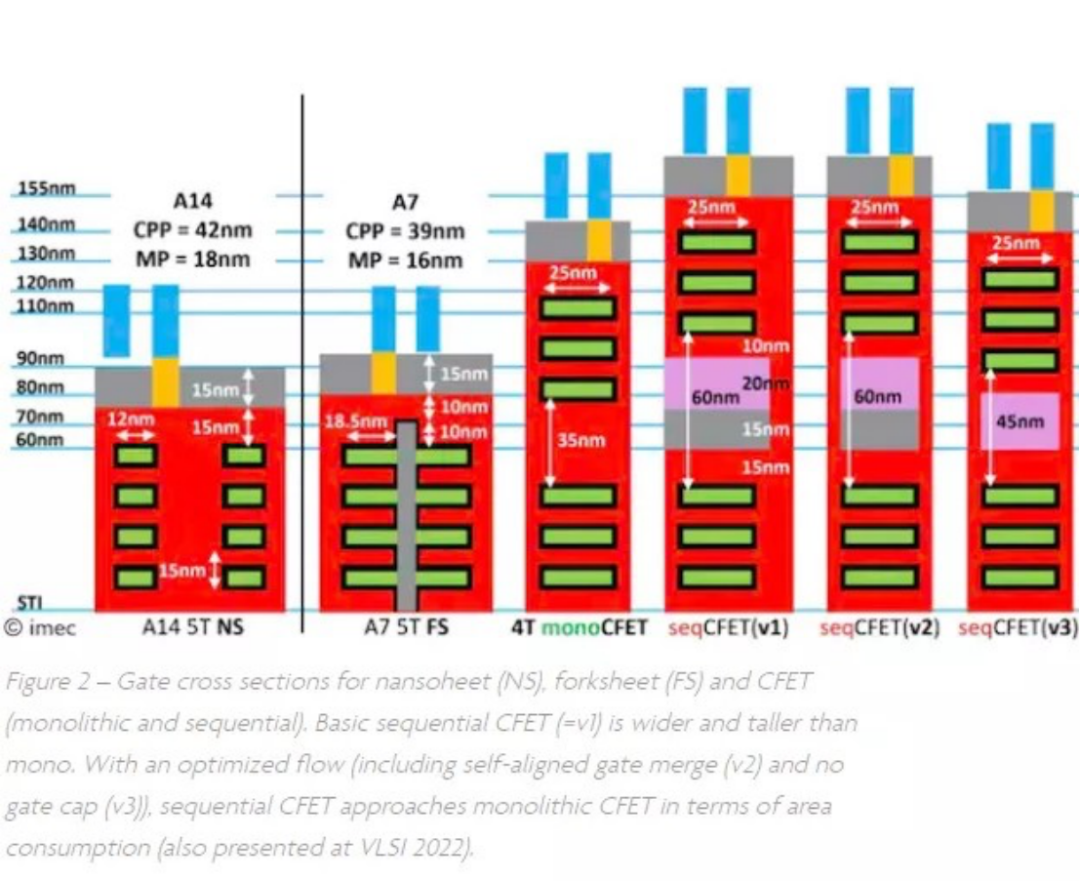

IMEC則認(rèn)為能夠超越2nm的器件架構(gòu),是Forksheet架構(gòu)。新的forksheet器件架構(gòu)是 GAA 納米片器件的自然演變,允許軌道高度從 5T 擴(kuò)展到 4.3T,同時仍然提供性能增益。或者,通過叉板設(shè)計,可用空間可用于增加板寬度,從而進(jìn)一步增強(qiáng)驅(qū)動電流。

圖側(cè)四個結(jié)構(gòu),均為CFET的變種 來源:imec

英特爾則是認(rèn)為可以使用一種GAA FET的最新形態(tài)——堆疊式CFET場效應(yīng)管架構(gòu)。這種架構(gòu)的集成密度進(jìn)一步提升,將n型和p型MOS元件堆疊在一起,可以堆疊8個納米片,比RibbonFET多一倍。目前,英特爾正在研究兩種類型的CFET:單片式(monolithic)和順序式(sequential)。不過,英特爾的CFET架構(gòu)并不是獨立提出的,而是與IMEC機(jī)構(gòu)長期合作的結(jié)果。

05

總結(jié)

在科技的世界里,1nm無疑是一個極具吸引力的存在。然而,正如我們在文章中所提到的,1nm技術(shù)雖然具有巨大的潛力,但也帶來了諸多挑戰(zhàn)。

對于許多公司和研究機(jī)構(gòu)來說,1nm可能代表著技術(shù)上的“圣杯”。它不僅僅是一個物理極限,更是一個巨大的商業(yè)機(jī)會。例如,1nm晶體管會帶來更快的處理器,更小的內(nèi)存單元,更高效的能源儲存等等。

通往1nm的道路可以謂是復(fù)雜又波折。產(chǎn)業(yè)界來看,這些學(xué)術(shù)的突破性進(jìn)展并不一定能很快用于商業(yè)化的芯片生產(chǎn)。畢竟3nm芯片的良率似乎都還是一個問題。從3nm到1nm,摩爾定律如何延續(xù),我們期待著更多的深入探索,以克服1nm技術(shù)所面臨的巨大挑戰(zhàn)。

審核編輯:黃飛

-

英特爾

+關(guān)注

關(guān)注

60文章

9900瀏覽量

171548 -

臺積電

+關(guān)注

關(guān)注

44文章

5611瀏覽量

166161 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137875 -

石墨烯

+關(guān)注

關(guān)注

54文章

1543瀏覽量

79474 -

半導(dǎo)體工藝

+關(guān)注

關(guān)注

19文章

107瀏覽量

26220

原文標(biāo)題:半導(dǎo)體工藝的極限:1nm之戰(zhàn)

文章出處:【微信號:ICViews,微信公眾號:半導(dǎo)體產(chǎn)業(yè)縱橫】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電再度突破半導(dǎo)體材料限制,離1nm又進(jìn)一步

半導(dǎo)體工藝講座

最精尖的晶體管制程從14nm縮減到了1nm

10nm、7nm等制程到底是指什么?宏旺半導(dǎo)體和你聊聊

半導(dǎo)體工藝幾種工藝制程介紹

為何說7nm就是硅材料芯片的物理極限

從7nm到5nm,半導(dǎo)體制程 精選資料分享

臺積電2nm工藝重大突破:朝著1nm挺進(jìn)

全球最先進(jìn)的1nm EUV光刻機(jī)業(yè)已完成設(shè)計

1nm之后將如何發(fā)展

1nm芯片是什么意思

芯片的極限是多少納米

臺積電已啟動1nm工藝先導(dǎo)計劃 升級下一代EUV光刻機(jī)是關(guān)鍵

臺積電1nm,如何實現(xiàn)?

半導(dǎo)體工藝極限,1nm如何實現(xiàn)?

半導(dǎo)體工藝極限,1nm如何實現(xiàn)?

評論