電子發燒友網報道(文/李寧遠)今年是生成式AI爆火的一年,各類基于生成式AI的工具席卷了今年的各類熱點,最近視頻領域Pika labs的產品也掀起了AI文生視頻的熱潮。而在生成式AI的推動下,HBM無疑是今年最火熱的高端存儲產品。

在AI芯片需求不減競爭加劇的背景下,全球最大的兩家存儲器芯片制造商三星和SK海力士都在積極擴大HBM產量搶占AI芯片存力風口。與此同時,作為HBM頭部廠商的SK海力士和三星在推進HBM迭代的同時,仍在不斷探索新的HBM芯片封裝技術。

三星此前一直在竭盡全力開發先進封裝技術如I-cube、H-cube和X-cube,近期又宣布將研發先進3D封裝技術SAINT。而SK海力士則在持續研發主打的基于TSV的封裝工藝外,近期披露準備在下一代DRAM中應用扇出封裝技術,探索HBM低成本路線。

傳統封裝無法匹配HBM需求,臺積電CoWoS供不應求

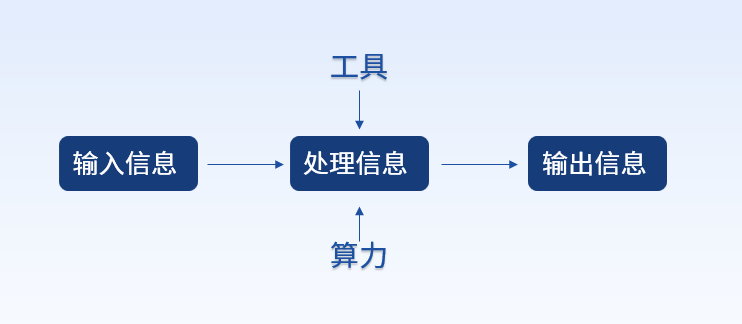

在人工智能算力發展如火如荼發展的當下,存力和算力一樣,是風口上的剛需。高性能計算里很大一部分瓶頸在于處理器與DRAM之間的通信速度限制,而且二者之間的通信速度越來越跟不上高性能計算需求前進的腳步。

為了解決這個通信速度限制,很多技術被開發了出來,比如現在同樣很火的存算一體。不過從目前來看,這些技術不可能在短時間內就解決處理器和內存之間通信限制。因此將DRAM與處理器通過封裝技術結合成為解決限制行之有效的手段。

在所有存儲芯片中,HBM也被看作是最適用于AI訓練、推理的存儲芯片。通過將多個DRAM芯片堆疊并與處理器封裝在一起,HBM實現了大容量高位寬的DDR組合。

HBM通過與處理器相同的中介層互聯實現近存計算,顯著減少了數據傳輸時間。封裝技術在其中發揮了決定性的作用,封裝技術直接影響了最后的帶寬和功耗。

HBM已經經歷了幾代產品的更迭,目前各大存儲廠商主要也是使用基于TSV的封裝技術進行芯片堆疊,基于TSV工藝的堆疊封裝技術顯著提升了HBM帶寬,并降低了功耗減小了封裝尺寸。

TSV的出現讓半導體裸片和晶圓可以實現高密度互聯堆疊在一起,是先進封裝的標志之一。TSV硅通孔技術通過硅通道垂直穿過組成堆棧的不同芯片或不同層實現不同功能芯片集成,貫穿所有芯片層的通道可以進行信號、指令、電流的傳輸,吞吐量的增加打破了單一封裝內低帶寬的限制。

傳統封裝無法匹配HBM需求,基于TSV衍生出的封裝技術,臺積電的CoWoS是目前供不應求的最理想的封裝方案。

不夸張地說,目前幾乎所有的HBM系統都封裝在CoWos上。CoWoS產能不足是行業內有目共睹的,直接造成了人工智能相關芯片的短缺。臺積電也是一再上調CoWos產能,以滿足市場需求。

三星發力3D封裝,SAINT探索HBM新存儲集成方案

作為行業頭部HBM供應商,同時在先進封裝領域布局積極的三星,在HBM升級競賽里相當積極,意圖趕超臺積電HBM先進封裝的決心也是很明顯。

此前三星為了在單個封裝內集成更多的Chiplet和HBM推出了I-Cube、H-Cube和X-Cube。I-Cube、H-Cube是2.5D封裝,X-Cube是3D封裝。

I-CUBE S將一塊邏輯芯片與HBM裸片水平放置在一個硅中介層上,實現高算力、高帶寬數據傳輸和低延遲;H-Cube將邏輯芯片與HBM裸片水平放置在一個硅中介層之外結合了ABF基底和HDI基底,在I-CUBE基礎上實現更大的封裝尺寸;X-Cube則是采用芯片垂直堆疊的全3D封裝。

而在近期,三星又宣布將計劃在明年推出先進的3D封裝技術,使用SAINT技術(Samsung Advanced Interconnection Technology,即三星先進互連技術),以更小的尺寸集成高性能芯片所需的內存和處理器。

SAINT技術共分為三大類,一是用于垂直堆疊SRAM和CPU的SAINT S,二是用于應用處理器堆疊的SAINT L,三則是應用于CPU、GPU等處理器和DRAM內存垂直封裝的SAINT D。據相關報道,該技術中SAINT S已經通過了驗證測試,SAINT D和SAINT L的技術驗證將于明年完成。

HBM及其相關封裝技術作為高性能計算領域扮演的重要角色,三星意圖通過SAINT技術在HBM及封裝領域占據主動。

SK海力士應用扇出封裝尋找跳過TSV的降本之路

作為另一家HBM頭部供應商,SK海力士同樣是采用基于TSV的封裝技術來進行產品迭代,現階段SK海力士無疑是HBM類產品的市場領導者,占據了最大的市場份額。

SK海力士在HBM3市場占據領先地位離不開他們開發的MR-MUF(批量回流模制底部填充)技術。這項技術確保了HBM 10萬多個微凸塊互連的優良質量。

此外,該封裝技術還增加了散熱凸塊的數量,同時由于其采用具有高導熱性的模制底部填充材料,具有更加出色的散熱性能。而SK海力士也一直在加強投入研發異構集成和扇出型RDL技術等先進封裝技術。

雖然SK海力士的HBM產品均使用基于TSV的封裝工藝,但相關產能的不足以及成本過高問題一直都存在。以TSV為核心的HBM封裝工藝,在保證良率的前提下成本占比接近30%,比前后道工藝成本占比都要高,是占比最高的部分。

為了解決TSV產能低成本高的困擾,SK海力士除了持續研發主打的基于TSV的封裝工藝之外,也在探索性價比更高的扇出封裝,為下一代DRAM做準備。

SK海力士希望通過扇出封裝這種方式,降低封裝的成本增加I/O接口的數量,而且還能跳過TSV工藝。SK海力士計劃明年推出該方案,并到2025年實現1微米以下或亞微米級水平的扇出型RDL技術。

SK海力士還透露將把下一代后處理技術“混合鍵合”應用于HBM 4產品,進一步縮小間距,同時在芯片堆疊時不使用焊接凸塊,讓封裝在高度上更具優勢。

小結

HBM涉及現在封裝領域的最先進的內存封裝技術,各大廠商在擴充原有技術路線產能的基礎上,都在不斷探索新的路線。在人工智能快速推動HBM需求的同時,HBM也帶動了封裝技術的不斷創新。在算力需求催生存力風口的機遇下,HBM大廠間的競爭從先進封裝就已經開始。

-

HBM

+關注

關注

0文章

374瀏覽量

14708 -

算力

+關注

關注

1文章

936瀏覽量

14750 -

先進封裝

+關注

關注

1文章

379瀏覽量

224

發布評論請先 登錄

相關推薦

算力基礎篇:從零開始了解算力

AI網絡物理層底座: 大算力芯片先進封裝技術

大模型時代的算力需求

摩爾線程張建中:以國產算力助力數智世界,滿足大模型算力需求

產能之外,HBM先進封裝的競爭

算力需求催生存力風口,HBM競爭從先進封裝開始

算力需求催生存力風口,HBM競爭從先進封裝開始

評論