理論白癡的我寫這個壓力有點小大,水平很有限,初學者看看,然后再去找對應論文看正規的說法和解釋,別被我誤導,老司機跳過。

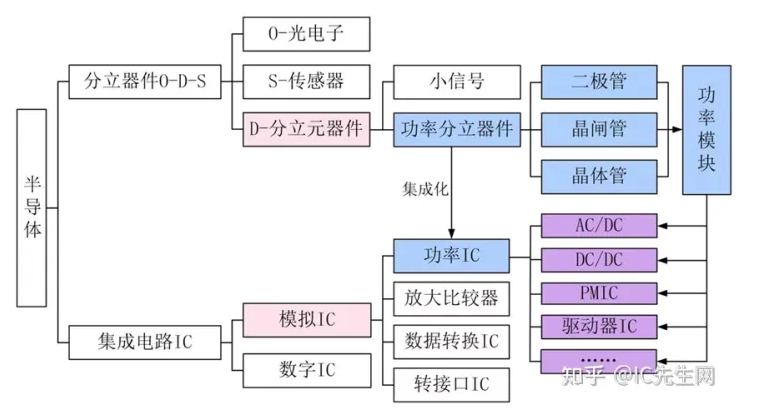

1、功率半導體器件簡介

功率半導體器件,以前也被稱為電力電子器件,簡單來說,就是進行功率處理的,具有處理高電壓,大電流能力的半導體器件。典型的功率處理,包括變頻、變壓、變流、功率管理等等。早期的功率半導體器件:大功率二極管、晶閘管等等,主要用于工業和電力系統(正因如此,早期才被稱為電力電子器件)后來,隨著以功率MOSFET器件為代表的新型功率半導體器件的迅速發展,現在功率半導體器件已經非常廣泛,在計算機、通行、消費電子、汽車電子 為代表的4C行業(computer、communication、consumer electronics、cartronics)。在大多數情況下,它是被作為開關使用(switch),開關,簡單的說,就是用來控制電流的通過和截斷。那么,一個理想的開關,應該具有兩個基本的特性:電流通過的時候,這個理想開關兩端的電壓降是零;電流截斷的時候,這個理想開關兩端可以承受的電壓可以是任意大小,也就是0~無窮大。

因此,功率半導體器件的研究和發展,就是圍繞著這個目標不斷前進的。現在的功率半導體器件,已經具有很好的性能了,在要求的電壓電流處理范圍內,可以接近一個比較理想的開關。舉幾個例子,功率二極管,晶閘管,還有功率BJT(就是功率雙極型晶體管)這些都是第一代產品了,比較老的了,第二代是以功率MOSFET為代表的新型功率半導體器件,如VDMOS、LDMOS,以及IGBT。VDMOS 即(vertical double-diffusion MOSFET)是縱向器件,柵和源電極在上面,漏極在下面,多用于分立器件;LDMOS 即(Lateraldouble-diffusion MOSFET),是橫向器件,其三個電極(源極柵極漏極)均在硅片上表面,易于集成,多用于功率集成電路領域。IGBT 即(InsulatedGate Bipolar Transistor 絕緣柵雙極型晶體管),可以看作是功率MOS和功率BJT的混合型新器件。(這一段是摘抄與修改)

2、NMOS襯偏效應解決的方法

在源端加P+,引出電極和源級短接,保持源和襯底電位一致,消除襯偏效應對閾值電壓Vth的影響。直接讓P-body和源級相連理論上也行,但輕摻雜的P-body接觸電阻更大,所以采用源區加P+的方法來降低接觸電阻。這這只是解決方法之一,不是唯一。

3、淺談MOS

個人覺得MOS是個很重要的概念,知道一些基本原理才能進行學術研究,所以MOS的特性一定要掌握到位。

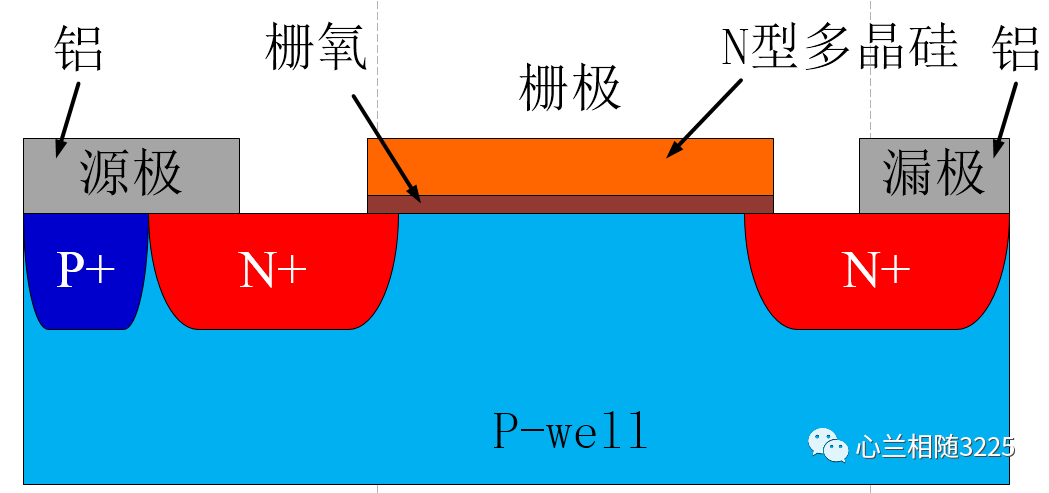

下圖是一個典型的NMOS示意圖,源極下方P+是為了消除襯偏效應的影響,同時也為了降低接觸電阻。柵氧一般很薄很薄,而且柵氧要求的質量很高,氧化層的形成一般有干氧氧化和濕氧氧化,柵氧一般(不是所有)采用干氧氧化,干氧雖然慢,但質量高。柵氧上面是多晶硅,多晶硅還需要摻入五價的元素(如磷,砷)形成N型多晶硅。為什么不摻硼這樣的元素形成P型多晶硅,一種說法是柵氧(SiO2)具有吸硼排磷的特性,假如多晶硅里有硼元素,那么就可能會進入柵氧,柵氧里便會摻入雜質,影響柵氧質量,甚至會出現我們極其不希望看到的柵電流。對了,個人覺得,在流片的時候,記得將靠近場氧等氧化層的P-區增大一下表面濃度哦,不然吸硼排磷,發現P-body最上面竟然不是P-,而是漂移區,硼都被氧化層吸走了,這就哭了,流片成本那么高,emmm畢竟流片良率問題太重要了。

高壓排斥空穴,低壓吸引電子這是大家都認同的。柵極加高壓,靠近柵氧的P-well區空穴便會被排斥開,留下不可移動的硼離子,這些陰離子形成的便是反型層,對于電子來說是低阻區,這就是所謂的溝道,而且,柵壓越大溝道越寬溝道電阻就越小。

當柵氧較厚時,pwell濃度較大時,反型較困難,即需要更大的柵壓才能形成反型層,也就是閾值電壓會增大,而且閾值電壓也跟溫度有關系哦,溫度升高,閾值電壓是降低的,因為Vth的表達式中有一項是與表面勢有關的,而表面勢與溫度的是正比關系,即溫度升高表面勢增大。在閾值電壓的表達式中,Vth=Vth0+γ((Φ-Vbs)^0.5-Φ^0.5),顯然第二項是負值,也就是說表面勢Φ增大Vth減小。

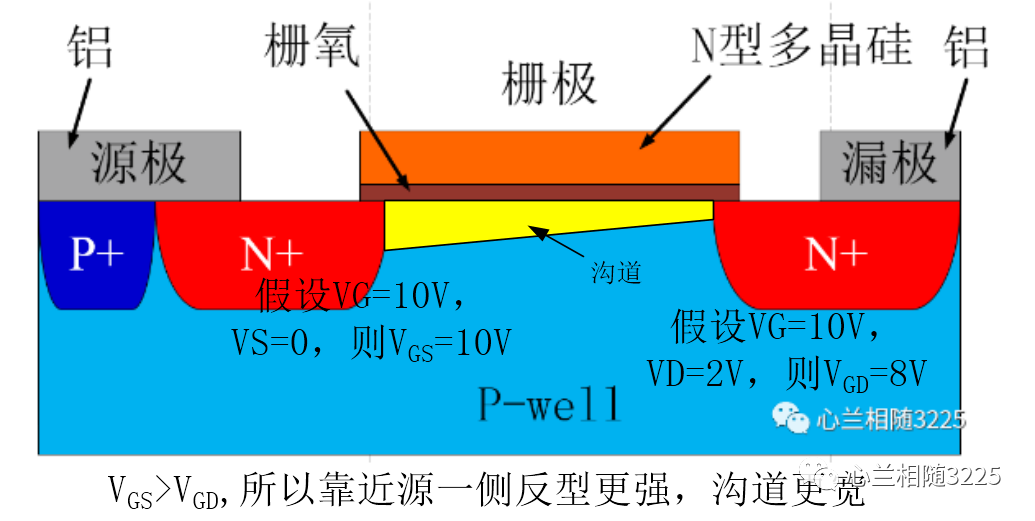

當反型層形成了,也就有了電子溝道,一旦漏極電勢大于源極,電子就會從源極經過溝道到達漏極。

下面談談線性電流和飽和電流,以及什么叫溝道夾斷。

當溝道形成,漏極電壓不大時,這個時候MOS的導通基本是受溝道電阻的影響,所以呈現的是線性區變化,

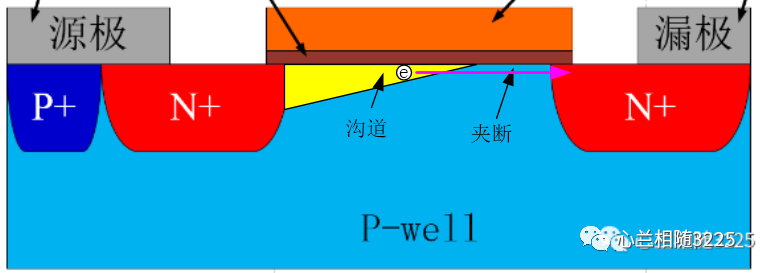

隨著漏壓繼續增加,靠近漏的溝道消失,形成夾斷,一方面,不是所有的電子都可以通過夾斷區,只有速度高的電子才能在電場作用下強行穿過夾斷區,另一方面,電子也是有飽和速度的,速度達到一定值不再增加,這就是為什么漏壓增加了,電流卻飽和不增加的原因。在功率器件,比如VDMOS中,飽和區的電流曲線不是平的,而是上翹的,是因為兩個P-body之間N-drift區即JFET區,更多的漏電勢落在了JFET電阻上,所以在溝道夾斷以后還是會電流上翹的現象,也就是準飽和效應。準飽和效應我涉獵較少,對此感興趣的多去查查文獻哦。

4、硬擊穿和軟擊穿

擊穿分為硬擊穿和軟擊穿,如果BV曲線突然上升,很陡,就稱為硬擊穿,如果BV曲線上升很緩,稱為軟擊穿。

5、查找專利去哪個網站?

查國內專利選佰騰網,soopat,查國外專利選freepatent online。

6、什么是閂鎖效應,即latch-up?

IGBT正常導通應該是柵下溝道開啟,電子從發射極出發,經過溝道,進入漂移區,到達并聚集在集電極下方,當集電極與集電極下方電位大于PN結的正向導通壓降,集電極P+和N-buffer構成的PN結就會開啟,器件不再只有電子電流,而且有空穴電流,進入雙極型模式,發生電導調制,即大注入(少子數量大于等于多子數量),電流能力大大增強。當柵壓降低,讓溝道下方電子反型層消失,電子電流就會被切斷,IGBT關斷。

但是當漂移區的空穴經源區P-body、源區P+流到源極時,由于P-body區電阻的存在,在源區P-body和源區N+可能產生一定的壓降,當該壓降大于由源區P-body和源區N+組成的PN結的正向導通壓降時,由源區N+、源區P-body和N-drift構成的寄生NPN就會開啟,此時柵對于溝道電流就失去了控制,無法通過柵壓讓器件關斷,這就是閂鎖效應,一般發生在IGBT內,示意圖如下。(我自己口述解釋的,很不嚴謹,意思大概懂即可)

工藝上為防正向導通期間寄生NPN開啟的方法是增大P-body的濃度,我們知道,摻雜越多,載流子就越多,電阻就越小,P-body電阻小,那么較大電流流過時,就很難在發射極N+和P-body之間形成0.7伏的正向導通壓降,發射極P-body/N+結就較難開啟,可以達到防閂鎖的目的,但是這樣會導致閾值電壓的增大。

7、溫度升高,PN結擊穿電壓會怎樣變化?

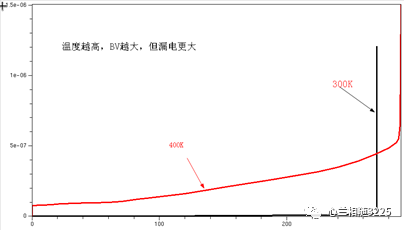

溫度升高,晶格振動劇烈,載流子遷移率因受阻而下降,故相同電壓下,溫度高的,速率更低,需要更大的電壓才能使得載流子達到雪崩擊穿的速率,因此溫度升高,擊穿電壓是變大的,但是溫度升高,本征激發的載流子數目也在變多,所以漏電也會增加,仿真結果如下。

8、PN+結的BV和P+N結的BV(breakdown voltage,擊穿電壓)有何差別?

對于PN+結來說,空穴是更少的少子,對于P+N結,電子是更少的少子,空穴遷移率小于電子,所以要想達到雪崩速率,PN+需要更大的電壓,PN+的BV高些,仿真證明如下。

9、SOI技術的優缺點

SOI就是有Psub,BOX和Ndrift的,Si基就是直接在Psub上做N漂移區的。

SOI全稱:silicon on insulator,絕緣體上硅

SOI優點:減小了寄生電容,降低了漏電,消除了閂鎖效應,抑制了襯底脈沖電流的干擾,與現有的硅工藝兼容,可以減少13-20%的工序。

SOI缺點:成本高,是Si的六倍以上,散熱困難。

10、RC-IGBT產生snapback原因

對于一般的IGBT,如上面第5條的圖所示, IGBT不存在體二極管,當器件關斷的時候,漂移區空穴可以通過發射極P+抽取,但是電子就慘了,沒有路徑讓它回家,集電極的P+對于電子而言是高阻區,于是電子就只能被漂移區內的空穴慢慢復合掉。復合的速度哪能比得上抽取的快,所以IGBT最嚴重的問題就是關斷速度賊雞兒慢,這就導致了IGBT只能用于大功率,可惜在高頻領域無用武之地。

為了解決這一頭疼問題,必須要讓IGBT關斷期間長長的拖尾電流消失,怎么辦呢?最簡單的就是也給電子一條回家的路徑,那就是在集電極側加一個N+區同時與集電極連接起來,這樣電子的抽取就變快了。IGBT發射極(E)也被叫陰極,集電極(C)也被叫陽極。

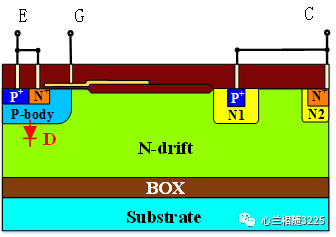

下圖是RC-IGBT,因為陽極多了個N+區用來提供電子抽取路徑,加快IGBT關斷的。正常的IGBT是左邊低壓右邊高壓,電流從右向左。但是加了陽極N+之后,左邊可以接高壓,右邊可以接低壓,體二極管可以導通,電流從左向右,實現了逆向導通的功能,所以叫逆導,reverse conduction,這是RC的來歷。由于陽極P/N1結被短路,RC-IGBT 正向導通初期(發生電壓折回之前)體內只有電子電流,陽極P+區不能向漂移區注入空穴,漂移區因此也沒有電導調制效應存在。也就是說,RC-IGBT發生電壓折回之前的導通電阻實際非常大,其值接近于相同結構尺寸下VDMOS的導通電阻。當陽極P+和N1下方電位大于陽極P/N1結的內建電勢時,陽極P+開始向漂移區注入空穴,使漂移區發生電導調制效應,降低漂移區的電阻。這會導致 RC-IGBT 的電流增大,使 N1下方的電勢進一步下降,結果會使漂移區有更多的空穴注入和更充分電導調制效應,這樣就會形成電流不斷增大而電阻不斷減小的正反饋過程。這個過程反映到輸出特性曲線的結果,即為 RC-IGBT 的電流增大同時電壓減小的電壓折回現象。

簡單來講就是MOS小電流模式切換到BJT大電流模式需要經歷突變這個過程。snapback現象的存在是不希望看到的,因為一個電壓對應值兩個電流,如果兩個玩意并聯,電壓是相同的,可能會存在一個流過電流大一個流過電流小,流過電流大的阻礙就變小,就會導致電流越來越大,可能會引起器件損壞。工程上一般是增大陽極N+和P+之間的距離,這樣可以利用N+和P+之間漂移區電阻來形成壓降,讓N1下方電勢早點比陽極電位小0.7V(假設PN結開啟電壓是0.7V),但這樣又太費面積,學術上的研究一般是通過讓電子繞路增大上述電阻,這方面論文太多了,感興趣去研究研究呢。

11、MOS二級效應有哪些?

溝道長度調制,背柵效應,亞閾值效應。

溝道長度調制效應:溝道夾斷以后,繼續增大VDS,會導致夾斷點往源極移動,溝道有效長度減小,電阻減小,ID增大

背柵效應:MOS管的閾值電壓將隨其源極和襯底之間電位的不同而發生變化。

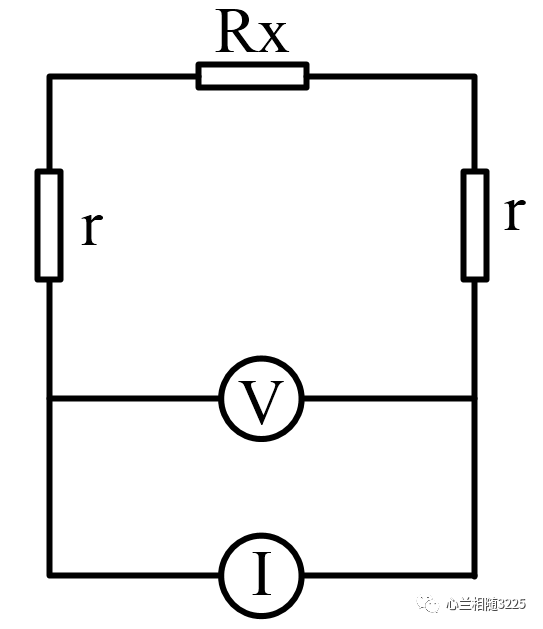

12、雙線法測電阻與四線法測電阻

電阻測試通常原理是恒流測壓,測量儀器產生恒定數值的測量電流I,通過兩根測量引線分別接觸待測電阻Rx兩端,當電流I流過Rx時,測得Rx兩端電壓為Ux,Rx=Ux/I,但是引線也是有電阻的,尤其在測量微小電阻時,引線上的電阻不能忽略不計,實際Rx=(Ux+2Ur)/I。

采用四線法測量時,由于四條引線分別形成電壓回路和電流回路,電壓測量回路的阻抗很大,流過的電流可以忽略,Rx=U/I是更加精確的,所以四線法測電阻被廣泛采用。

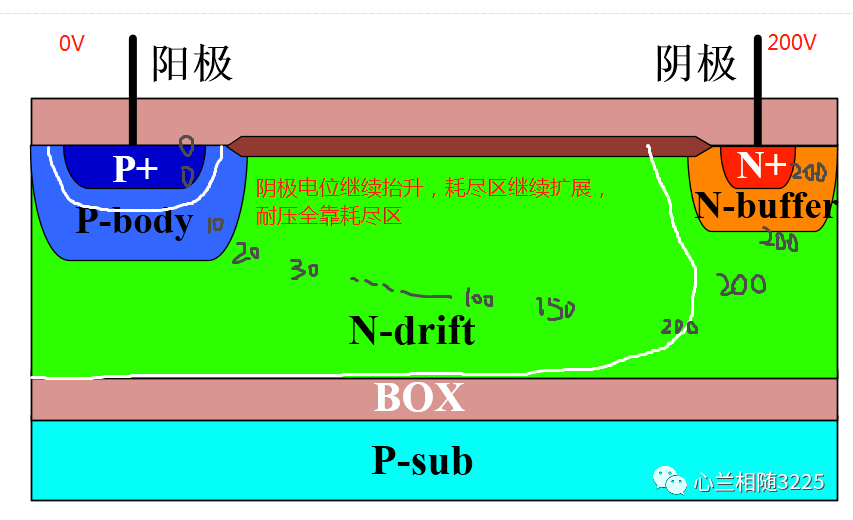

13、二極管的耐壓過程

功率PiN二極管反偏時的反向擊穿電壓VBR主要是結的低摻雜一側的雜質濃度決定。考慮一般的非穿通情況,本征i區的寬度比空間電荷區的寬度要寬,二極管的擊穿電壓可以由下式來表示:

其中:EBR為臨界擊穿電場強度,ε0為自由空間介電常數, εr為相對介電常數,ND為施主濃度。根據上式,我們可以看出,要想使二極管具有較高的擊穿電壓 VBR,硅片初始材料應具有較低的施主雜質濃度 ND,也就是說要具有較高的電阻率。為了能夠讓空間電荷區在反偏時有足夠的擴展空間,FRD 的漂移區還必須具有比較大的厚度。但對于低正向壓降的要求來說,必須保證載流子具有較長的壽命以保證在正向大注時實現高度的電導調制。因此高反向擊穿電壓和低正向壓降對高阻層的要求是相互矛盾的,在器件設計時要考慮到。下面我只是想把耗盡過程表達清楚,耗盡線是我隨便瞎畫的。個人認為PN結的耐壓過程很重要,初學者一定要去查閱資料文獻將其搞懂。

圖中黑色的數字,代表各位置的大致電位,這里想表達的是,電勢只會在耗盡區進行降落,耗盡區以外的區域電勢不變,稱為中性區,換句話說,只有耗盡層的展寬程度才是耐壓大小的決定性因素。所以對于高壓應用的場合,普遍采用N漂移區來提升器件的耐壓特性。

器件提前擊穿原因有很多,比如某處電場太強(通常在鳥嘴處,溝槽柵拐角等這些曲率較小的地方),超過硅基的臨界擊穿電場(一般認為25萬-30萬V/m)。

理論這種東西基本上全靠自己去悟,沒有誰可以指導誰,也不是教授博士說的就一定是對的,論文都有錯的,比如很多論文里的NMOS的N說成N-type,但嚴格來講是指N-channel,從來沒有N-type這種說法。公眾號里寫的肯定有錯誤的地方,但我覺得錯不可怕,如果看一個公眾號可以提起你對這一方向的興趣,從而好像找到了自己的方向,開始去搜索研究論文,激情于仿真,測試等等,我想這個公眾號就是成功的。

-

二極管

+關注

關注

147文章

9581瀏覽量

165954 -

MOSFET

+關注

關注

146文章

7101瀏覽量

212773 -

晶閘管

+關注

關注

35文章

1098瀏覽量

77099 -

BJT

+關注

關注

0文章

222瀏覽量

18122 -

功率半導體

+關注

關注

22文章

1131瀏覽量

42889

發布評論請先 登錄

相關推薦

功率半導體器件的定義及分類

什么是基于SiC和GaN的功率半導體器件?

淺談功率半導體器件與普通半導體器件的區別

功率半導體器件學習筆記(1)

功率半導體器件學習筆記(1)

評論