事故現場

先貼一下代碼的簡版:

localparam S_IDLE = 4'd0;

localparam S_HEAD = 4'd1;

localparam S_PAYLOAD = 4'd2;

localparam S_TAIL = 4'd3;

localparam S_ERROR = 4'd4;

reg [3:0]status, nx_status;

always @(posedge clk_100m or negedge rst_spt_n)begin

if(!rst_spt_n) status <= S_IDLE;

else status <= nx_status;

end

always @* begin

case(status)

S_IDLE: ...

S_HEAD: ...

S_PAYLOAD: ...

S_TAIL: ...

S_ERROR: ...

default: nx_status = status;

endcase

end

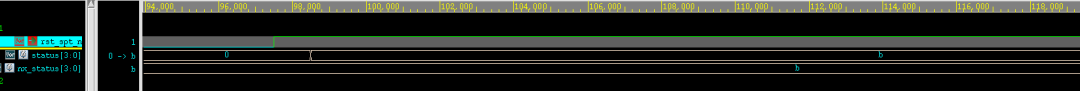

狀態機本身很簡單,default也寫了,然后進行仿真時看到了這樣的波形:

nx_status仿真初始的值為4'hb,而后導致status的值也為4'hb,始終無法回到IDLE狀態,整個電路的功能也無法正常開展。

事故分析

這個問題得以暴露要感謝在驗證環境中打開了initreg功能:

CMP_OPTIONS += +vcs+initreg+random

RUN_OPTIONS += +vcs+initreg+$(SEED)

通過這樣的配置使得reg型的數值在仿真開始時被賦值為隨機數。該bug就是由于nx_status被賦值為狀態之外的隨機數而發現的。

在代碼中,nx_status沒有任何位置被進行“復位”,當然了因為nx_status本身不是寄存器也就不存在復位的問題,不過狀態機的alway@*中的處理是有問題的,這導致nx_status一旦跑“飛”了,status下一拍會更新為nx_status的值,那么整個狀態機將不可恢復。

事故解決

修改狀態機的寫法為:

always @* begin

case(status)

S_IDLE: ...

S_HEAD: ...

S_PAYLOAD: ...

S_TAIL: ...

S_ERROR: ...

default: nx_status = S_IDLE;

endcase

end

或者

always @* begin

nx_status = S_IDLE;

case(status)

S_IDLE: ...

S_HEAD: ...

S_PAYLOAD: ...

S_TAIL: ...

S_ERROR: ...

default: nx_status = status;

endcase

end

重新仿真后波形正確:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5317瀏覽量

120006 -

仿真器

+關注

關注

14文章

1016瀏覽量

83635 -

狀態機

+關注

關注

2文章

492瀏覽量

27478

發布評論請先 登錄

相關推薦

Verilog狀態機+設計實例

在verilog中狀態機的一種很常用的邏輯結構,學習和理解狀態機的運行規律能夠幫助我們更好地書寫代碼,同時作為一種思想方法,在別的代碼設計中也會有所幫助。 一、簡介 在使用過程中我們常說

什么是狀態機?狀態機的三種實現方法

文章目錄1、什么是狀態機?2、狀態機編程的優點(1)提高CPU使用效率(2) 邏輯完備性(3)程序結構清晰3、狀態機的三種實現方法switch—case 法表格驅動法函數指針法小節摘要:不知道大家

發表于 12-22 06:51

如何寫好狀態機

如何寫好狀態機:狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的邏輯功底,所以許多公司的硬件和邏輯工程師面試中,狀態機設計幾乎是必選題目。本章在引入

發表于 06-14 19:24

?97次下載

什么是狀態機 狀態機的描述三種方法

狀態機 1、狀態機是許多數字系統的核心部件,是一類重要的時序邏輯電路。通常包括三個部分:一是下一個狀態的邏輯電路,二是存儲狀態機當前狀態的時

什么是狀態機?狀態機5要素

玩單片機還可以,各個外設也都會驅動,但是如果讓你完整的寫一套代碼時,卻無邏輯與框架可言。這說明編程還處于比較低的水平,你需要學會一種好的編程框架或者一種編程思想!比如模塊化編程、狀態機編程、分層思想

狀態模式(狀態機)

以前寫狀態機,比較常用的方式是用 if-else 或 switch-case,高級的一點是函數指針列表。最近,看了一文章《c語言設計模式–狀態模式(狀態機)》(來源:embed linux

發表于 12-16 16:53

?9次下載

什么是狀態機?狀態機的種類與實現

狀態機,又稱有限狀態機(Finite State Machine,FSM)或米利狀態機(Mealy Machine),是一種描述系統狀態變化的模型。在芯片設計中,

狀態機怎么上來就錯了?怎么解決?

狀態機怎么上來就錯了?怎么解決?

評論