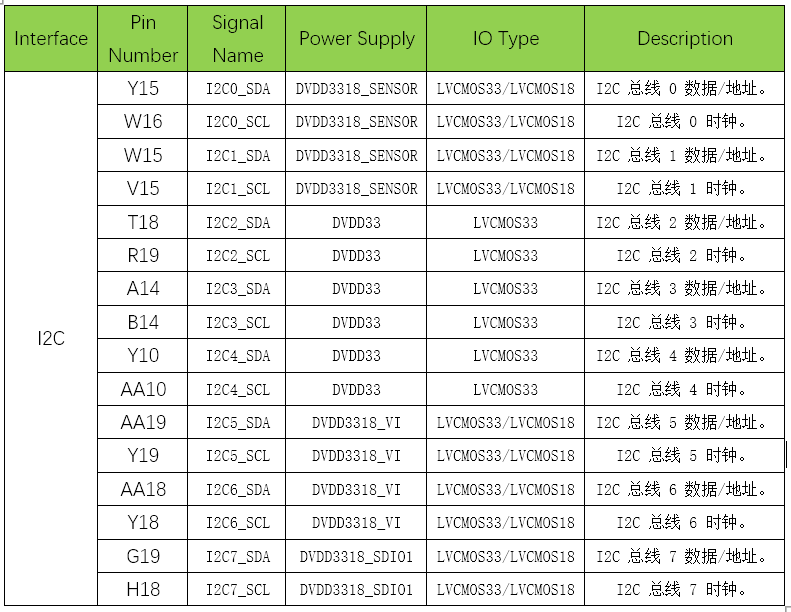

上一期我們介紹了 【Hi3566V100 I2C 硬件設計要點】,本期將繼續給大家推出海思硬件設計系列:Hi3566V100 SDIO 硬件設計要點。

一、前言

Hi3566V100 是一顆面向車載行車記錄儀、駕駛員狀態監控等領域推出的高性能、低功耗的 Camera SoC。Hi3566V100 內核為 Cortex A7 MP2 @792MHz,支持雙路 1080p@30fps H.265/H.264 編碼。

二、Hi3566V100 SDIO 原理設計思路

Hi3566V100 有 2 個SDIO3.0 接口,其中 SDIO0 支持 SDIO3.0、SDXC 存儲卡;

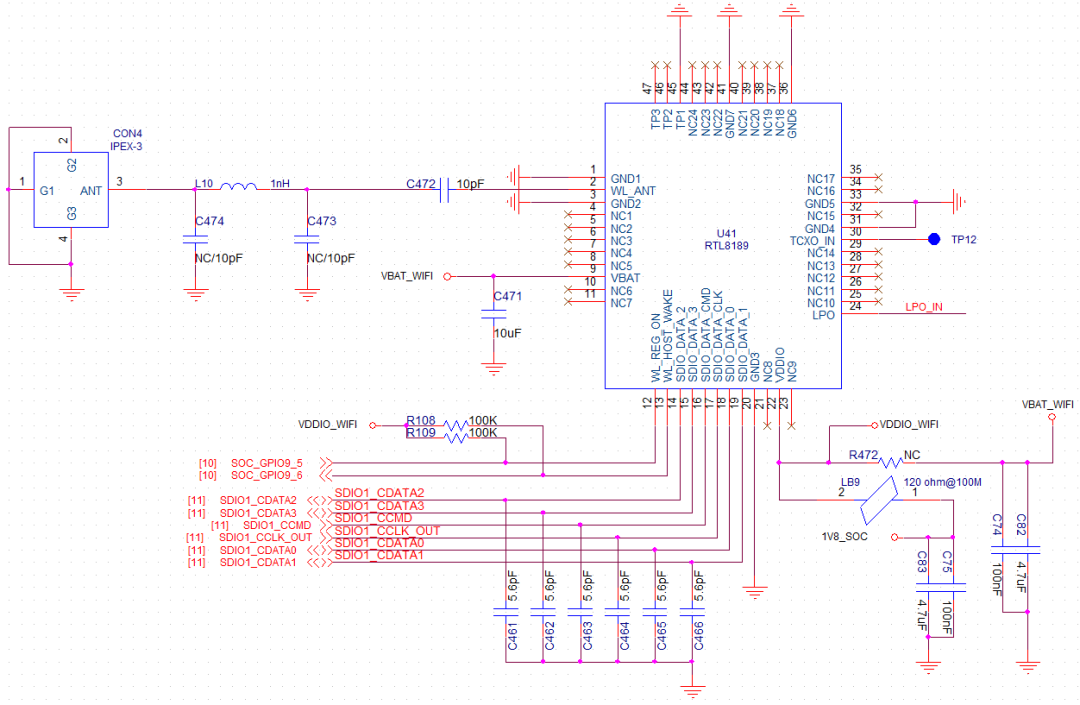

SDIO1 只支持對接 Wi-Fi,接口支持 1.8V 和 3.3V 電平;

SDIO0_CARD_DETECT 和 SDIO0_CARD_POWER_EN 只支持 3.3V 電平;

SDIO0 數據線電壓域是 SDIO0_VOUT,自動識別 1.8V/3.3V,支持 1.8V/3.3V SD 卡。

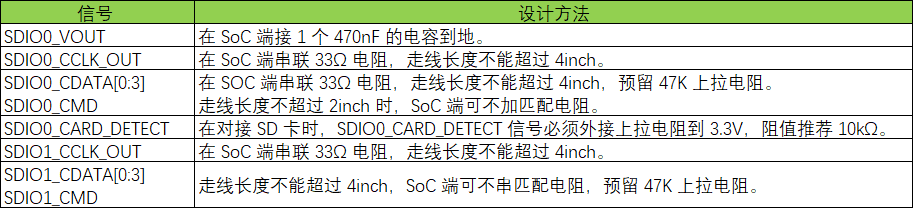

圖 1 SDIO 信號設計要求

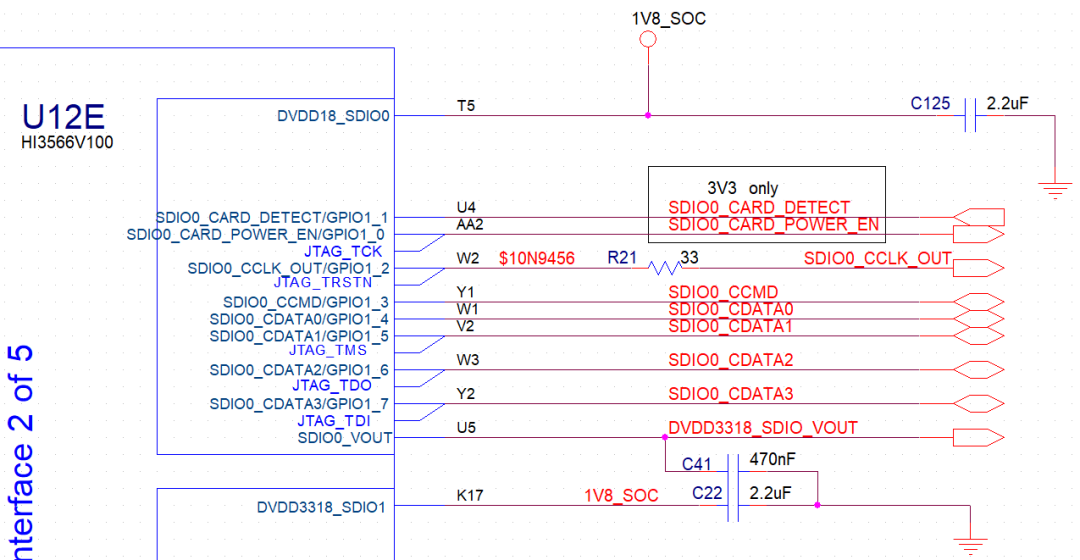

圖 2 SDIO0 的 SoC 端原理圖

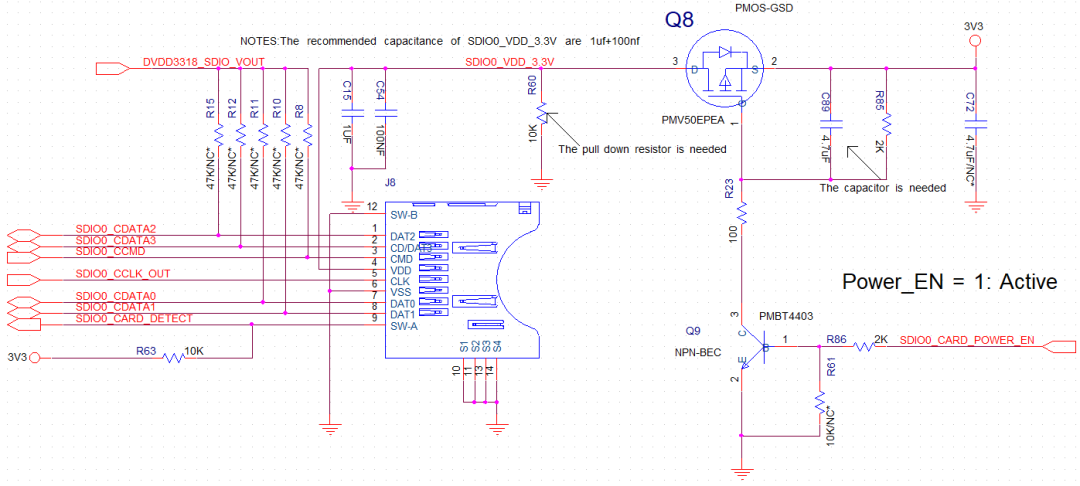

圖 3 SDIO0 的 SD 卡端原理圖

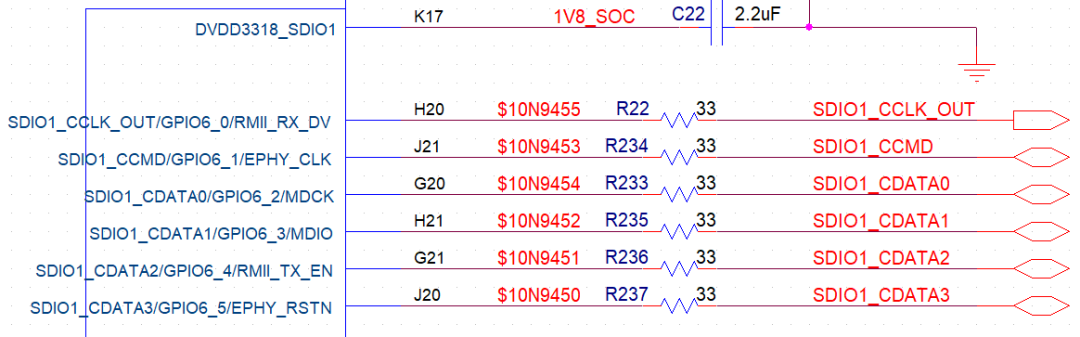

圖 4 SDIO1 的 SoC 端原理圖

圖 5 SDIO1 的 Wi-Fi 端原理圖

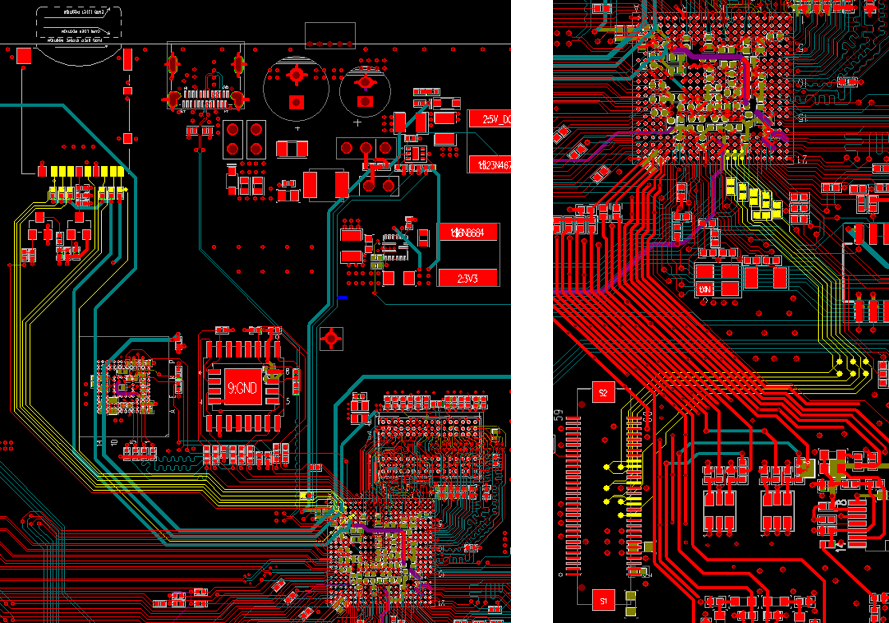

三、PCB 設計思路

- 相鄰信號走線間距保證“3W”原則。

- SDIO0/1_CDATA[0:3]、SDIO0/1_CCMD 的線長以 SDIO0/1_CCLK_OUT 的線長為基準,偏差控制在 ±500mil。

- 如果 SDIO0 需要支持 SDXC 卡,那么 SDIO0 的數據信號必須以 GND 為參考平面,并保持信號參考平面完整。

圖 6 SDIO0 PCB 走線 圖 7 SDIO1 PCB 走線

以上便是 Hi3566V100 SDIO 硬件設計要點的全部內容。

-

接口

+關注

關注

33文章

8150瀏覽量

149659 -

硬件設計

+關注

關注

18文章

356瀏覽量

44436 -

海思

+關注

關注

41文章

435瀏覽量

115258 -

SDIO

+關注

關注

2文章

65瀏覽量

19227

發布評論請先 登錄

相關推薦

海思Hi3566V100 I2C硬件設計要點

海思Hi3566V100 SDIO硬件設計要點

海思Hi3566V100 SDIO硬件設計要點

評論