SJA1105P/Q/R/S 系列是 NXP 推出的一款 5 端口車載以太網(wǎng)交換機(jī),支持IEEE 音視頻橋接(AVB)和時(shí)間敏感網(wǎng)絡(luò)(TSN)標(biāo)準(zhǔn)。這五個(gè)端口中的每一個(gè)都可以單獨(dú)配置為 10/100/1000 Mbit/s 運(yùn)行。

芯片介紹

1.1 概述

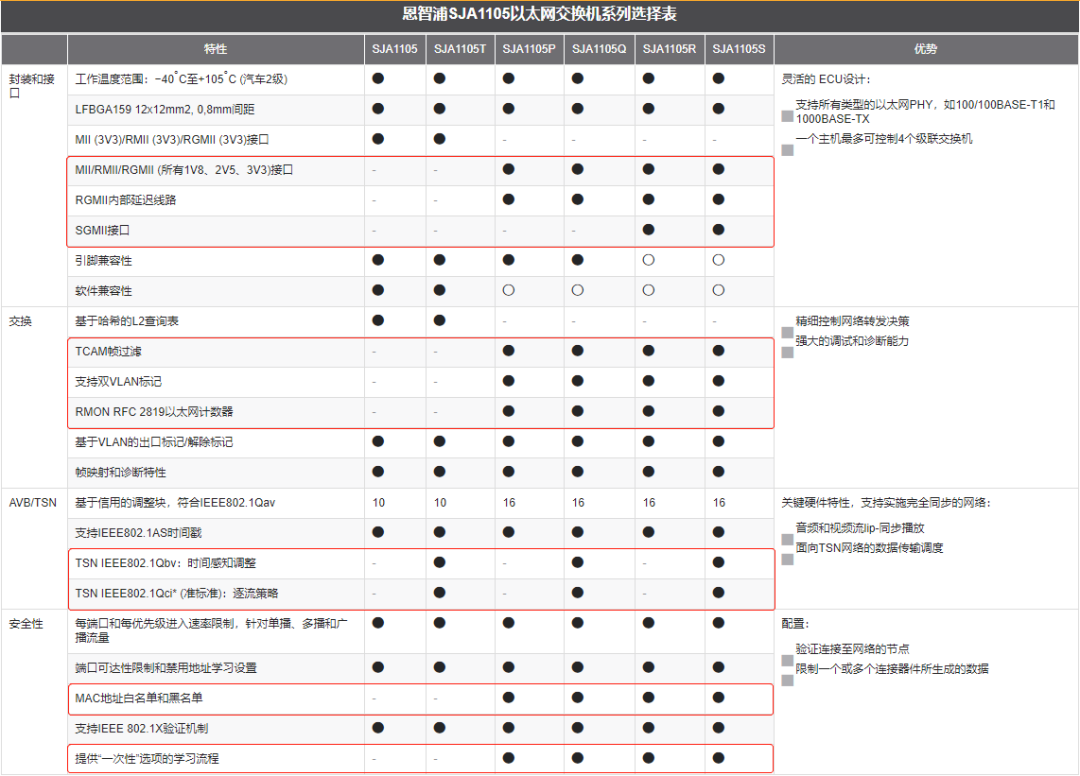

SJA1105PEL/QEL/REL/SEL 系列是一款汽車千兆以太網(wǎng)交換機(jī),相較于 SJA1105EL/TEL,其擴(kuò)展了交換機(jī)的功能,改進(jìn)了安全特性,擴(kuò)展了接口選項(xiàng),具體區(qū)別如圖:

SJA1105P/Q/R/S 系列中 P/Q 版本不帶 SGMII 接口(本文設(shè)計(jì)指導(dǎo)基于 P/Q 版本),具體區(qū)別如下圖:

1.2 基本特征

① 基于幀頭的安全特性

a. 根據(jù)具體幀頭值劃分的幀黑名單和白名單

b. 防止轉(zhuǎn)發(fā)錯(cuò)誤或惡意數(shù)據(jù)

c. 支持實(shí)施防火墻應(yīng)用

② 5 個(gè)可單獨(dú)配置的端口,帶有擴(kuò)展 IO 選項(xiàng)

a. 廣泛的數(shù)據(jù)傳輸速率,可優(yōu)化 PCB 設(shè)計(jì)

b. SGMII 選項(xiàng)用于 EMC 友好型千兆位接口

c. 可靈活地連接至 10/100/1000 BASE-T1/TX 光 PHY

a. 實(shí)施完全同步的網(wǎng)絡(luò)

b. 支持汽車領(lǐng)域大多數(shù) AVB /TSN 特性

c. 由恩智浦或第三方軟件廠商提供的 AVB 軟件

1.3 封裝及引腳信息

① 封裝: SJA1105P/Q/R/S 系列封裝均為 LFBGA159(SOT1427-1),且兼容 SJA1105、SJA1105T,具體封裝參數(shù)如圖:

② 引腳定義:

硬件設(shè)計(jì)指南

1.1 電源設(shè)計(jì)

① VDD_CORE、VDDA_OSC、VDDA_PLL 的電源輸入拓?fù)淙鐖D所示:(建議在每一路電源上增加一個(gè)鐵氧體磁珠及兩個(gè)電容組成一個(gè) PI 型濾波)

② VDDIO_MIIx 的電源輸入拓?fù)淙鐖D所示:(建議在每一路電源上增加一個(gè)鐵氧體磁珠及兩個(gè)電容組成一個(gè) PI 型濾波)

所有 xMII-port 端口需根據(jù)其模式配置提供相應(yīng)的電源(1.8V/2.5V/3.3V)。

沒有使用的端口,其 VDDIO_MIIx 電源可以直接連接到地面,以節(jié)省電力。也可以選擇在核心電源處于活動(dòng)狀態(tài)時(shí)動(dòng)態(tài)關(guān)閉各個(gè)端口的電源。但是 VDDIO_MIIx 不能懸空。

③ VDDIO_HOST、VDDIO_CLO 的電源輸入拓?fù)淙鐖D所示:(建議在每一路電源上增加一個(gè)鐵氧體磁珠及兩個(gè)電容組成一個(gè) PI 型濾波)

VDDIO_HOST 和 VDDIO_CLO 都可以接受 1.8 V、2.5 V 或 3.3 V 的電源。SPI、JTAG 和PTP_CLK 接口通過 VDDIO_HOST 提供。25 MHz 時(shí)鐘輸出、CLK_OUT 由 VDDIO_CLO 提供。獨(dú)立的供電引腳和各種電壓搭配為不同的接口電壓兼容提供了靈活性。

重要的是,提供 VDDIO_HOST 的域也提供給了附加的微處理器的 SPI 接口。這保證了SDO 和 SDI 引腳上的電壓是從 VDD_HOST 派生的。在任何情況下,需確保 VDDIO_HOST 上電之前 SPI 的輸入引腳(SDI, CS)沒有電平。

2.2 接口設(shè)計(jì)

① MII/RMII/RGMII 接口

未使用的 xMII 接口應(yīng)該有固定狀態(tài),輸入端不能懸空,特別是所有 RX 輸入都應(yīng)連接到 GND。或者也可以通過內(nèi)部上/下拉(見 ACU 寄存器)來定義引腳狀態(tài)。

輸出端(TX pins)可以懸空。

MII/RMII/RGMII 接口設(shè)計(jì)要求:

a. 單端 50 Ω 阻抗控制。

b. 組間等長(zhǎng)控制

c. 建議將時(shí)鐘和數(shù)據(jù)信號(hào)走內(nèi)層,以減少輻射發(fā)射。

② SPI 接口

SJA1105PQRS 通過 SPI 連接到主機(jī)控制器上進(jìn)行初始配置和時(shí)鐘調(diào)整,并進(jìn)行一般管理,其工作在從機(jī)模式。SPI 接口可以在 3.3 V、2.5 V 或 1.8 V 的電源電壓下工作,這取決于 VDDIO_HOST 電源。SPI 的時(shí)鐘最大支持到 25 MHz。

SPI 設(shè)計(jì)要求:

a. 單端 50 Ω 阻抗控制。

b. 推薦組間等長(zhǎng)(SCK,SDI,SDO,SS_N)

2.3 時(shí)鐘設(shè)計(jì)

SJA1105PQRS 支持晶體輸入(振蕩模式)和外部時(shí)鐘輸入(時(shí)鐘模式)作為參考時(shí)鐘。

① 晶體模式

選擇晶體和負(fù)載電容的基本原則是確保其振蕩頻率穩(wěn)定在 25mhz±50ppm 的容差范圍內(nèi)(針對(duì) RMII 和 RGMII),如果所有端口都工作在 MII 模式,則為 25mhz±100ppm。

建議在默認(rèn)配置下使用兩個(gè) 10pf 陶瓷電容器。電容值可能隨晶振規(guī)格和板級(jí)測(cè)試結(jié)果而變化。當(dāng)晶振被用作時(shí)鐘源時(shí),需要盡可能的將晶振靠近 SJA1105PQRS 放置以減小 EMI 影響。

② 時(shí)鐘模式

SJA1105PQRS 支持 AC-coupled(沒有外部電壓偏置)的外部 25MHz 時(shí)鐘輸入至 OSC_IN 引腳,此時(shí) OSC_OUT 引腳保持懸空,這種應(yīng)用下需要串接 100 pF 的電容。

注意 OSC_IN 的輸入電壓不能超過 1.2V 的峰峰值(VDDA_OSC)。如果使用超過 1.2V 峰峰值的數(shù)字時(shí)鐘源,建議使用電阻進(jìn)行分壓后再輸入,如圖所示:

2.4 典型參考設(shè)計(jì)

如下圖所示為兩顆 TJA1102 與一顆 SJA1105P/Q 通過 MII/RMII 連接的系統(tǒng)示意圖,其中主控與 SJA1105P/Q 通過 RGMII 接口連接。

為了與 TJA1102 兼容,必須選擇 3.3 V 的 VDDIO_MIIx 電源。其他接口的電源則根據(jù)主控系統(tǒng)電平?jīng)Q定對(duì)應(yīng)的電壓大小。

2.5 PCB Layout 指導(dǎo)

在去耦電容的布置設(shè)計(jì)中,應(yīng)注意寄生電感和寄生電阻對(duì)去耦電容諧振頻率的影響,從而影響去耦性能。

盡量減小寄生電感和電阻:

a. 減少去耦電容至電源和地引腳之間的走線長(zhǎng)度。

b. 增加走線寬度。

c. 小電容盡量靠近芯片引腳,因?yàn)橹C振頻率高的小電容更容易受到寄生電感和電阻的影響。

以上就是關(guān)于 SJA1005x 的硬件設(shè)計(jì)的全部?jī)?nèi)容,接下來我們也會(huì)不斷推出關(guān)于ADAS 域控制器硬件設(shè)計(jì)的開發(fā)博文。

-

NXP

+關(guān)注

關(guān)注

60文章

1243瀏覽量

181482 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5288瀏覽量

169653 -

交換機(jī)

+關(guān)注

關(guān)注

20文章

2572瀏覽量

98252 -

端口

+關(guān)注

關(guān)注

4文章

916瀏覽量

31856 -

車載以太網(wǎng)

+關(guān)注

關(guān)注

18文章

209瀏覽量

22812

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

以太網(wǎng)交換機(jī)的測(cè)試

如何配置以太網(wǎng)交換機(jī)

什么是以太網(wǎng)交換機(jī)/ATM交換機(jī)

工業(yè)以太網(wǎng)交換機(jī)簡(jiǎn)介及其與普通交換機(jī)的區(qū)別介紹

工業(yè)以太網(wǎng)交換機(jī)和普通交換機(jī)的區(qū)別

以太網(wǎng)交換機(jī)的基本概念,具有什么特點(diǎn)

以太網(wǎng)交換機(jī)是什么 以太網(wǎng)交換機(jī)的使用方法

以太網(wǎng)交換機(jī)是什么?

以太網(wǎng)交換機(jī)怎么用

詳解工業(yè)以太網(wǎng)交換機(jī)的原理、特點(diǎn)、優(yōu)勢(shì)、應(yīng)用

車載以太網(wǎng)交換機(jī)硬件設(shè)計(jì)指南

車載以太網(wǎng)交換機(jī)硬件設(shè)計(jì)指南

評(píng)論