本文記錄SDC約束文件中比較復雜的一些命令,包括時鐘分頻、時序例外、多周期約束、半周期約束、多時鐘約束等。感覺項目中能用到的基礎命令差不多就總結完了。

時鐘分頻

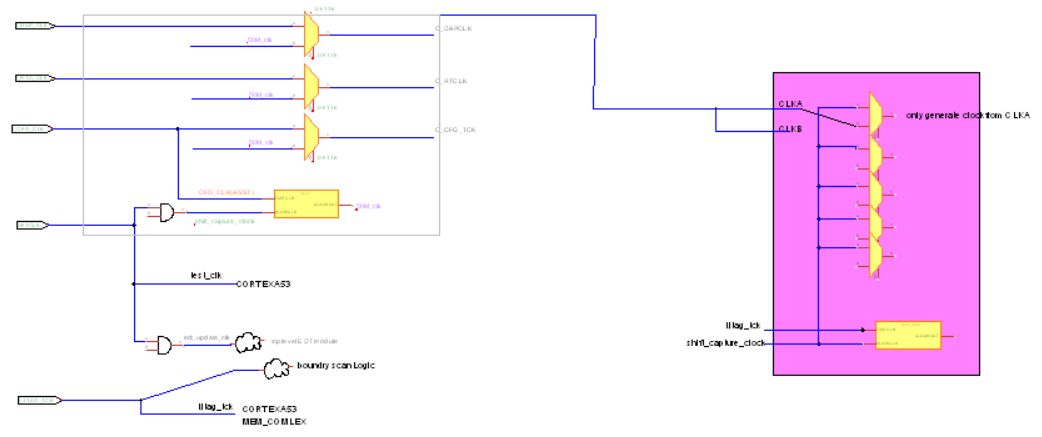

時鐘信號穿過時序單元分頻之后,需要人為設置generatedclock,工具才能夠正確推導分頻之后的時鐘。因為EDA工具在STA時,時鐘信號不能穿透時序單元傳播。

命令:

create_generated_clock-divide_by 2 -nameCLKG-source[get_portsCLK] [get_pinsFF1/Q]

set_clock_latencyvalue[get_clocksCLKG]#設置延時

set_clock_uncertaintyvalue[get_clocksCLKG]#設置不確定性

set_clock_transitionvalue[get_clocksCLKG]#設置轉換時間

除-divide_by之外,還可以采用-edges更精確的表明相對于masterclock,generatedclock的時鐘跳變邊沿。

FalsePath

某些情況下,設計中的確存在某些路徑,但是這些路徑之間的時序是不可能的,或者不是真實的,就要設置falsepath,讓工具不再對該路徑進行STA(注意只是不進行時序分析,路徑還是存在的)。比如跨時鐘域之間的路徑,不會跳變的路徑等,或者不可能的路徑等。命令為:

set_false_path

互斥時鐘

多個時鐘是同步的,但是邏輯是相互排斥的,比如通過MUX二選一的時鐘,他們之間的時序路徑也不需要分析,為了讓工具不再優化兩時鐘之間的時序,可以用兩種命令約束:

方法1:

set_false_path-from[get_clocks CLK1] -to [get_clocks CLK2]

方法2:

set_clock_group-logically_exclusive-groupCLK1 -groupCLK2

-logical_exclusive表示兩個時鐘在邏輯上是不能同時存在的。如果物理上不能同時存在,比如同一個時鐘源定義了兩個時鐘,就要采用-physically_exclusive。

異步時鐘

兩個設計的時鐘來自于兩個不同的晶振,時鐘源沒有任何關系,頻率不確定,相位不確定,這兩個時鐘就叫異步時鐘,工具無法對異步時鐘進行時序分析,也沒必要進行時序分析。但是設計人員要確保信號在異步時鐘域之間的傳輸時不出現亞穩態。一般采用打兩拍、握手、fifo等跨時鐘域處理方式。

命令為:

set_clock-asynchronous-groupCLKA-groupCLKB

set_case_analysis

用于約束固定0/1,或者只有上升沿/下降沿的端口,在這個端口散出的路徑中,就只有0/1,或者只分析上升沿/下降沿。在MMMC設置中,經常用這個設置芯片的不同工作模式。

多周期設計

在設計中,當兩個寄存器之間的組合邏輯路徑里,數據傳輸花費的時間多于一個時鐘周期,就需要為這個組合邏輯路徑聲明為多時鐘周期路徑。

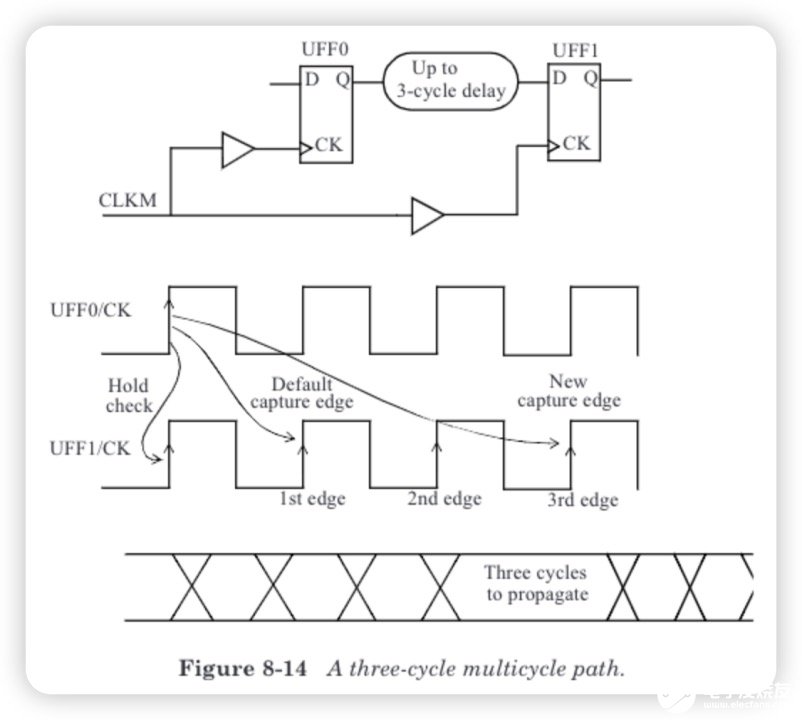

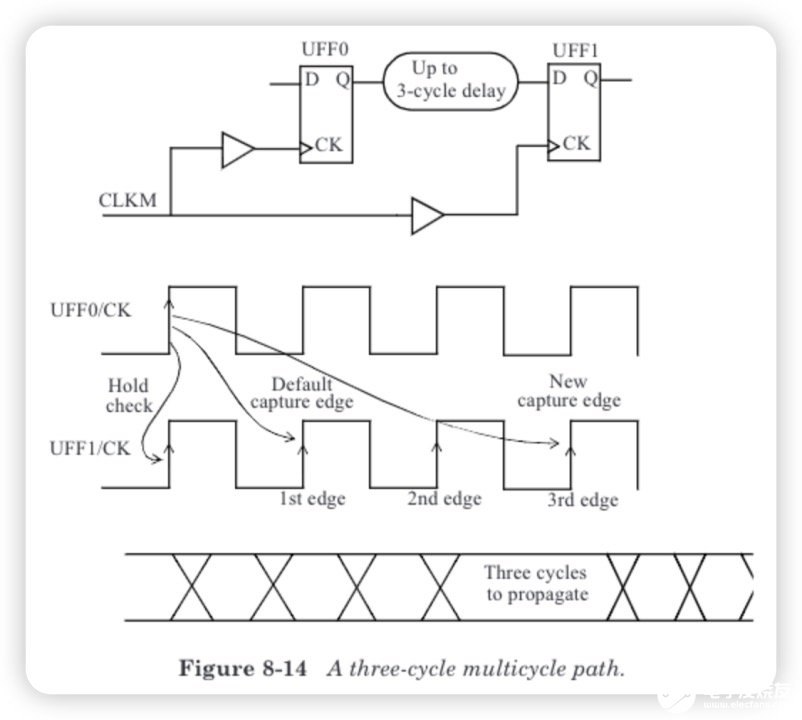

上圖中,兩個寄存器之間的組合路徑需要3個時鐘周期。對建立時間的約束命令為:

create_clock-nameCLKM -period 10 [get_portsCLKM]

set_multicycle_path 3 -setup -from[get_pins UFF0/Q] -to [get_pinsUFF1/D]

接下來考慮hold時間檢查,默認的hold檢查是setup之前的有效沿(2ndedge),但是實際上數據不需要經過這么久的延時,實際上hold檢查的合理有效沿需要提前2個周期(setup-1),因此hold約束命令為:

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

此外,如果該多時鐘周期路徑分為兩個部分A和B,其中A的延時為3clockcycles,B的延時是一個標準的時鐘周期,那么可以只用-through選項約束慢速的部分。命令:

set_multicycle_path 3 -setup-througSLOW

set_multicycle_path2-hold-throughSLOW

Half-Cycle Paths

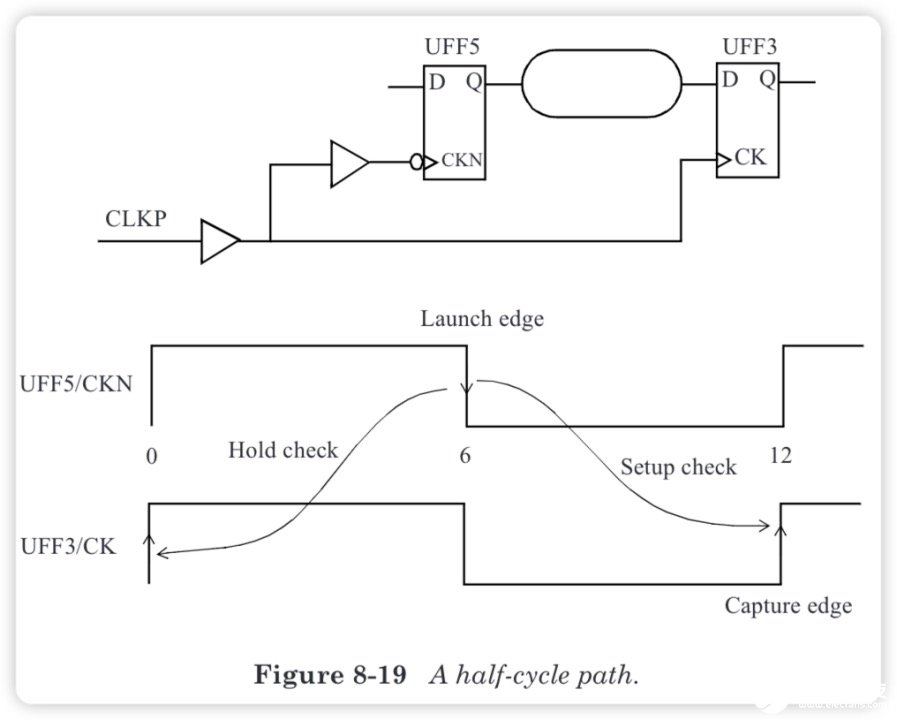

當設計中同時存在上升沿和下降沿出發的場景,就很可能存在half-cyclepath。比如上升沿出發的寄存器到下降沿觸發的寄存器或者下降沿出發的寄存器到上升沿觸發的寄存器,如下所示。

建立時間中,數據的ArriveTime等于下降沿的6ns延時加上數據的延時,RequireTime為12ns的時鐘周期。即數據只有半個時鐘周期的時間,因此對建立時間的約束更苛刻了。

保持時間的含義是在時鐘沿跳變時,上一個狀態不能變化太快。如上圖所示,保持時間的檢查的有效沿為caputreedge的上一個上升沿,由于launchedge已經有半個周期6ns的延時了,因此數據總是在6ns之后才來的,因此保持時間的裕量特別大。

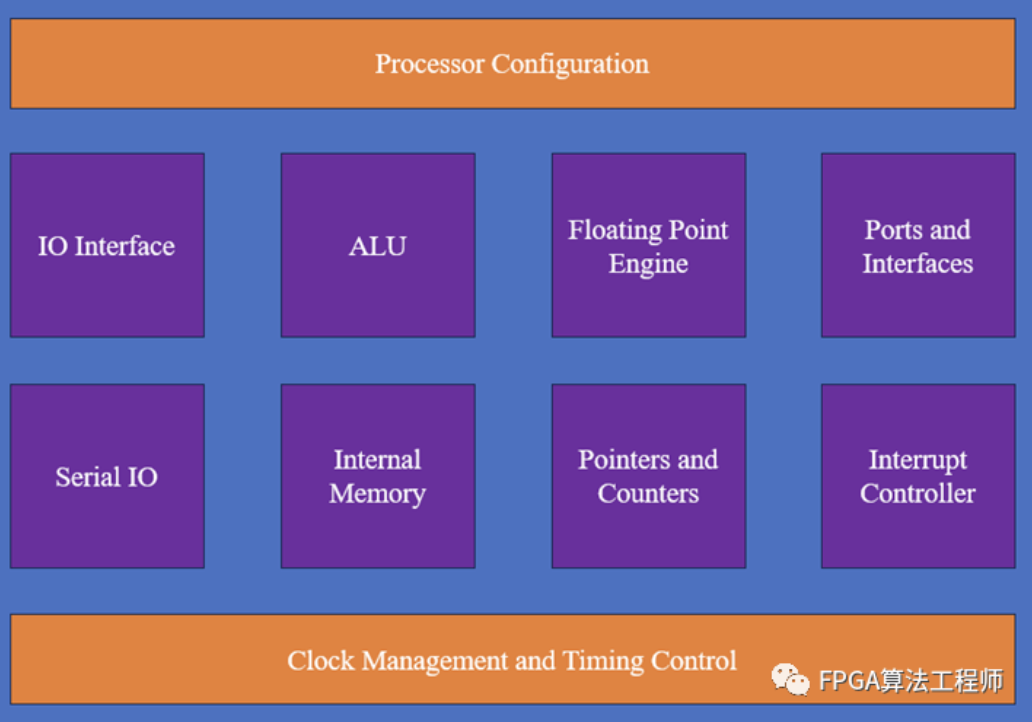

多時鐘約束

設計內部包含多個時鐘,但是所有時鐘都通過一個時鐘源分頻得到,這種是同步時鐘,相位都是固定的。工具在分析時序時,會自動計算兩時鐘信號相鄰最近的相位的時間差,作為STA檢查中的RequireTime。

在輸入/出端口,一個輸入/出對應著多個時鐘的輸入,這種需要對該端口進行多約束。

多時鐘輸入延時

create_clockCLKA#內部時鐘

create_clockCLKB#外部時鐘

set_input_delay1 -clockCLKB-max【get_portsA】

其中CLKA為待優化模塊內部的采集端口A數據的時鐘,CLKB為待優化模塊外部驅動數據進入端口A的虛擬時鐘。

多時鐘輸出延時

create_clockCLKA#內部時鐘

create_clockCLKB#外部采集時鐘B

create_clockCLKC#外部采集時鐘C

set_output_delay1 -clockCLKB-max【get_portsA】

set_output_delay1 -clockCLKC-add_delay-max【get_portsA】

Removal/RecoveryTiming

可以理解為復位信號的“Setup/HoldTime”。

審核編輯:黃飛

-

時鐘源

+關注

關注

0文章

93瀏覽量

15936 -

時鐘信號

+關注

關注

4文章

445瀏覽量

28511 -

異步時鐘

+關注

關注

0文章

17瀏覽量

9402 -

時鐘分頻

+關注

關注

0文章

4瀏覽量

5713

發布評論請先 登錄

相關推薦

聊聊ASIC設計約束與SDC命令

Linux中常用的壓縮和解壓縮命令介紹

時序約束 專版

Linux系統中常見的壓縮命令工具概述

如何將Altera的SDC約束轉換為Xilinx XDC約束

時序分析基本概念—SDC概述

ASIC設計約束與SDC命令

SDC約束文件中常見的基礎命令總結

SDC約束文件中常見的基礎命令總結

評論