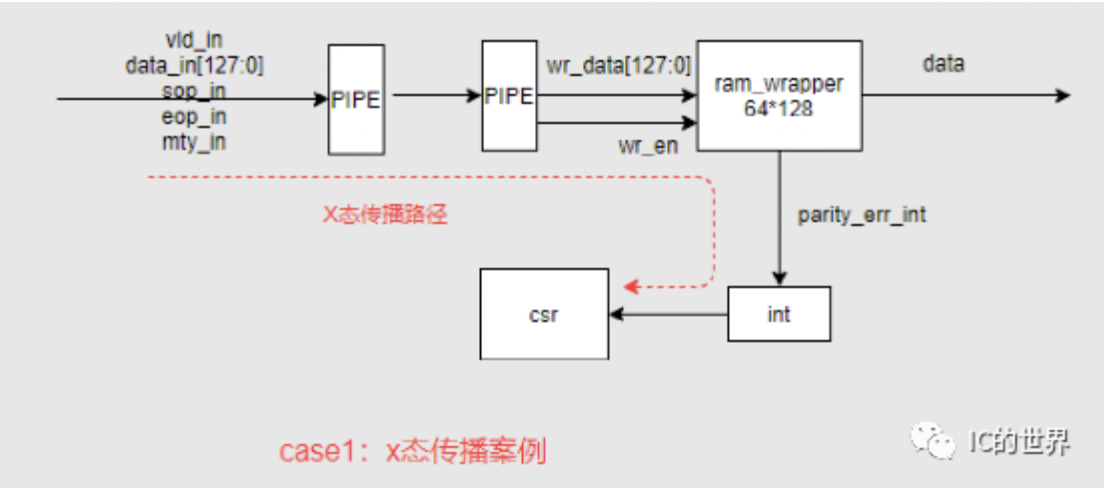

在使用VCS進行仿真時,工程師們常常會面對一個極為重要且充滿挑戰的問題——X態傳播行為。X態信號代表了未知或不確定的邏輯值(或者高阻Z態),可能會在設計中引入意想不到的問題,因此如何處理X態成為了芯片設計與仿真中的一個關鍵議題。

VCS提供了仿真選項-xprop=vmerge/tmerge/xmerge來處理和擴散X態傳播問題。本文將深入探討仿真中的X態傳播行為,著重于不同仿真選項對X態傳播的影響,以及應對X態隱匿和擴散的一些方法。

對于-xprop,官方給出的解釋是:

Verilog和VHDL常用于數字設計建模。設計人員使用RTL構造描述硬件行為。然而,某些RTL仿真語義不足以準確地為硬件行為建模。因此,相比實際硬件行為,仿真結果要么太過樂觀,要么太過悲觀。

因為這些語義限制,Verilog和VHDL仿真器會忽略掉控制信號上的X不定態,在輸出上會分配一個固定的數值。這樣造成的結果就是,由于缺少X的傳播,RTL仿真器往往無法檢測到和X態相關的設計問題。然而,同樣的設計問題可以在門級仿真中檢測出來,因此許多時候必須運行大量的門級仿真,只是為了調試X相關問題。現在VCS在RTL階段提供了的全新X傳播(X-propagation)支持,使用該技術,工程師可以節省大量用于調試RTL和門級仿真的X建模的差異上的時間和精力。

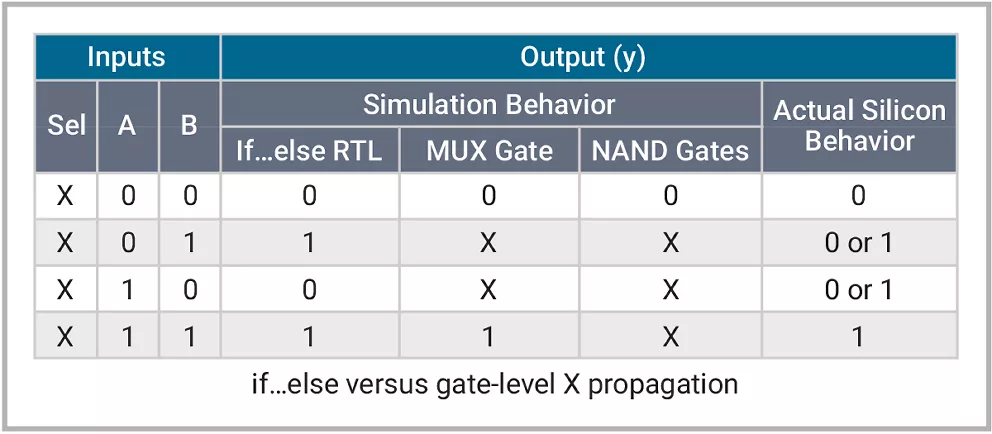

進一步查詢可以明確,不加入-xprop選項時默認的仿真行為是vmerge。從X態傳播的嚴重程度來看,xmerge>tmerge>vmerge,三個選項可以等價理解為悲觀預期>合理預期>樂觀預期。那么到底是需要X態傳播嚴重些呢還是樂觀些呢?單純從驗證的角度,通常我們是希望X態盡可能的傳播以便發現更多的隱藏問題;但是如果過于悲觀的行為預期又會和實際電路行為有所出入。因此根據個人的經驗,數據和運算通路的模塊應該能夠通過xmege測試,而控制通路的模塊至少通過tmerge測試。

好了言歸正傳,我們來探究下不同-xprop選項對仿真結果的影響,主要對三種常用語句繼續探究:assign/case/if-else,那么先上個省流版:

好了接下來咱們來展開聊聊,就從assign說起吧。

assign

assign是對xprop選項最不敏感的語法,無論是在哪種xprop配置反應都是一樣的(如有遺漏請不吝賜教)。對于邏輯運算,assign遵循合理X態規則: 如果能確定數值,則傳播確定值,否則傳播X態 。具體的規則如下:

x & 1 = x

x | 1 = 1

x & 0 = 0

x | 0 = x

x ^ 0 = x

x ^ 1 = x

參考如下代碼和波形:

//test0

logic t0_sel0, sel1;

initial begin

t0_sel0 = 1'b0;

`DELAY(20, clk);

t0_sel0 = 1'bx;

end

wire t0_xend0 = t0_sel0 & 1'b1;

wire t0_xend1 = t0_sel0 | 1'b1;

wire t0_xend2 = t0_sel0 & 1'b0;

wire t0_xend3 = t0_sel0 | 1'b0;

wire t0_xend4 = t0_sel0 ^ 1'b1;

wire t0_xend5 = t0_sel0 ^ 1'b0;

-xprop=vmerge/tmerge/xmerge波形均一致:

但是呢,有一個assign語法不太合理(僅僅從RTL角度而不是仿真角度),會呈現X態:

wire t0_xend6 = (t0_sel0 == t0_sel0)

而對于===則會反饋為1,這個也算是很”著名“的==和===的區別,感興趣的可以自行查閱:

assign對于選擇邏輯,配置為vmerge和tmerge遵循的規則仍然是 如果能確定數值,則傳播確定值,否則傳播X態 ,比如下面這個代碼:

wire t2_en2 = t0_sel0 ? t2_data0 : t2_data1;

vmerge和tmerge的波形如下:

而xmerge的波形如下:

不過需要注意的是在xmerge配置下,如果X態出現在數據內那就不無腦X而是合理X了:

wire t2_en3 = t2_data0 ? t0_sel0 : t2_data1;

好的關于assign的X態傳播行為就說這么多吧。

case

對于case語句當判斷語句中出現X態時,會是什么行為呢?來看下面這段代碼:

always @* begin

case(t0_sel0)

0 : t2_en1 = t2_data0;

1 : t2_en1 = t2_data1;

default: t2_en1 = t2_data0;

endcase

end

vmerge仿真結果:

tmerge仿真結果:

xmerge仿真結果:

區別很明顯了,那我們總結一下規律,case(sel)選擇a or b:

通過表來看,個人認為tmerge是最為合理的策略。而對于X態在數據中的情況,無論什么配置case都是如實的將X態傳播出來,比如這個代碼:

always @* begin

if(t2_data0)begin

t2_en4 = t0_sel0;

end

else begin

t2_en4 = t2_data1;

end

end

哪怕xmerge的仿真結果也是這樣的:

所以大家也看出來了,X態傳播中我們真正需要擔心的是條件中的X態,數據里的X態一般都能如實的反饋出來。

if-else

直接上代碼:

always @* begin

if(t0_sel0)begin

t2_en0 = t2_data0;

end

else begin

t2_en0 = t2_data1;

end

end

vmerge仿真結果:

tmerge仿真結果:

xmerge仿真結果:

雖然vmerge下都沒有傳播X態,但是顯然行為和case時候又不一樣了。那么總結一下if(sel) a else b的選擇語句結果:

可以發現sel有X態時if-else語句中vmerge選擇的是else分支,而case是選擇"不變"策略;tmerge和xmerge的結果則是和case語句相同的。

當然了對于X態在數據內,無論什么配置if-else語句也是如實的將X態反饋出來:

always @* begin

if(t2_data0)begin

t2_en5 = t0_sel0;

end

else begin

t2_en5 = t2_data1;

end

end

好的,做了這么多實驗,最后還是匯總剛剛的那張表,對于條件有X態的場景,三種語法的規則如下:

對于數據有X態的場景,三種語法均會如實合理的傳播X態。本篇內容至此,下次來討論下如何快速高效的反饋和定位X態傳播問題。

-

仿真器

+關注

關注

14文章

1016瀏覽量

83649 -

VHDL語言

+關注

關注

1文章

113瀏覽量

17988 -

RTL

+關注

關注

1文章

385瀏覽量

59710 -

VCS

+關注

關注

0文章

78瀏覽量

9590

發布評論請先 登錄

相關推薦

LM2903B仿真中,為什么運放Vcc電壓為0的時候,同相輸入端的電壓的電壓是負值?

時序仿真中怎么查看內部信號的變化

RTL級仿真與門級仿真

關于modelsim后仿真鎖存器出現不定態的問題

X態如何通過RTL級和門級仿真模型中的邏輯進行傳播呢?

IC設計:接口X態隔離設計

RTL仿真中X態行為的傳播—從xprop說起

RTL仿真中X態行為的傳播—從xprop說起

評論