過去幾十年來,在摩爾定律的推動下,處理器的性能有了顯著提高。然而,傳統的計算架構將數據的處理和存儲分離開來,隨著以數據為中心的計算(如機器學習)的發展,在這兩個物理分離的單元之間傳輸數據的成本越來越高,在整體延遲和能耗方面占據了主導地位。

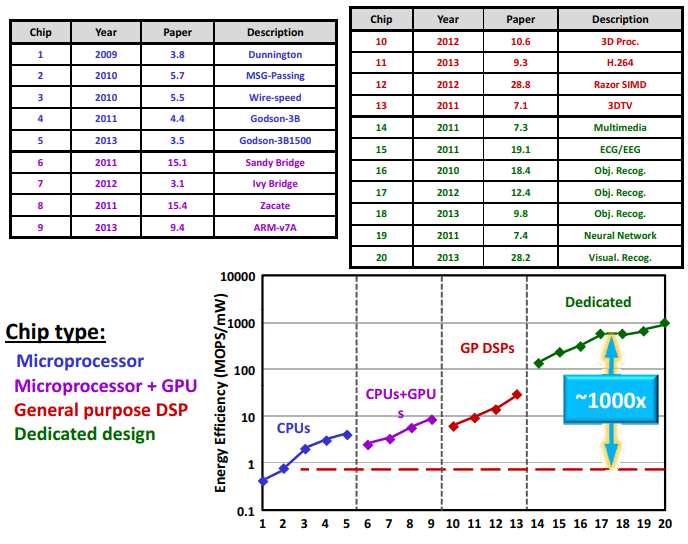

專用處理器的能效

同時,盡管傳統邏輯門具有通用性和魯棒性,但其計算效率低下,在進行乘法、加法和非線性函數等算術計算時需要消耗大量資源。此外,通過在底層硬件層面構建多個內核來提高計算并行性也需要耗費大量資源。

傳統的計算硬件基于馮-諾依曼架構,處理和內存分離,數據需要在兩者之間來回穿梭。這在處理機器學習任務時效率很低,既限制了計算速度,又浪費了電力。神經形態計算有各種不同的形式,是一種可能的解決方案,例如,IBM研究院的研究人員最新設計的芯片中受大腦啟發,它將內存和處理元件共置一地,無需訪問片外內存。這種被稱為NorthPole的芯片能以比現有架構更快的速度和更低的能耗執行圖像識別任務。

另一種也可歸入神經形態計算的方法是存內計算。在這里,計算任務被轉移到存儲它們的內存單元中。迄今為止,已開發出了一系列復雜的存內計算技術,用于克服馮-諾依曼瓶頸,并持續提高計算吞吐量和能效。

01.在后摩爾時代提高計算機性能

存內計算(CIM)技術是解決摩爾定律瓶頸的潛在方案之一。

CIM與“存算一體化”(in-memory computing)和內存處理密切相關,其子領域有時被稱為存內邏輯。CIM的基本思想是,將數據計算移至存儲數據的內存單元,從而實現原位計算,消除帶寬限制和數據移動成本。

它通常利用物理定律(如基爾霍夫電流定律)和內存陣列中的電荷共享來進行模擬計算,創建高效的計算基元,包括邏輯門和乘積(MAC)操作。此外,交叉點隨機存取存儲器(RAM)架構允許自然扇出,從而促進了大規模計算并行性。

這些優勢催生了各種CIM研究方向,目的是在后摩爾時代提高計算機性能,并為人工智能(AI)等應用構建計算加速器。

CIM研究涉及從基礎電子器件到高級架構和大規模系統的各個層面,可以使用新興的電阻式存儲器,也可以使用成熟的硅基存儲器。盡管名稱相同,但CIM技術的基本原理卻大相徑庭,這取決于全部或部分輸入操作數是否由存儲單元就地提供、計算完成后是否將輸出重新就地存儲在存儲單元中、輸入/輸出數據是易失性還是非易失性,以及輸入/輸出數據是否以相同的物理方式表示......這些差異使得我們很難對CIM技術形成全面的認識。

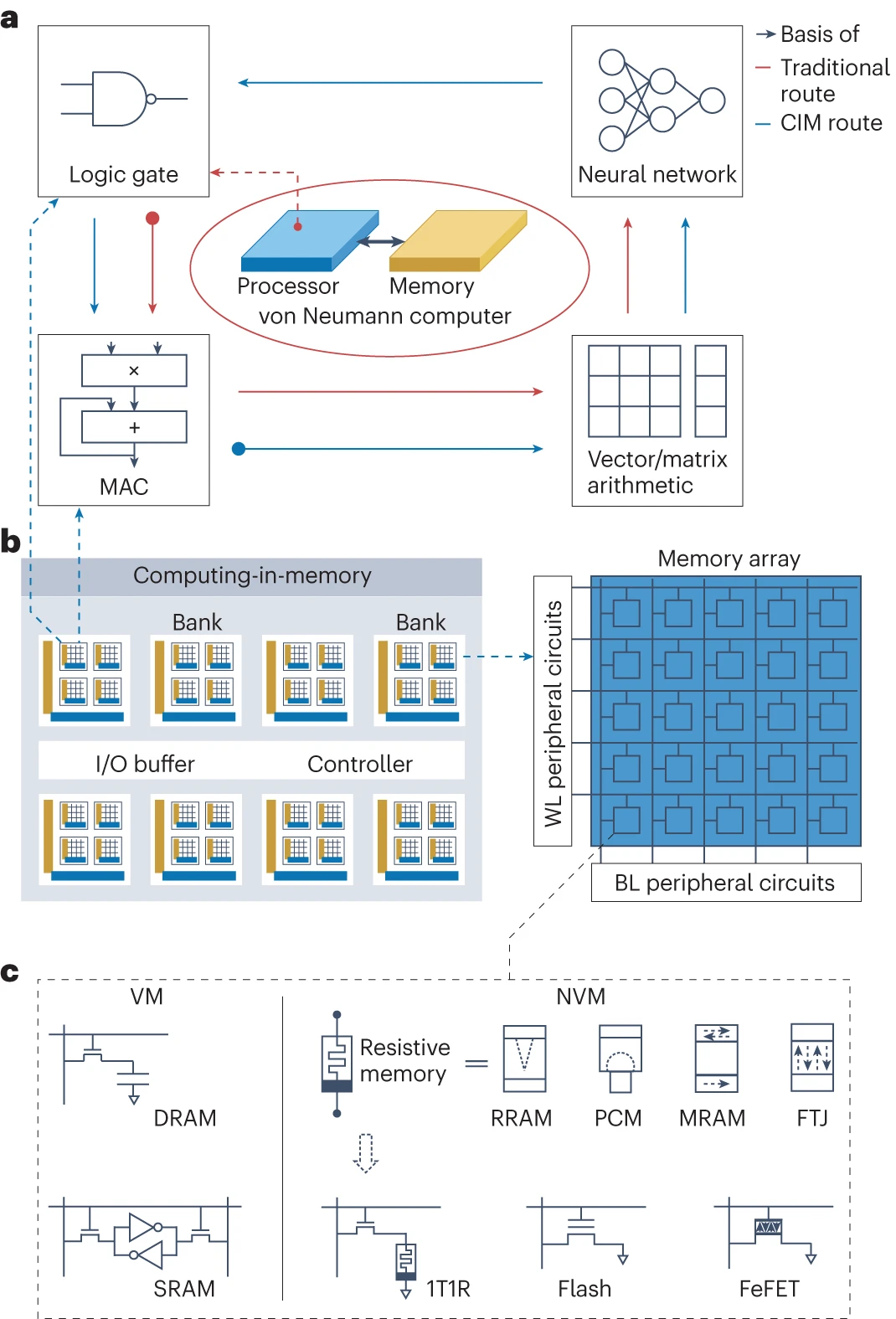

計算基元和CIM的基礎部件。a)馮-諾依曼體系結構和CIM體系結構中計算原語的ouroboros模型。在馮-諾依曼計算機中,計算路線從基本邏輯門開始,提供算術運算,以支持人工神經網絡等算法。所有這些計算都在處理器中執行,處理器與整個內存層次結構通信,以運行完整的程序。在當今的CIM提議中,計算一般基于存內單元中的物理MAC運算,利用物理定律進行乘法和求和。物理MAC可以很容易地在內存陣列中并行化,以進行向量和矩陣運算,這反過來又為ANN奠定了基礎。b)CIM架構,包括內存陣列瓦片組、輸入/輸出(I/O)緩沖器和控制器。c)包括VM和NVM在內的存儲器技術,所有這些技術都可以在交叉點架構中實現CIM

MAC是計算機運算的基本操作,它與基礎布爾邏輯門的關系如圖所示。在馮-諾依曼計算機中,所有操作都依賴于功能完整的邏輯門,而邏輯門又是由互補金屬氧化物半導體(CMOS)晶體管構成的。邏輯門用于構建算術計算的處理核心,其中最重要的是MAC運算。由于矩陣代數的常規形式,標量MAC運算可通過順序處理或多核并行化擴展到矢量/矩陣運算。

最后,矩陣代數為大量算法奠定了基石,其中,ANN(和深度學習)是當今最受關注的算法。就CIM而言,其理念始于嵌入式電路物理的MAC運算,它通過基于ANN的閾值邏輯概念為邏輯門奠定了基礎,而邏輯門又是通過向量運算實現的。并行MAC或邏輯門都可以沿著存儲器陣列中的一列進行,盡管前者是后者的基礎。在這種方法中,并行MAC和復合邏輯門都用于執行矩陣計算,例如神經網絡。

與CMOS邏輯門相比,CIM邏輯門的優勢在于能將計算融合到存儲器陣列中,以及交叉點RAM架構提供的大規模計算并行性。由于CIM邏輯門依賴于物理定律的模擬計算,任何線性可分離的邏輯功能都可以在一次操作中完成。因此,復雜的邏輯功能可以通過減少運算次數和降低硬件成本來輕松實現。

02.六類存內計算技術

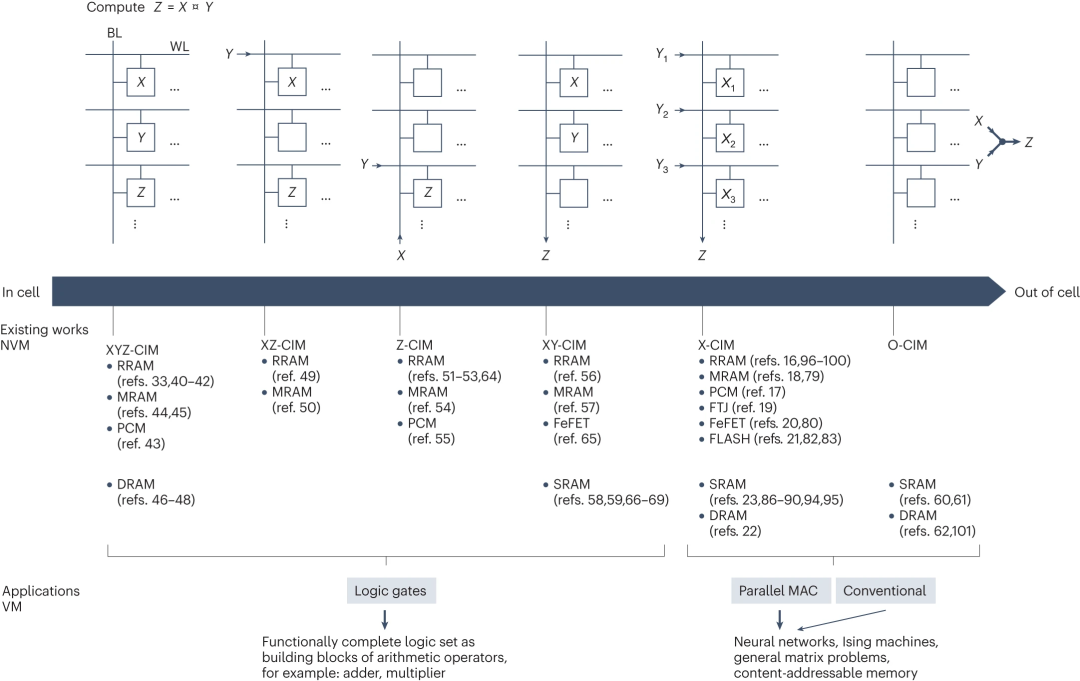

全方位的CIM技術可抽象為一個等式Z = X¤Y,其中符號¤代表邏輯門或點乘運算。對于點乘,X和Y分別代表權重向量和輸入向量,Z是標量輸出;對于邏輯門,X和Y是兩個輸入操作數,Z是邏輯輸出。

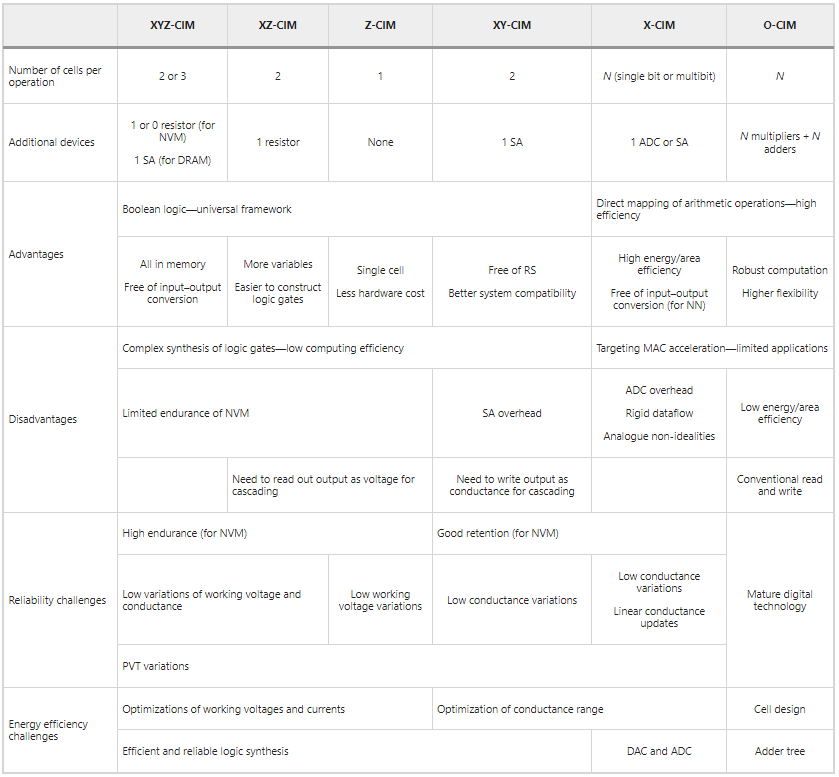

根據X和Y是否由存儲單元提供,以及計算結束時輸出Z是否重新存儲在存儲單元中,CIM被分為六類:XYZ-CIM、XZ-CIM、Z-CIM、XY-CIM、X-CIM和O-CIM。

全方位的CIM技術。每種類型的CIM都標明了候選存儲器、計算基元和主要應用。頻譜是在將并行MAC(點積)和邏輯門抽象為Z = X¤Y的基礎上建立的,其中X和Y可以是標量或向量,Z是標量,¤是表示CIM操作的符號。所有CIM技術分為六種類型,從全部在內存中到不在內存中,每種類型都有若干NVM和/或VM種類,進而針對通用或特定應用

XYZ-CIM

X和Y均由陣列中的存儲單元提供,輸出Z也重新存儲在一個存儲單元中。計算依賴于X和Y的隱式讀出,從而修改BL電位,最終改寫輸出單元。XYZ-CIM是典型的布爾邏輯運算,已通過單位非易失性RRAM、PCM、MRAM和易失性DRAM實現。

XZ-CIM

在計算過程中,只有一個輸入操作數駐留在內存單元中。另一個輸入由外部施加的電壓編碼,輸出Z在計算結束時重新存儲為單位單元狀態。XZ-CIM僅適用于基于NVM的邏輯運算,典型的存儲器技術包括RRAM和MRAM。

Z-CIM

存儲單元中只存儲輸出Z,輸入通過BL和WL提供。考慮到BL和WL電壓的所有可能組合,由此產生的單比特單元狀態構成一個邏輯門。Z-CIM已在RRAM、MRAM和PCM等NVM上實現。

XY-CIM

輸入操作數X和Y均由存儲單元提供,而輸出Z則通過BL檢測放大器 (SA) 獲得。它也適用于邏輯運算,存儲器技術可以是電阻式NVM或SRAM。它的工作原理是并行讀出兩個單比特存儲單元,并將讀出結果感應和離散化為二進制輸出。

X-CIM

只有輸入X由陣列中沿一列的存儲單元提供,Y由施加到WL的外部電壓表示,輸出Z則在BL外圍獲得。與上述類型的CIM不同,X-CIM通常旨在以高度并行的方式執行兩個向量的點乘。所有存內技術,包括單比特或多比特NVM和單比特VM都已實現了X-CIM,這為進一步鼓勵其研究提供了積極反饋。

O-CIM

這里沒有存儲單元之間的交互,而是將傳統邏輯門或計算模塊置于存儲單元或陣列附近進行計算。O-CIM通常采用成熟的存儲器技術進行設計,包括SRAM和DRAM。它類似于早期的近存儲器計算概念,但其進步在于進一步縮短了存儲器與處理器之間的距離。

由于全面識別了輸入的來源和輸出的方向,基于該分類法的頻譜應涵蓋所有CIM技術。在頻譜的末端,它與傳統的馮-諾依曼范式相聯系。在這一范圍內,特定的存儲技術可能被用于多種類型的CIM,但原理各不相同。另一方面,某些類型的CIM在技術上可能只適用于特定的內存設備,或只值得關注。此外,計算基元與CIM類型相關,并最終與存儲器載體相關。

除O-CIM外,所有其他CIM類型都依賴于模擬乘法、加法和電路中物理定律的非線性激活。將前兩種運算結合起來,就可以得到用于并行MAC運算的點乘,而將所有三種運算結合起來,就可以得到布爾邏輯門。

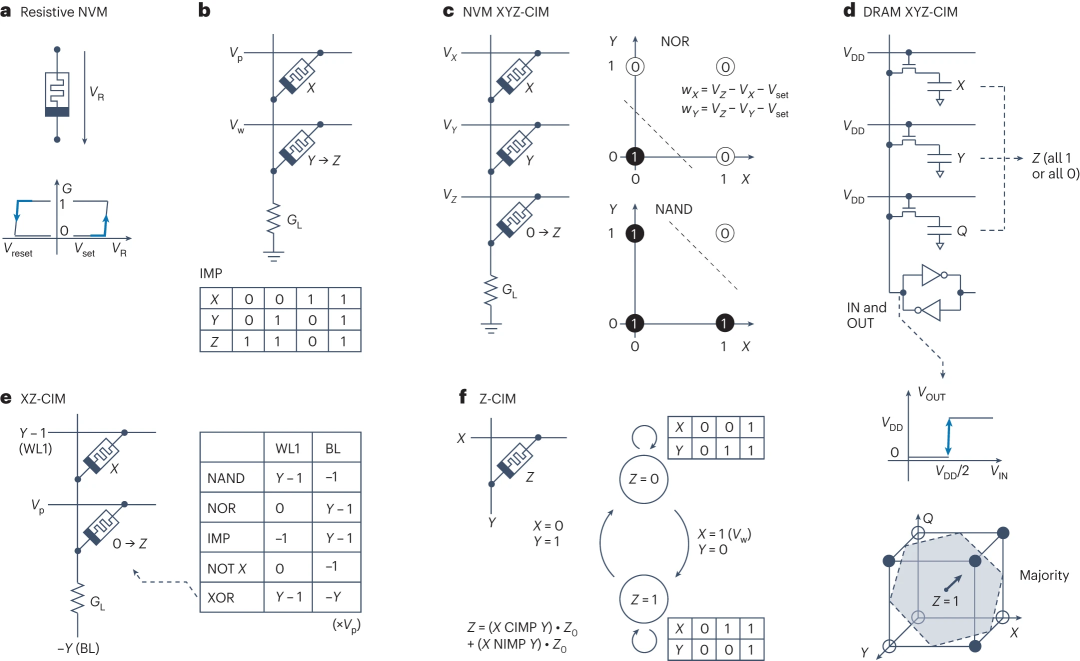

03.各種CIM技術的原理

XYZ-CIM、XZ-CIM和Z-CIM的共同點是將輸出Z原位存儲在存儲單元中。它們都主要使用新興的NVM進行邏輯運算。由于新興NVM通常是基于電阻的存儲器,因此可將其視為一般的兩端電阻開關 (RS) 器件。通常情況下,當器件兩端的電壓足夠大且具有正負極性時,就會通過“設置”切換到高導狀態(HCS),或通過“復位”切換到低導狀態(LCS)。

這種描述適用于RRAM、MRAM和FTJ。由于CIM通常只使用一種開關極性,因此單極性開關PCM也可包含在此模型中。兩種電導狀態編碼二進制1和0,與傳統存儲器應用相同。對于邏輯門,計算依賴于器件的條件開關,這是其他器件狀態和外加電壓的函數。這種非線性特性可視為 ANN中的激活函數。

因此,任何基于RS的NVM器件都有可能用于這三種類型的CIM。

XYZ-CIM、XZ-CIM和Z-CIM。a)電阻式存儲器件示意圖及其RS行為;b)XYZ-CIM的狀態IMP邏輯;c)XYZ-CIM的SFNN;d)DRAM位向邏輯;e)XZ-CIM 的邏輯運算;f)Z-CIM 的邏輯運算

XYZ-CIM:NVM有狀態邏輯

在XYZ-CIM建議中,一種突出的方法是基于所謂的有狀態邏輯,利用NVM器件(通常是RRAM)實現。蘊含(IMP)門最初是為有狀態邏輯運算而提出的,一個RRAM單元的電導狀態編碼輸入操作數X,而另一個單元則代表操作前和操作后的輸入Y和輸出Z。電阻的電導值大致設定在LCS和HCS的對數值中間。

Vp(例如,Vw/2)和Vw分別施加到兩個WL中的一個不同的WL上,其中Vw足夠大以實現設定的轉換,而Vp則不然,同時BL電阻器接地。激活后,單元Y的最終狀態,即輸出Z,根據IMP函數確定。具體來說,如果Y單元最初處于HCS (1),則施加的電壓極性不會觸發開關;如果Y最初處于LCS (0),則其開關取決于X:如果X處于LCS,由于兩個LCS設備的隔離,BL電位將接近于0。

因此,器件Y上的壓降足以將其切換到HCS;但如果X位于HCS中,Vp將大大提高BL電位,從而阻止Y的切換。

XYZ-CIM:DRAM位向邏輯

DRAM位向邏輯是另一項重要的XYZ-CIM提議,它依賴于計算期間的鎖存型SA同步重寫。商用DRAM產品只需少量修改甚至無需修改即可實現該功能。

圖(d)顯示了由三個DRAM單元組成的一列,在BL的末端有一個鎖存型SA。SA是一個雙穩態電路,由兩個CMOS反相器組成,形成一個正反饋回路。與BL相連的終端既是輸入節點,也是輸出節點,通過它來檢測和修改BL電壓。當BL電壓高于(或低于)VDD/2時,SA迅速做出反應,將輸出穩定在VDD(或0)。在邏輯運算中,多行同時被激活。因此,電路自然會執行三個輸入單元的多數邏輯功能,邏輯結果最終會重新存儲在所有三個單元中。

第一步,將BL預充電至VDD/2,以實現位向邏輯。然后,用VDD同時激活三個WL,而SA尚未激活。存儲在DRAM單元X、Y和Q中的電荷由所有DRAM電容(電容CC)和寄生BL電容(電容CB)共享,從而使BL電位達到VDD/2。

多數邏輯函數是線性可分離的,DRAM電路可視為單層感知器,類似于SFNN。在該模型中,輸入是存儲的電壓電平,網絡權重由電容給出,非線性激活神經元由閾值為VDD/2的鎖存型SA激活。在多數門的基礎上,可以方便地實現更復雜的功能,例如全加法器。為了實現一套完整的邏輯門,可以利用SA中的互補位設計NOT門,通過另一個選擇晶體管將互補位寫入雙觸點單元。與保留所有輸入的SFNN不同,DRAM位邏輯對邏輯輸入具有破壞性。為解決這一問題,可在陣列中專門設計三行用于邏輯運算。

此外,在邏輯運算之前和之后,應執行RowClone操作,即利用相同的電荷共享原理將源行中的數據復制到目的行,以便在陣列內傳輸輸入和輸出。

XZ-CIM

XZ-CIM還依賴于RRAM和MRAM等NVM器件的條件切換。有狀態邏輯以兩個輸入存儲單元的電導狀態為條件,而XZ-CIM中用于調節的兩個輸入則分別用電導狀態和電壓表示。

這種編碼方法為邏輯門的構建提供了更多便利,并使XOR等線性不可分割函數的一步操作成為可能,但卻增加了級聯時轉換輸入和輸出異質屬性的成本。基于兩個RRAM單元的典型XZ-CIM邏輯門如圖(e)所示。一個輸入操作數X由RRAM器件的電導狀態提供,而另一個輸入操作數Y則由外加電壓編碼。

輸出重新存儲在第二個單元中,該單元初始化為LCS(0)。BL負載電阻的電導值設置在LCS和HCS之間,以便進行適當的分壓。輸出存儲單元采用恒定的Vp,條件是Vset/2 < Vp < Vset,然后WL1和BL的電壓決定邏輯門的類型。在XOR的情況下,WL1和BL的電壓分別為 (Y - 1)Vp 和 (-Y)Vp 。

通過改變所加電壓的編碼方案,該電路可以實現所有16個雙輸入布爾邏輯門,從而簡化復雜函數的邏輯合成,進而縮短CIM的延遲時間。

Z-CIM

基于NVM的邏輯可擴展到Z-CIM,其中輸入操作數X和Y均通過施加電壓來提供。輸出Z作為存儲單元的電導狀態就地存儲(圖f)。除了MRAM和PCM之外,RRAM一直是Z-CIM研究最活躍的對象。

它基本上基于NVM的傳統寫入操作,但對傳統上被認為無效的其他輸入組合進行了邏輯擴展。RRAM的切換取決于壓降的極性和初始電導狀態。當存儲單元最初處于LCS狀態(Z0 = 0)時,只有X = 1 (Vw)和Y = 0的輸入組合才能將設備切換到HCS,即Z = 1,而在其他輸入情況下,設備仍處于LCS狀態(Z = 0)。當存儲單元最初處于HCS狀態(Z0 = 1)時,只有X = 0和Y = 1 (Vw) 的組合才會關閉設備并存儲 Z = 0,而在其他情況下,設備仍處于Z = 1狀態。這兩種情況分別對應于非蘊涵函數(NIMP)和互補蘊涵函數(CIMP)。

通過將一個輸入固定為1或0,或通過交換應用于WL和BL的操作數以及級聯此類操作,所有14個線性可分離邏輯門都可以用存儲單元來實現。

線性不可分離的XOR/XNOR是例外。為使其可行,應采用基于堆疊兩個極性相反的電阻開關的互補RRAM概念,利用其非對稱讀出過程。另外,1T1R單元可以更有效地執行Z-CIM的XOR邏輯,這要歸功于該結構的終端數量較多,便于對輸入操作數進行編碼。

XY-CIM

基于NVM或SRAM的邏輯運算也提出了XY-CIM。

就NVM而言,兩個輸入操作數是存儲單元的二進制電導狀態(LCS或HCS)。基本上,任何具有兩種不同電阻狀態的NVM器件都可用于XY-CIM,包括本征三端器件,如 FeFET。在同時激活兩個WL時,存儲單元的狀態被讀出到BL,其中的電流(ILCS或IHCS)被累加,并由電流模式SA感測。可以將SA視為二元神經元電路,以參考電流作為激活閾值,產生邏輯輸出。

兩個輸入的四種組合會產生以2ILCS、ILCS + IHCS和2IHCS為中心的三種BL電流分布。因此,在2ILCS和ILCS + IHCS之間(或ILCS + IHCS和2IHCS之間)設置SA的閾值,就能得到線性可分離的OR(或AND)邏輯函數。

鑒于神經元激活是通過CMOS電路實現的,因此很容易得到兩個邏輯門的倒數,即NOR和NAND。OR和NAND的組合將產生線性不可分割的XOR邏輯,通過連續施加兩個參考電流來實現。

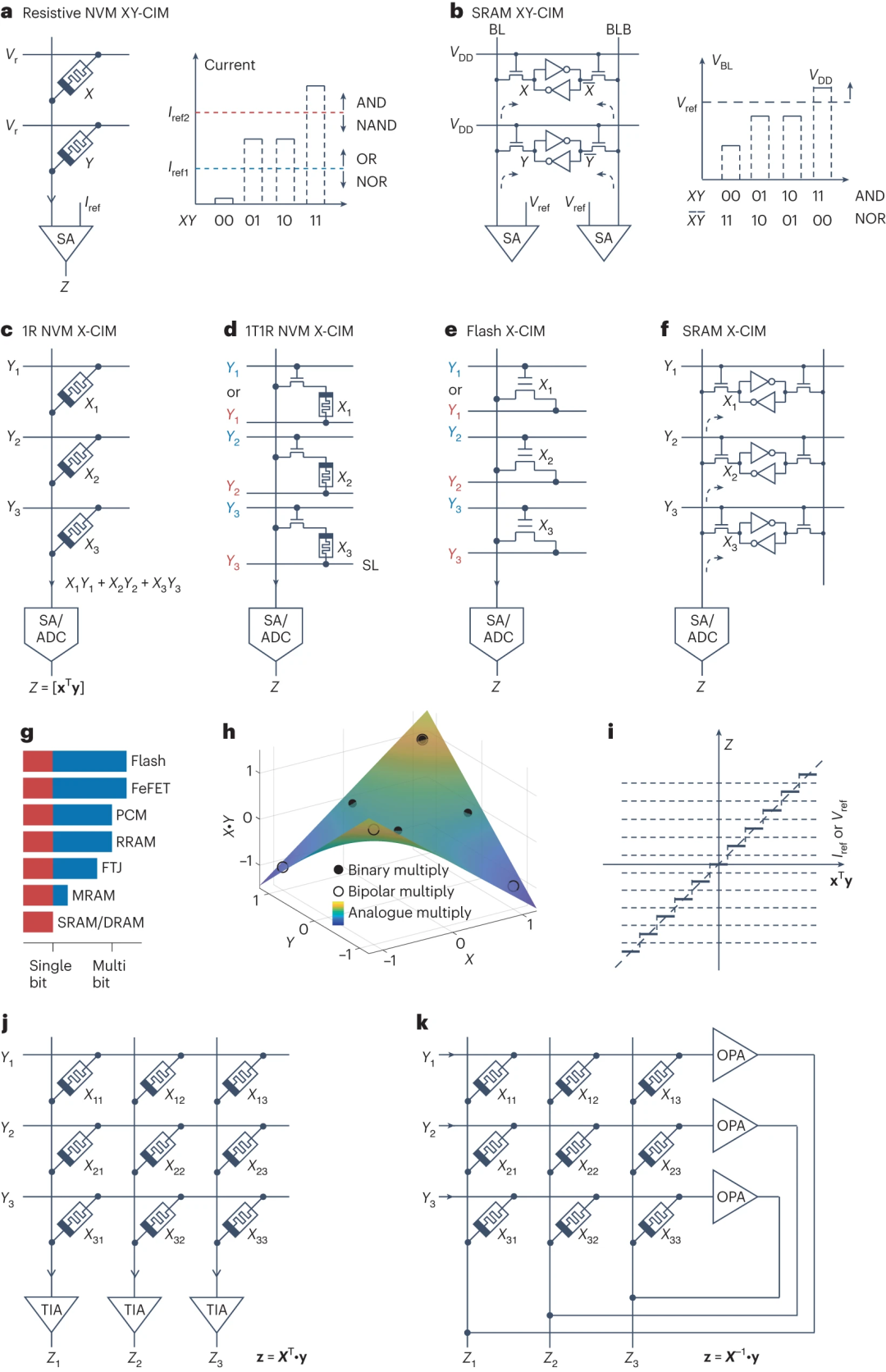

XY-CIM和X-CIM。a)XY-CIM基于電阻式NVM的邏輯運算。b)基于SRAM的XY-CIM邏輯運算。c-f)基于被動1R NVM(c)、基于1T1R NVM(d)、基于NOR閃存(也基于FeFET)(e)和基于SRAM(f)的點積運算

就SRAM而言,XY-CIM的兩個輸入操作數由存儲在SRAM單元中的電壓電平提供。

SRAM單元的核心是雙穩態電路,其兩個內部節點存儲二進制電壓電平及其補碼。在標準6T SRAM結構中,兩個選擇晶體管控制BL和互補BLB,以訪問兩個節點。在進行邏輯運算時,BL和BLB首先被預充電到VDD,如同SRAM的讀出過程。

同時激活兩個WL時,BL和BLB 可能會放電,這取決于兩個SRAM單元的狀態。具體來說,只有當輸入X和Y均為1時,BL才會保持在VDD位置。如果有一個單元處于0狀態,則BL放電至較低電壓;在兩個單元都處于0狀態的情況下,BL電壓的降低會加劇。

通過為SA設置參考電壓,以區分VDD和其他降低的BL電壓,SA輸出被識別為AND邏輯結果。當BLB訪問輸入位X和Y的補碼時,SA采用相同的參考電壓提供NOR邏輯。

同樣,AND和NOR的組合也有助于XOR邏輯。傳統6T SRAM的位邏輯運算會受到存儲單元的干擾,這是由于通過同一端口的寫入和讀取路徑耦合所致。當多個WL同時開啟時,BL/BLB可能會放電,進而導致存儲單元狀態翻轉。為解決這一問題,主要策略是通過增加存取晶體管或修改其配置來解耦寫入和讀取路徑,從而形成4 + 2T/8T/10T SRAM結構。此外,WL的欠驅動或異步激活也有助于解決干擾問題。

X-CIM

X-CIM的基本物理原理與XY-CIM基本相同,只是輸入操作數的定義不同。

通常,X-CIM以實現并行MAC運算為目標,其中一個輸入操作數由表示權重向量x的存儲單元列提供,另一個輸入則是外部施加到WL或其他線路上的電壓向量y。因此,這兩個向量的點積在BL上以電流或放電累積的形式產生,然后由BL外圍電路感應。人們對ANN加速器的濃厚興趣促使所有存儲器技術都被用于X-CIM,該技術正在積極研究中,并努力實現模擬-數字混合浮點精度方案。

X-CIM也可能意味著基于非易失性存儲器(如MRAM和FeFET)的邏輯運算。然而,人工智能加速器在并行MAC運算方面的大量工作使這方面的努力黯然失色。

在虛擬機方面,SRAM憑借其獨特的優勢和工業成熟度,包括快速讀/寫速度、低功耗、無限耐久性以及與最先進邏輯工藝的兼容性,在利用X-CIM進行并行MAC加速方面備受關注,盡管其代價是單元占用空間較大。值得注意的是,在鎖存器電路中,還包括x的補碼二進制向量,這對帶符號計算非常有用。

SRAM結構具有豐富的靈活性,可用于可靠、高效的X-CIM優化,但4T鎖存器電路始終是權重存儲的核心。一種策略是通過采用8T/10T/12T結構來解耦讀出路徑,以保護SRAM單元免受干擾,但這會進一步加劇單元占用空間的問題。在一些基于標準6T SRAM陣列的方案中,加入了專門設計的局部計算單元和全局BL,以平衡電路功能和面積開銷之間的權衡。

根據存儲器技術的不同,存儲在存儲器單元中的權重向量x可以是單位或多位的。雖然VM通常是單比特器件,但許多NVM顯示多比特甚至模擬狀態,這是提高X-CIM吞吐量的關鍵因素,而機器學習加速非常需要這種吞吐量。閃存、FeFET、PCM、RRAM和FTJ是出色的模擬電導器件,這要歸功于它們的基本物理特性,允許對電荷存儲、鐵電極性比、晶體體積和導電絲直徑等狀態變量進行持續調整。

因此,這些非易失性存儲器件的存儲窗口很大,從10到10^6不等,這使它們能夠在單個單元中存儲多比特信息。由于電導開關比小,MRAM被認為是單比特存儲器,盡管目前正在努力開發多比特器件。為了最大限度地提高計算效率,輸入矢量y通常編碼為多比特值,如具有模擬幅度或寬度的WL電壓脈沖,不過也可能采用串行二進制脈沖以節省數據轉換成本。

因此,CIM操作是在電流域、時域或電荷域進行的。鑒于x和y都可能是二進制值、模擬值或由差分運算實現的雙極值,兩個元素的乘法運算可能采用AND邏輯、雙極XNOR或純模擬結果的形式。由于多位輸入和同時激活的多個WL(通常為?2),點乘的檢測需要一個能量化多個離散輸出電平的轉換電路,這通常通過多級SA或模數轉換器 (ADC) 來實現。與存儲單元相比,SA和ADC通常要大得多,耗電量也更大。因此,除了原位計算和X-CIM固有的并行性,SA或ADC已成為另一個效率瓶頸,需要進行設計優化,以保持CIM帶來的性能提升。

O-CIM

最近,基于SRAM的CIM通過在存儲單元附近加入傳統邏輯門,逐步轉向全數字領域。由于在計算過程中不需要融合存儲單元,因此被合理地稱為O-CIM。

在這種方法中,一個輸入操作數通過一條專門設計的線路從外部提供,另一個輸入操作數從SRAM單元讀出并輸入到鄰近的邏輯門,由邏輯門執行兩個操作數的乘法運算。為了對乘法結果進行求和,必須在附近部署分層加法器樹,在數字域中產生部分和。

就DRAM而言,傳統的計算模塊不是將單個邏輯門嵌入存儲單元周圍,而是靠近陣列構建,從而利用陣列級并行性實現MAC加速。O-CIM通常采用成熟的易失性存儲器進行設計,以尋求與當代商業產品的工業兼容性。通過采用標準數字計算單元,O-CIM比其他基于模擬計算的CIM更為可靠。

04.CIM技術發展的挑戰與展望

不同CIM方案的主要特點和挑戰,以及這些方法在器件可靠性和計算效率方面面臨的挑戰

CIM技術可用于融合內存和計算,并為加速計算提供空間并行性。它們還可以通過使用非常規但功能強大的邏輯門(例如多數函數),以及將算術運算直接映射到硬件電路,來提供高效計算。

CIM可通過同時激活多個WL來實現,從而通過陣列中的物理規律啟動存儲單元之間的交互。目前已開發出一系列CIM技術,其中許多技術都基于交叉點陣列架構——該架構可容納幾乎所有存儲器技術。

新興的NVM已成為CIM的重要候選技術,并被用于探索一系列超越內存的應用。相反,DRAM和SRAM等成熟內存技術的修改較少:DRAM已針對存儲密度和減少漏電進行了優化,因此不利于工藝修改,盡管CIM在陣列中造成的開銷不到1%;SRAM的優勢在于其在現代邏輯制造工藝中的靈活性,允許定制存儲器陣列設計,盡管標準的6T SRAM仍受到重視。

在CIM中,邏輯門的開發旨在為通用計算提供功能完整的邏輯集,所有XYZ/XZ/Z/XY-CIM類型都能通過眾所周知的邏輯集(如AND + OR + NOT 門或單一NAND或NOR門)或非常規邏輯集(如IMP + FALSE門)提供這種功能。相比之下,并行MAC是為加速神經網絡等特定應用而開發的。

在不同的邏輯門CIM方案中,有兩個因素可用來區分不同的方法:計算(即非線性激活)是否由被動RS單元執行,以及輸入和輸出操作數的物理屬性是否相同。在前一種情況下,使用RS單元作為神經元的NVM有狀態邏輯、XZ-CIM和Z-CIM實現非常緊湊,但DRAM比特邏輯和XY-CIM方案需要額外的有源SA進行計算,因此犧牲了部分面積效率。在后一種情況下,XYZ-CIM被認為是一種真正的CIM方法,因為所有輸入/輸出操作數都由陣列中的存儲單元就地表示;它沒有轉換過程,因此可以輕松實現級聯,并有利于順序處理的整體延遲。

相反,NVM的XZ-CIM、Z-CIM和XY-CIM則需要額外的操作來將輸出讀出為電壓(或將輸出寫入為電導),以便級聯下一個邏輯門,從而造成延遲,阻礙吞吐量的提高。就SRAM而言,可能需要設計一個特殊單元,將邏輯輸出寫入單元,以便后續訪問。

X-CIM和O-CIM均用于并行MAC,但使用方式不同:即模擬與數字。X-CIM可以提供很高的能量/面積效率,這要歸功于將計算基元直接映射到存儲器陣列的高效方法。然而,由于計算過程的模擬性質,它的精度會因設備(如電阻單元、電容器或晶體管)、陣列和電路的非理想性而下降。在一次操作中,還可以提高輸入的分辨率、NVM的存儲容量和CIM單元的并行性,從而提高計算吞吐量。然而,這種優勢也帶來了輸入數模轉換和輸出模數轉換的開銷。

在NVM的X-CIM應用中,神經網絡已被提出,由于每兩層神經元之間的權重矩陣是固定的,因此MVM可以自然級聯。對于通用應用,由于存儲單元中一個向量的隔離,可能需要像邏輯門一樣的屬性轉換過程來進行級聯操作。

O-CIM在數字域中使用傳統的CMOS邏輯門。因此,它的計算穩健性更高。此外,由于省去了ADC和數模轉換器 (DAC),數據轉換的負擔也得以克服。模擬X-CIM的硬件映射是固定的,與之相比,數字O-CIM具有更高的靈活性,可以適應更廣泛的問題。不過,由于每個處理元件都包括一個乘法器和一個用于MAC運算的加法器,因此它在面積和能效之間進行了權衡,類似于其他數字加速器,如基于收縮陣列的設計。

在用于邏輯運算的CIM類型中,NVM狀態邏輯、XZ-CIM和Z-CIM依賴于存儲器單元的動態RS,因此要求器件具有較高的耐用性,以支持頻繁的邏輯門操作。因此,PCM(據報道其耐用性超過10^10)似乎更適合(盡管還不夠)這些類型的CIM。RRAM的最新耐用性相當有限(超過10^6),必須加以改進才能達到要求。MRAM的表現甚至更好,一般顯示出10^12的耐用性。然而,MRAM本身受限于較小的內存窗口,這對可靠的模擬計算,尤其是多輸入邏輯門構成了障礙。

由于XY-CIM和X-CIM基本上是兩個或多個單元的并行讀出過程,因此可以采用任何具有兩個或多個不同狀態的存儲器件。因此,NVM器件的時間保持特性和狀態變化應足以保證可靠的讀出、求和和離散化,分別由用于邏輯運算或并行MAC的SA或ADC完成。雖然NVM器件在傳統的二進制存儲器應用中一般都能保持足夠的存儲時間(85°C時超過10年),但在邏輯運算中,兩個或多個單元狀態的線性疊加會對存儲性能造成更嚴格的限制。特別是在用于并行MAC的X-CIM中,最好有一個多比特單元,通常會同時激活多個單元以提高吞吐量。

在這種情況下,除MRAM外,所有NVM設備都顯示出較大的存儲窗口,從而實現了多位存儲。然而,由于受到狀態變化的嚴重限制,最先進的NVM只能提供可靠的兩比特容量。因此,要實現更大容量的存儲單元,仍有很大的器件優化空間,成熟的多級NAND閃存可以作為很好的參考。

非易失性存儲器的模擬電導經常被用于計算,通常是為了在人工智能加速器等典型應用中實現較高的等效吞吐量和能效。然而,必須注意的是,傳統的存儲器模式應始終保持,在這種模式下,應能以足夠的讀出余量區分多種狀態。為了開發可靠的基于電阻式NVM的CIM技術,在算法和系統層面已經做出了許多努力,但這些努力通常僅限于特定應用。

位切片、分而治之和補償等策略已被用于擴展大規模問題的計算精度。雖然這些解決方案可方便地應用于正向矩陣乘法,但對于X-CIM的矩陣反演而言,這些問題變得難以解決,從而為基于電阻式NVM的通用矩陣計算留下了探索空間。

NVM設備的耐用性不足是有狀態邏輯、XZ-CIM和Z-CIM所面臨的關鍵問題,阻礙了它們在實際應用中的發展。對于有狀態邏輯和XZ-CIM而言,由于兩者都依賴于模擬乘法、求和及非線性激活,因此必須保證設置/復位電壓以及LCS和HCS在周期與周期之間以及設備與設備之間的低變化,以限制邏輯運算的誤碼率。

Z-CIM不需要模擬乘法和求和。因此,它只需要較低的設定/復位電壓變化。相比之下,XY-CIM和X-CIM則需要較低的LCS和HCS變化,以實現可靠的CIM操作。特別是在使用多位NVM器件的并行MAC中,輸入存儲單元的電導分布和點乘結果會變得更加復雜,因此需要設計精細的讀出電路(SA/ADC)。此外,X-CIM還可能涉及神經網絡訓練。因此,電導更新在電導范圍的最小或最大邊界具有良好的線性非常重要。

要克服NVM器件的耐久性、時空一致性和更新線性等挑戰,從根本上說,這些都是由器件物理特性控制的,因此必須對器件材料和結構進行優化,從源頭上解決這些問題。所有這些CIM方案都依賴于模擬計算,而模擬計算很容易受到工藝-電壓-溫度(PVT)變化的干擾。不過,對于使用新興NVM的CIM的PVT問題,目前僅有偶爾的研究,但這是實際應用過程中的一個重要挑戰。

要最大限度地提高CIM的能效,需要解決幾個問題:

1)在基于RS的CIM方案中,每個事件都會導致相當大的功耗。因此,需要優化設置/復位電壓和電流。

在使用靜態存儲單元狀態的XY-CIM和X-CIM中,NVM器件較低的絕對電導率應有助于降低能耗。盡管如此,這種優化并不容易,因為低電導通常伴隨著非線性電流-電壓特性,這會帶來額外的計算誤差。

2)在合成具有完整功能邏輯集的復雜邏輯運算時,可選擇的方法多種多樣。

它可以由許多雙輸入門電路或少數幾個多輸入門電路組成,從而導致硬件和延遲成本的巨大差異,以及對模擬非理想性的不同敏感性。因此,要實現可靠而高效的邏輯合成,就必須權衡利弊。X-CIM一直在努力解決ADC和DAC的開銷問題,而這正是提高能效的主要挑戰。在O-CIM中,雖然使用單邏輯門(例如NOR門)可以方便地實現乘法器,但加法器樹一直是公認的瓶頸。因此,需要在這方面進一步努力,以提高能效和面積效率。

3)此外,雖然X-CIM的并行MAC已被證明在加速計算方面具有相當大的潛力,但它本質上無法提供通用計算系統。在這種情況下,CIM方法中邏輯門與并行MAC運算的結合值得進一步探索。

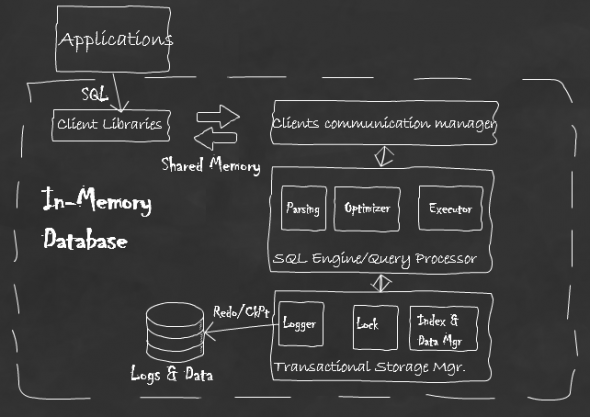

05.存內計算開辟數據處理新范式

目前,存內計算提供了多種技術,但迄今為止最重要的是存內數據庫(以下簡稱IMDB),市場上已有相關軟件及其應用。

早在1984年,市場上就出現了存內數據庫,最早的產品之一是IBM TM1 - OLAP數據庫。然而,由于操作系統和可用硬件的限制,這些系統無法發揮其優勢。近年來,這些限制逐漸被淘汰,市場上出現了幾種來自主要供應商的IMDB解決方案。

2008年,IBM推出了SolidDB作為IMDB,它通過兩個獨立但永久同步的數據庫副本以及硬盤上的永久日志來提供數據的完整性。一旦發生數據丟失,整個數據庫可在幾秒鐘內恢復而不會丟失數據。Oracle于2009年推出了 TimesTen作為IMDB,可用作傳統RDBMS的緩存或獨立數據庫。TimesTen使用事務日志和數據庫檢查點作為數據完整性措施。2010年,SAP推出了HANA數據庫技術,這是一種高性能分析設備。

SQLite是一個包含關系型數據庫系統的程序庫,由于具有許多數據庫接口,是世界上使用最廣泛的SQL數據庫。要在主內存中使用SQLite數據庫,可以在數據庫連接中使用:“存內”選項。一旦關閉數據庫連接,數據庫就會被寫入磁盤。

隨著技術不斷發展,內存數據庫正變得越來越流行,主要用于時間緊迫的應用程序、實時數據輸出以及海量數據分析等領域。例如,谷歌、Twitter和Facebook使用的都是定制的存內數據庫,以確保對不斷增加的數據量做出快速反應。

事實上,關于存內計算的話題,IT專家們認為這是一種范式轉變,是數據處理或實時業務的新時代。

在進行研究和實驗的過程中,可以證明這些說法并不那么籠統。存內計算的高效使用為大數據和實時分析領域提供了全新的可能性,但大型企業在硬件和軟件領域的轉換和購置成本仍然很高。

在不太復雜的領域,如軟件開發中的單元測試,中小型企業已經開始使用存內數據庫。在不久的將來,由于數據量的穩步增長和硬件價格的下降,存內計算技術將變得越來越重要。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19165瀏覽量

229128 -

摩爾定律

+關注

關注

4文章

632瀏覽量

78931 -

計算機

+關注

關注

19文章

7421瀏覽量

87718 -

存內計算

+關注

關注

0文章

29瀏覽量

1373

原文標題:“超越摩爾定律”,存內計算走在爆發的邊緣

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

六類模塊PCB調試技術

【轉】PCB線路板調試技術之六類模塊

PCB設計之六類模塊電路板的調試

六類模塊PCB調試的標準與過程

分享:六類模塊pcb調試技術

超六類網線和六類網線區別如何劃分

網線選擇六類的好還是超六類的好

六類網線和超六類網線不同的地方在哪里

六類網線要用六類的網絡面板嗎-clan

六類存內計算技術原理解析

六類存內計算技術原理解析

評論