Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。

BRAM是FPGA定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的內部,是FPGA實現各種存儲功能的主要部分,是真正的雙讀/寫端口的同步的RAM。

本片文章是基于Vivado的 2017.1的版本,其他版本都大同小異。

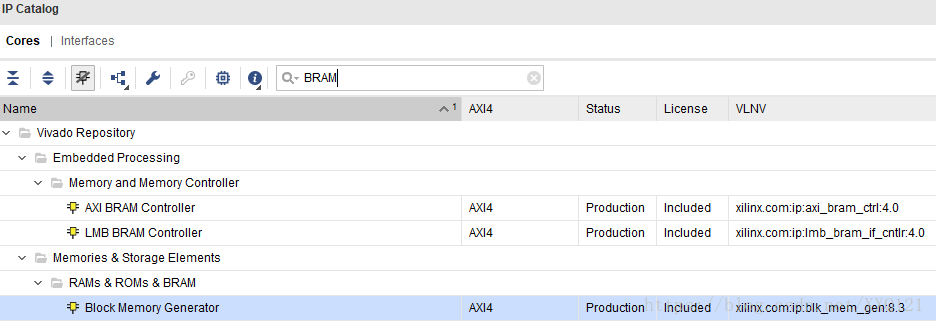

首先在Vivado界面的右側選擇IP Catalog 選項。

然后就可以在IP 目錄中,選擇想要的IP核,此處在搜索框輸入BRAM,選擇我們要使用的BRAM IP核。

即最下方的Block Memory Generator,顧名思義,塊狀RAM。

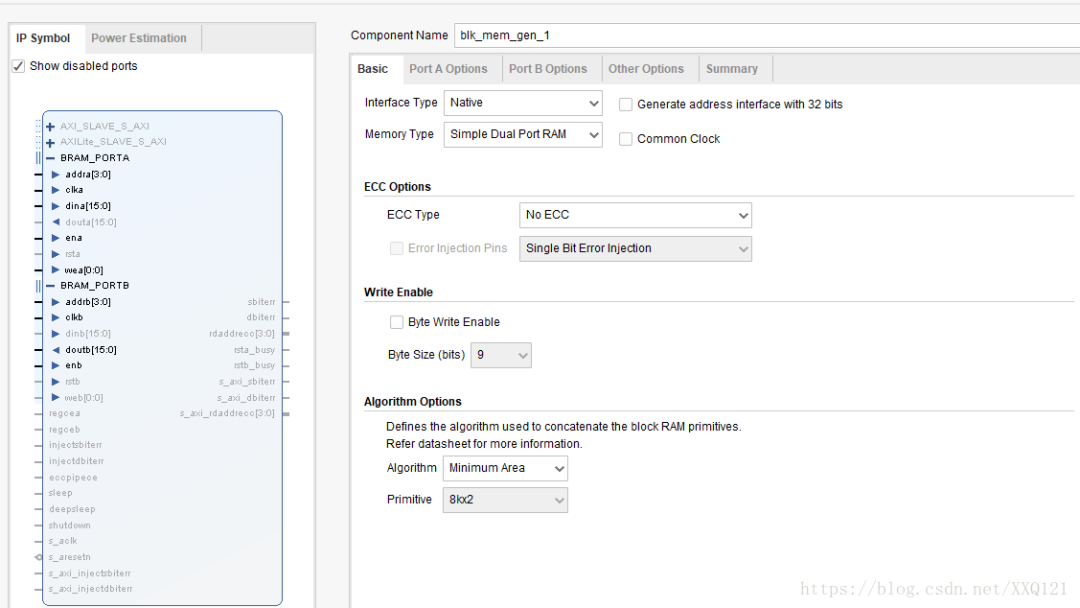

我們常用的是單口BRAM,單口寫,單口讀。可配置Memory Type 為Simple Dual Port RAM。如下圖所示:

其中Component Name 可以自定義自己所需要的模塊名稱。類型定義完成后,可以看到左側顯示的模塊端口,端口的使用后面再細說。

設置完成后,開始設置端口的位寬以及深度,選擇Port A Options選項,可以看到下面的界面。

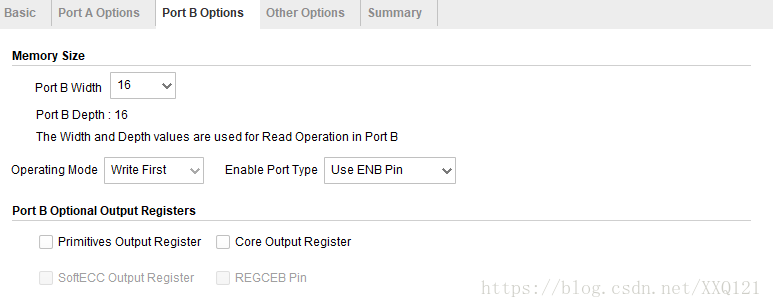

Port A Width即位寬,也就是你存儲數據的有多少位,Port A Depth即深度,也就是你要存多少個數據。端口A設置好后,還需要點擊Port B Options,點擊完進入Port B Options選項后,系統會幫你自動設置好端口B的寬度和深度,因為B肯定是和A一樣的。

可以看到端口B也設置完成,同時在Port B Optional Output Registers有一個Primitives OutputRegisters選項。如果這個選項不勾上,那么正常的情況下,當第一個時鐘時候,送來地址,那么數據會在第二個時鐘取好送出RAM。但是當勾上這個選項后,那么數據就會延遲兩個時鐘,在第三個時鐘送出。這是取數據情況下的時序。當存數據時候,那么只需要地址和數據在同一個時鐘下即可。

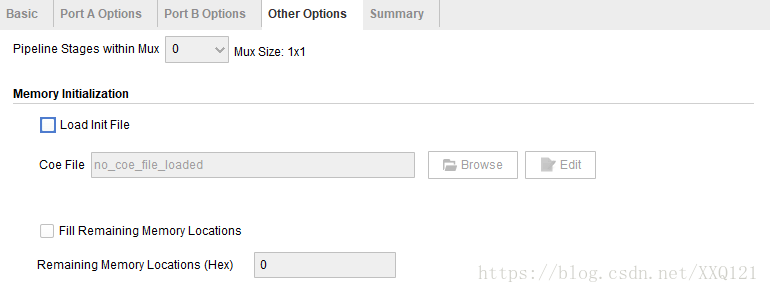

當我們在一般使用RAM時候,如果需要事先存到RAM里的數據量不大,我們可以在Testbench里面寫一下即可。但是如果數據量較大時,那么我們可以使用.coe文件事先將數據導入到RAM 之中,如下圖所示。

在Other Options選項中,有一個Load Init File選項,即加載初始化文件,在這里勾上后,即可加載已存儲好數據的.coe文件。關于.coe文件的制作,網上有很多教程,在此不再贅述。然后點擊下方OK,然后再點擊彈出來的窗口的Generate即可生成BRAM 的IP核。

至此,常用情況下的BRAM的配置選項以及設置介紹完成。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA實現基于Vivado的BRAM IP核的使用

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602004

原文標題:FPGA實現基于Vivado的BRAM IP核的使用

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

vivado導入舊版本的項目,IP核心被鎖。

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

芯驛電子ALINX推出全新IP核產品線

Xilinx DDS IP核的使用和參數配置

關于FPGA IP核

FPGA開發如何降低成本,比如利用免費的IP內核

基于FPGA設計的BRAM內部結構

FPGA設計的IP和算法應用綜述

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應相連?

FPGA優質開源模塊-SRIO IP核的使用

FPGA實現基于Vivado的BRAM IP核的使用

FPGA實現基于Vivado的BRAM IP核的使用

評論