當(dāng)我們談?wù)?a href="http://www.nxhydt.com/tags/mosfet/" target="_blank">MOSFET的寄生電容時(shí),我們?cè)谡務(wù)撌裁矗?/strong>

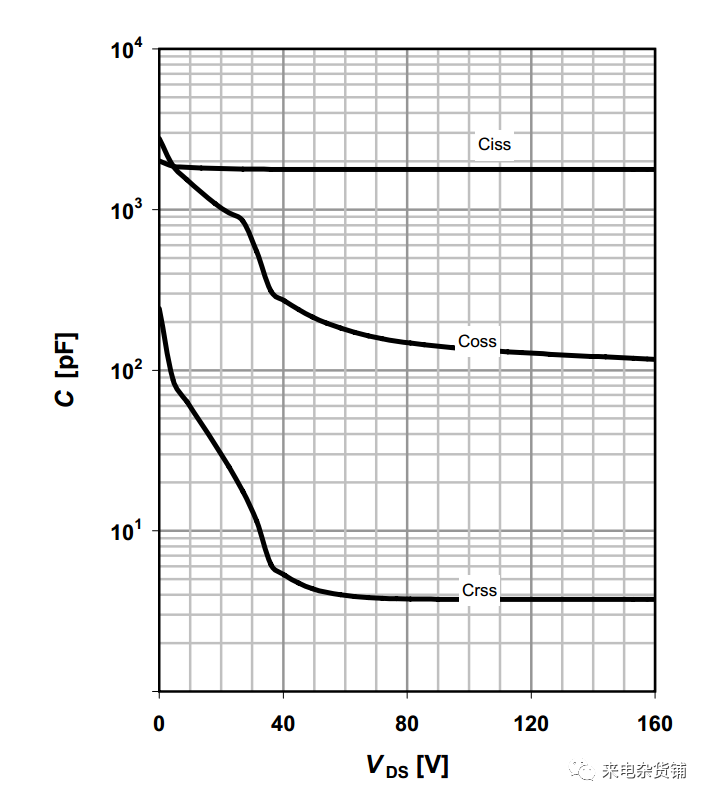

EE工程師都會(huì)面臨MOSFET的選型問題,無論是功率級(jí)別應(yīng)用的Power MOS還是信號(hào)級(jí)別的Signal MOSFET,他們的Datasheet中,一定會(huì)給出MOSFET的三個(gè)結(jié)電容隨Vds電壓變化的曲線。

之所以需要關(guān)心這些電容,是因?yàn)殡娙萑葜祻哪承用娣从沉似骷拈_關(guān)特性,影響了包括開關(guān)速度、效率、振蕩以及EMI在內(nèi)的各種系統(tǒng)特性。

相信很多EE第一次面對(duì)這些寄生電容時(shí),都會(huì)覺得玄乎其玄。為什么電容不再是固定的容值,而非要隨著DS的電壓急劇變化?現(xiàn)實(shí)世界往往是非線性和復(fù)雜的,今天本著格物致知的精神,我們先從功率MOSFET器件的結(jié)構(gòu)出發(fā),讓大家明白MOS里面的這些寄生電容到底是什么,以及怎樣對(duì)應(yīng)到實(shí)際的電路應(yīng)用中來,幫助大家形成一些知識(shí)上的閉環(huán)。

1.橫向溝道與垂直溝道

所謂溝道Channel,本質(zhì)上就是電流在MOS本體中的流通路徑。可以看到,溝道的開通與否是由柵極Gate與源極Souce之間的Vgs電壓決定,因此MOSFET被認(rèn)為是電壓控制型器件。

如下這張示意圖是 橫向溝道設(shè)計(jì) ,漏源極之間距離小且都置于硅晶圓表面,這樣的結(jié)構(gòu)適合集成,多用于信號(hào)級(jí)的MOS。

功率MOS一般采用的 垂直溝道設(shè)計(jì) ,源極和漏極置于晶圓的相反兩端。以常見封裝TO-220為例,芯片置于框架上,通常將靠近塑封料的一面稱為正面,正面主要分布源極和門極,靠近銅框架的一面稱為背面,背面主要分布漏極。這樣從漏極連到源極的溝道的方向就是“垂直的”。

2.垂直溝道MOS的半導(dǎo)體結(jié)構(gòu)

襯底substrate、外延層epitaxial layer和本體P- Body,和高摻雜N+區(qū)構(gòu)成了垂直溝道MOSFET的半導(dǎo)體結(jié)構(gòu)。

如下a)圖,是最早期投入商業(yè)應(yīng)用的VMOS設(shè)計(jì),但由于制造的穩(wěn)定性問題和V形槽尖端的高電場, VMOSFET被取代。

如下b)圖,為DMOSFET設(shè)計(jì)(Fairchild的叫法),可以看到其柵極Gate與表面平行,又稱平面型MOS,這是商業(yè)上最成功的設(shè)計(jì),由于工藝簡單,至今還有非常大的年出貨量。

當(dāng)然,當(dāng)前主流的功率MOS的門極結(jié)構(gòu)如下c)圖,使用U型槽設(shè)計(jì),稱為UMOSFET,或直接稱為溝槽型MOS。

可以看到無論哪種結(jié)構(gòu),MOS的Gate都會(huì)與N+區(qū),P- Body區(qū),以及外延層形成一對(duì)多的局面,這也是MOS的門極相關(guān)電容的主要來源。

3.電容在哪兒?

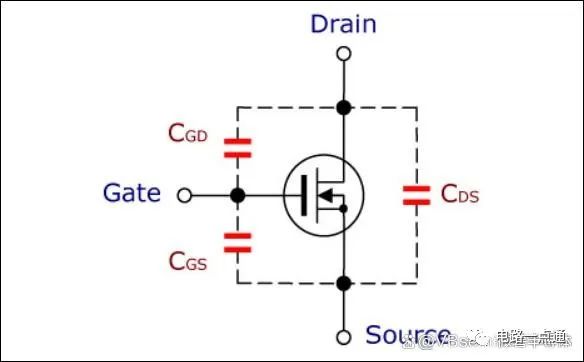

當(dāng)我們從應(yīng)用層考慮寄生電容對(duì)電路性能影響時(shí),對(duì)于MOS管及其結(jié)電容一般采用如下的方式進(jìn)行建模。

同時(shí),廠家也會(huì)在Datasheet中給出Ciss,Coss和Crss的典型值和曲線。如果只是停留在主功率電路的設(shè)計(jì)層面,工程師只需要知道這些電容的大致范圍即可。但在調(diào)試過程中,往往需要關(guān)注到更細(xì)節(jié)的瞬態(tài)波形,對(duì)電容特性的理解就顯得至關(guān)重要了。

上圖為一個(gè)MOSFET元胞的縱向截面,只展示左邊這一半,右邊的一半可以軸對(duì)稱看過去。一個(gè)MOSFET產(chǎn)品往往由成千上萬個(gè)這樣的元胞橫向重復(fù)并聯(lián)組成,因此需要有單位面積電容的概念。

Cgs,是柵極對(duì)源極的電容。在芯片尺度,這個(gè)電容由三部分組成:柵極對(duì)源極金屬的電容Co,柵極對(duì)N+區(qū)的電容CN+,柵極對(duì)P- Body的電容Cp。在芯片表面,源極金屬,N+區(qū)和P- Body,都是等電位的。因此柵極對(duì)源極的電容容值是以上三個(gè)電容容值之和。

其一,柵極對(duì)源極金屬的電容Co可以表示成:

公式中的物理量意義解釋如下

當(dāng)器件柵極結(jié)構(gòu)確定時(shí),Ao 和to都是確定的值,Co可以認(rèn)為是固定值。

其二,柵極對(duì)N+的電容CN+可以表示為:

公式中的物理量意義解釋如下

一些專用仿真軟件,對(duì)MOS進(jìn)行物理層面的建模時(shí),Cox是非常典型的一個(gè)參數(shù),它反映了柵極氧化物的電容性質(zhì)。可以認(rèn)為,Cox也是固定的結(jié)構(gòu)參數(shù),CN+不隨Vds電壓變化。

其三,唯一隨電壓變化的就是柵極對(duì)P- Body的電容 Cp了。在Vds的低壓段,當(dāng)VDS增大時(shí),耗盡區(qū)會(huì)擴(kuò)大至p型體,耗盡區(qū)的厚度決定了電容CP的極間距,容值隨之減小。但到一定程度后耗盡區(qū)的厚度不再增大,不會(huì)超過P- Body的10%,最終表現(xiàn)為Cp在高壓段隨Vds電壓變化極小。

Cgd,是柵極對(duì)漏極的電容,又稱米勒電容。其中,平面型MOS的單位面積的米勒電容可以由以下公式計(jì)算如下:

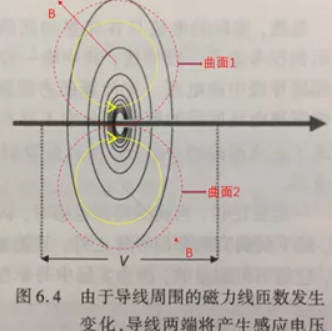

其中,Wd為外延層中耗盡區(qū)的寬度。X為表面外延層的橫向長度。當(dāng)DS電壓越高時(shí),耗盡區(qū)的寬度越大(根據(jù)PN結(jié)理論,表面外延層中耗盡區(qū)的寬度Wd和Vds電壓的平方根成正比),有效的米勒電容的極板面積減小,米勒電容容值減小。

Cds,漏源極電容。這個(gè)電容的容值大小與P-Body和外延層的接觸結(jié)構(gòu)強(qiáng)相關(guān)(上圖是非常理想的平面型接觸,是為了方便大家有一個(gè)定性的理解。實(shí)際上商用MOSFET的接觸結(jié)構(gòu)更多的是三維的,將空間充分利用起來,例如如SuperJuction MOSFET)。這樣的結(jié)構(gòu)可以按如下PN結(jié)的結(jié)電容公式計(jì)算:

可以看到,漏源電容也隨著Vds的增加而減小,和Vds的平方根成反比,這也是大多數(shù)電力電子教科書中近似量化Vds電容非線性的一種方法。

-

MOSFET

+關(guān)注

關(guān)注

144文章

7088瀏覽量

212715 -

MOS管

+關(guān)注

關(guān)注

108文章

2394瀏覽量

66591 -

PN結(jié)

+關(guān)注

關(guān)注

8文章

480瀏覽量

48645 -

寄生電容

+關(guān)注

關(guān)注

1文章

291瀏覽量

19192 -

VDS

+關(guān)注

關(guān)注

0文章

45瀏覽量

10711

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

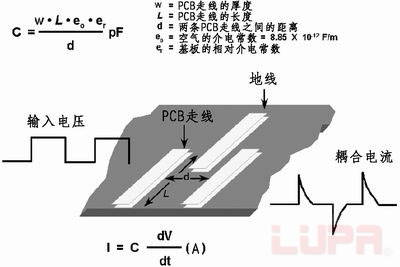

PCB布線設(shè)計(jì)時(shí)寄生電容的計(jì)算方法

PCB寄生電容的影響 PCB寄生電容計(jì)算 PCB寄生電容怎么消除

mos管寄生電容是什么

寄生電容,寄生電容是什么意思

寄生電容產(chǎn)生的原因_寄生電容產(chǎn)生的危害

什么是寄生電容_寄生電容的危害

mos管寄生電容是什么看了就知道

基于寄生電容的MOS等效模型

MOS管的開通過程

MOSFET的寄生電容及其溫度特性

pcb連線寄生電容一般多少

寄生電容對(duì)MOS管快速關(guān)斷的影響

MOS結(jié)電容(下)MOS的結(jié)電容應(yīng)用特性分解

MOS結(jié)電容(上)MOS里的寄生電容到底是什么?

MOS結(jié)電容(上)MOS里的寄生電容到底是什么?

評(píng)論