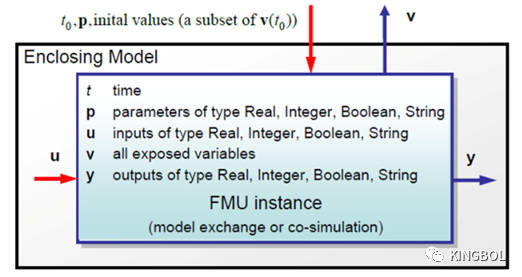

FMI聯合仿真為聯合仿真環境中仿真工具的耦合提供了接口標準。子系統之間的數據交換僅限于離散的通信點。在兩個通信點之間的時間內,子系統由各自的求解器獨立求解。主要算法控制子系統之間的數據交換和所有仿真求解器(子)的同步。

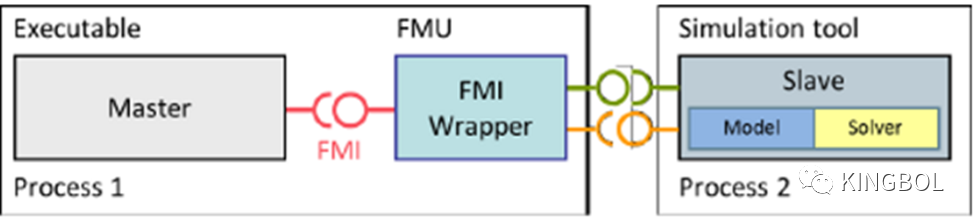

使用工具耦合方法進行聯合仿真:在工具耦合方法中,FMU實現將FMI函數調用包裝到仿真工具提供的API調用中。除了FMU之外,還需要仿真工具來運行一個聯合仿真,如圖1所示。

*Figure 1 *Cosimulation with tool coupling on a single computer

01

FMU的導出

1. 在SaberRD中創建設計

在將Saber設計導出到FMU之前,必須在SaberRD中創建Saber原理圖設計。有關如何創建Saber原理圖設計的信息,請參見SaberRD設計創建用戶指南中的創建設計。

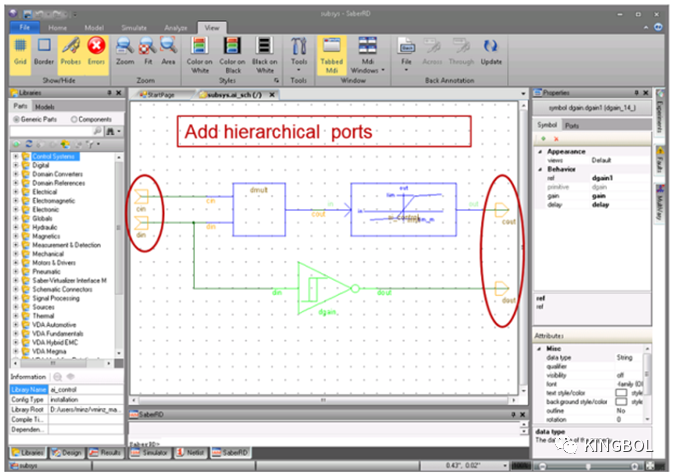

2. 為輸入和輸出添加分層端口

*為了將Saber設計導出到FMU,必須在設計中至少定義一個分層端口。您必須在需要導出為FMU中的輸入/輸出端口的節點上附加一個層次結構端口,如圖2所示。

*Figure 2 *Adding hierarchical ports on schematic

*從部件庫中的Schematic Connectors類別中選擇適當的端口符號,并將其連接到需要導出到FMU的原理圖節點。如果是離散端口和模擬控制端口,請將分級輸入連接器連接到輸入端口,將分級輸出連接器連接到輸出端口。對于物理模擬端口,如電氣和液壓端口,連接分層模擬連接器。

*注意:將錯誤的層次連接器連接到節點將導致FMU導出失敗。在原理圖中添加端口連接器的順序很重要,因為在導出的FMU的modelDescription.xml中定義FMU端口時也使用相同的順序。

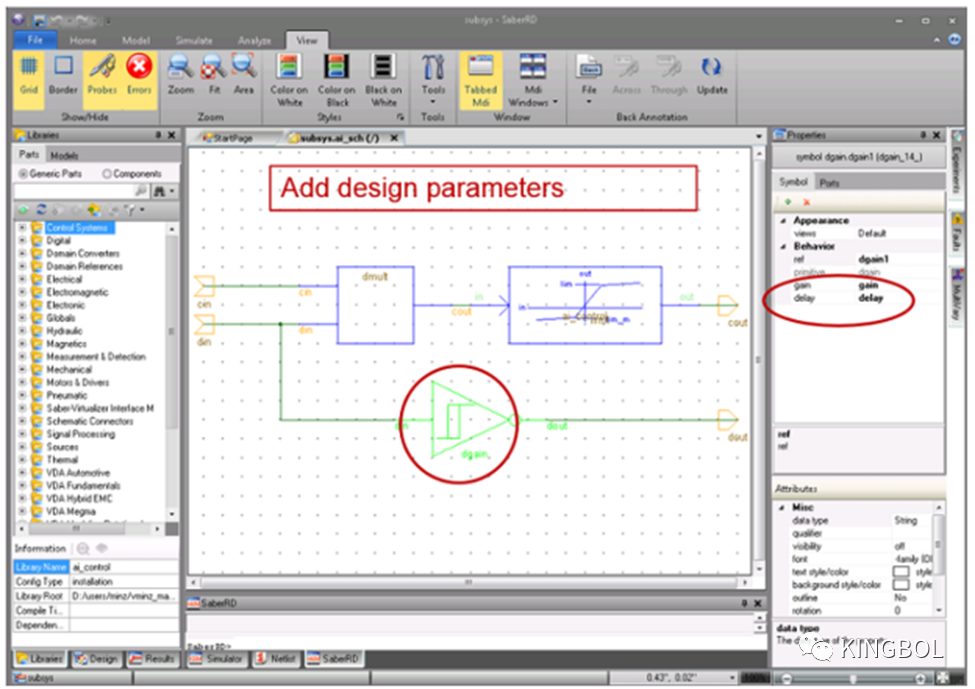

3. 在原理圖中增加設計參數(可選)

*對于任何需要作為設計參數暴露給父模擬器以便在聯合模擬開始時對其進行修改的模型參數,都應該在原理圖上添加設計參數。選擇需要作為模型屬性網格上的參數導出的屬性,并將其值更改為所需的名稱,該名稱將在創建層次符號時用作層次參數。如圖3所示。

*Figure 3 *Adding design parameters on schematic

*注意:只有標量、整數和字符串類型的屬性可以導出為FMU參數。復合類型的模型參數,如MAST結構、數組、VHDL-AMS記錄和向量不允許作為FMU導出的設計參數。

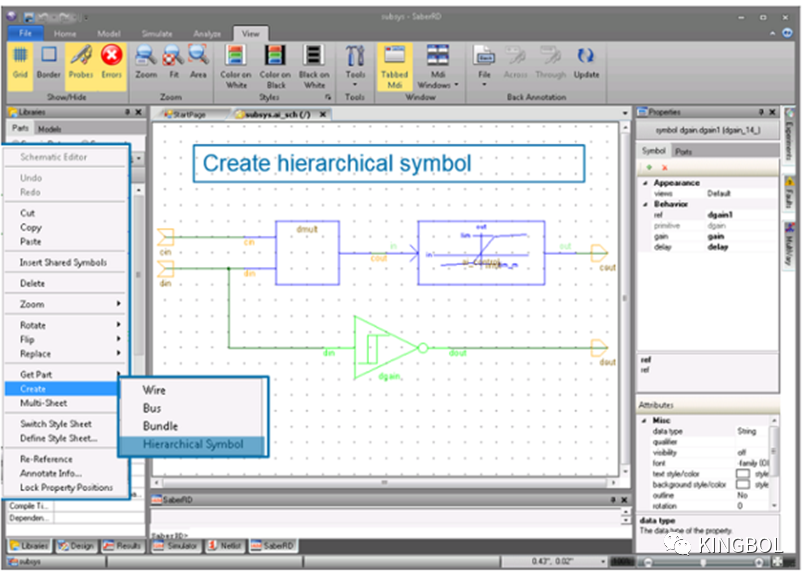

4.為Saber原理圖創建層次符號

*一旦Saber設計的層次原理圖準備好了,在將其導出到FMU之前,需要使用它的層次符號。

*要創建分層符號,右鍵單擊原理圖打開原理圖編輯器Schematic Editor彈出菜單,單擊Create下拉菜單,選擇分層符號Hierarchical Symbol。

*注意:層次符號的名稱必須與Saber設計相同。

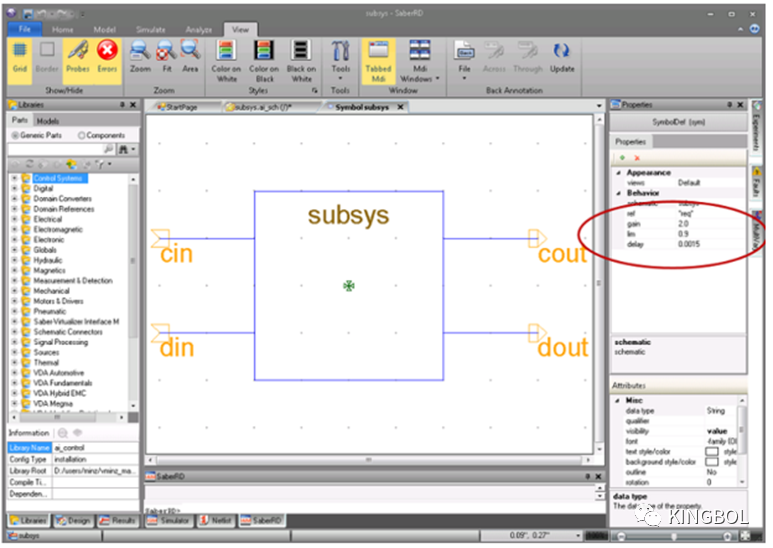

*Figure 4 *Creating hierarchical symbol for schematic

** 5.編輯層次符號(可選 )**

*如果分層設計有任何設計參數或物理模擬端口,生成的符號需要手動更新,如下所示:在分層符號上添加設計參數:

*打開符號編輯器并加載生成的符號。在符號屬性網格上,添加之前在原理圖中添加的所有設計參數,并為它們分配適當的值,如圖5所示。這些屬性可以在父模擬器開始共同模擬時被更改。

Figure 5**Add design parameters on symbol

*更新分層符號上的物理端口方向和類型:對于離散和模擬控制端口,在創建Saber設計原理圖時,在端口連接器上定義輸入/輸出信息。這些類型的端口不需要進一步處理。但是,模擬物理端口能量保守,如電氣或液壓端口有兩個組成部分,單個端口上的通過變量和跨變變量。而且,它們沒有方向信息。

*為了能夠將物理端口導出到FMU,必須提供物理端口的方向和類型信息。

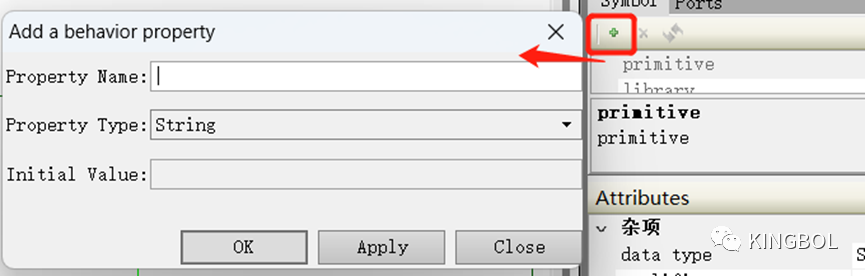

要提供方向和類型信息,請在符號編輯器中打開符號并選擇物理端口。

*單擊“ Properties”窗格上的“Add a behavior property”圖標,在Property Name字段中,輸入因果關系causality,在Initial Value中,提供其方向和類型信息,用空格分隔,如下所示:

*指定模擬端口方向:第一個值指定端口方向,可以是輸入,也可以是輸出。輸入意味著端口從父模擬器讀取值,而輸出意味著端口將數據發送到父模擬器。默認情況下,方向被設置為輸出,這意味著所有物理端口都將數據發送到父模擬器。

模擬端口類型:第二個值表示物理端口的數據類型。要么跨過要么穿過。value, across表示端口與父模擬器交換它的across值,而through表示端口與父模擬器交換它的through值。您還可以使用在MAST或VHDL-AMS中定義的物理單元來指定端口類型。

*添加因果方式的方法如圖6所示:

Figure 6**Adding causality

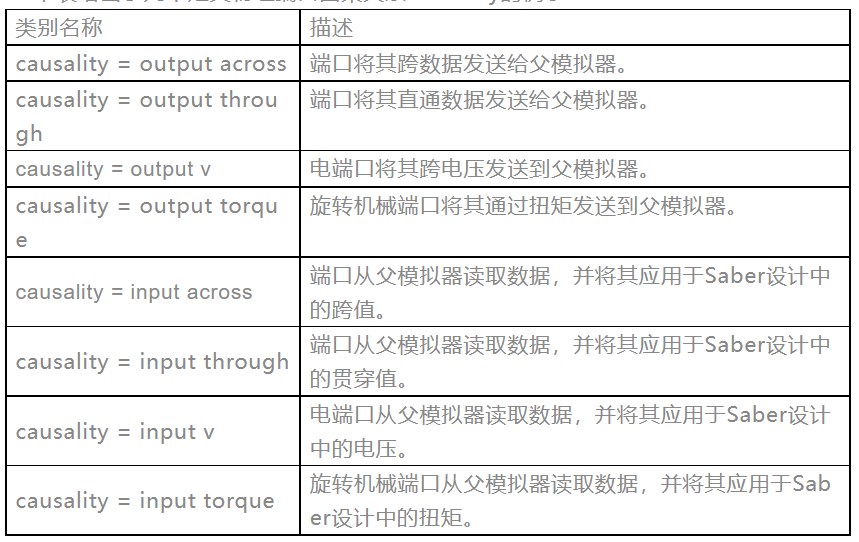

*下表給出了幾個定義物理端口因果關系causality的例子:

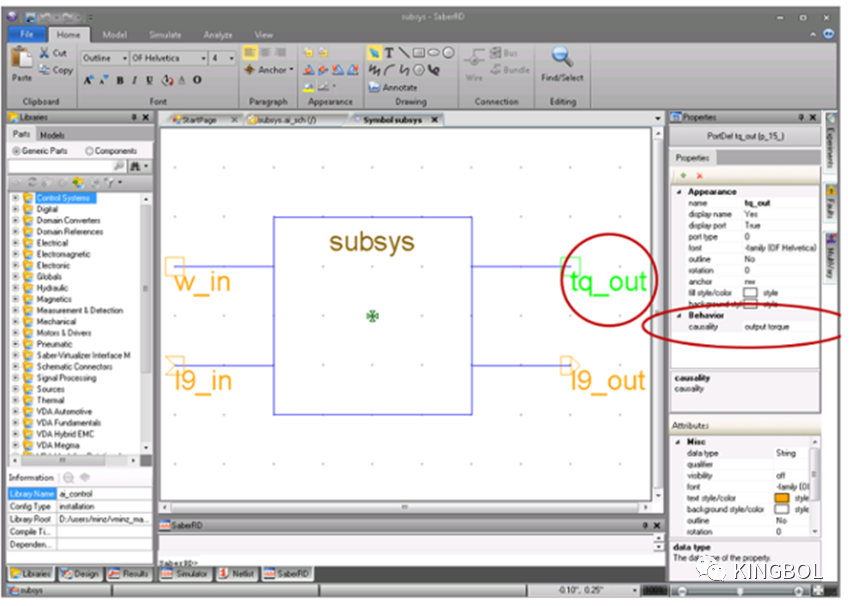

*更新后的物理端口causality屬性如圖7所示:

*Figure 7 **Adding causality *on physical port on symbol

6.驗證SaberRD設計

*當Saber設計就緒時,在將其導出到FMU之前,驗證它在SaberRD中正確工作。

這可以通過創建一個Saber測試來完成,如下所示:

在層次符號的輸入端口上應用刺激,并將適當的負載連接到層次符號的輸出端口。

運行直流和瞬態分析。

確保在模擬過程中沒有錯誤。

如果模擬成功,請檢查模擬結果是否正確。

如果仿真結果正確,Saber設計就可以導出到FMU。

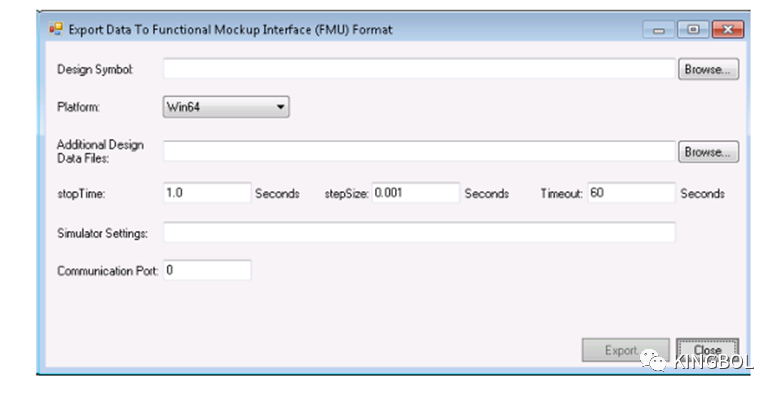

7.導出一個Saber設計到FMU

在SaberRD中選擇“File > Export”,選擇“Function Mockup Interface (FMI)....”系統彈出“Export Data To Functional Mockup Interface (FMU) Format”對話框,如圖8所示。

Figure 8**Saber FMU export

“Export Data To Functional Mockup Interface (FMU) Format”對話框:

Design Symbol: 指定要導出的Saber設計的層次符號名稱,包括其位置路徑。符號必須是等級符號。與符號相關聯的原理圖文件也應該在同一目錄中。這個字段是強制性的,因為層次符號是“將Saber設計導出到FMU”所必需的。

Platform:指定EMU導出到的系統。支持的系統為win64,win32, linux64, linux32。可以任意選擇其中一個平臺,默認是win64。

Additional Design Data Files:除了模型( .sin, .vhdl), symbols ( .ai_sym)和schematic ( .ai_sch),可在此指定所有其他文件,例如TLU(table Look-up)模型的外部數據文件( .ai_dat),這些文件需要使用SaberHDL模擬器運行模擬。如果不需要其他設計數據文件,該字段可以留空。

*stopTime: 指定FMI聯合仿真的停止時間。默認值是1.0秒。

*stepSize:指定聯合仿真期間的通信步長。它必須小于stopTime。默認值是0.001秒。

*Timeout:指定了在共同模擬中完成以下所有任務的最大時間限制,在此時間之后,如果沒有完成,父模擬器將失敗。

*在父模擬器和子模擬器之間建立連接。

*完成一個單獨的溝通步驟,包括以下任務:

*父模擬器將輸入數據發送給子模擬器。

*子模擬器完成給定步長的模擬。

*子模擬器將輸出數據發送回父模擬器。

注意:

1默認值為60秒。2.建議增加復雜Saber設計的超時值,以避免在協同仿真過程中出現不必要的故障,因為完成一個時間點的仿真可能需要更長的時間。

- Simulator Settings:指定SaberHDL模擬器設置。該字段是可選的,默認模擬器設置,如tniter(目標迭代數)和集成順序從SaberHDL模擬器。

在以下情況下,需要指定模擬器設置:

*特定模擬器設置以獲得更好的收斂性:在一些復雜的Saber設計中,可能需要一些特定的高級模擬器設置以獲得更好的收斂性。在將設計導出到FMU之前,需要設置這樣的模擬器設置。在協同仿真過程中使用這些設置來提高收斂性能。例如: dc; tr -tend 1 -tstep 1 us -tniter 10 -order 1

*Saber設計沒有直流解決方案:如果Saber設計沒有直流解決方案,并且需要-trip zero選項來啟動瞬態模擬,則可以在模擬器設置中指定。例如tr -tend 1-tstep 1 ms-trip zero。選項 -trip zero允許導出的FMU在共同模擬期間跳過直流分析。

*保存SaberHDL結果:大多數FMI模擬器刪除FMU解壓縮的臨時目錄。默認情況下,SaberHDL在這個臨時目錄下的resources子目錄中運行模擬,在共同模擬完成后,SaberHDL結果將被刪除。如果您想保存SaberHDL模擬結果,可以使用選項-wdir保存SaberHDL結果。例如,如果你想將Saber結果保存在一個名為saber_results的目錄中,設置應該是:dc;Tr-tend 1-tstep 1u-wdir saber_results。

*在FMU中創建默認實驗:如果你想在modelDescription.xml中創建默認實驗定義,那么可以使用模擬器設置。例如,如果你想創建一個stopTime=5.0, stepSize=0.01的默認實驗定義,那么模擬器設置應該是: dc; tr -tend 5.0 -tstep 0.001.。注意,通信步長是模擬器設置中初始時間步長的10倍。

*Communication Port:指定在共同模擬期間父模擬器和子模擬器之間用于通信的TCP/IP端口。默認值是0,當使用它時,導出的FMU自動找到下一個可用端口。但是,可以指定一個特定的端口來建立通信。

02

限制

以下是FMI 2.0 Co-Simulation接口下FMU導出的限制:

*導出的Saber FMU僅支持win64、win32、linux64和linux32平臺。

*FMU中只支持將標量數字、MAST中的字符串、real、integer和VHDL-AMS中的字符串類型的參數導出為參數。

*只有一些預定義的離散端口,如MAST中的state nu, state logic_4, state fmi_boolean和VHDL-AMS中的signal std_logic支持導出到FMU。

*只有一些連續的因果端口,如MAST中的輸入,ref nu, output, var nu和VHDL-AMS中的quantity in/out real支持導出到FMU。

*僅支持以下預定義物理端口導出到FMU。

*頭文件中定義的所有物理引腳.sin在MAST語言中: electrical, magnetic,thermal_k,thermal_c,rotational_vel,rotational_ang,translational_pos,translational_vel,light,hyd_mks,pneumatic.

*VHDL-AMS中定義的性質: electrical, magnetic, rotational, rotational_velocity, translational, translational_v, fluidic, thermal, thermal_c, radiant.

*物理端口默認只導出一個組件到FMU。物理端口有兩個組件,跨變量和通過變量。但是,默認情況下,只有一個組件被導出到FMU。這是通過在符號端口上添加因果關系行為來實現的,例如,交叉輸入或通過輸出。如果您希望將兩個組件都導出到FMU,在導出FMU之前,請使用ai_conversion庫中的域轉換模型將跨變量和通過變量轉換為Saber設計中的控制變量端口。這將跨組件和通過組件導出到FMU。

*沒有提供源代碼。

*導出的FMU不提供輸出變量的導數。

*在一個設計中只能實例化一個Saber FMU。

*導出的FMU不能序列化FMU狀態。

*導出的FMU不能使用內存管理功能。

03

Saber FMU實例

Saber FMU實例概述

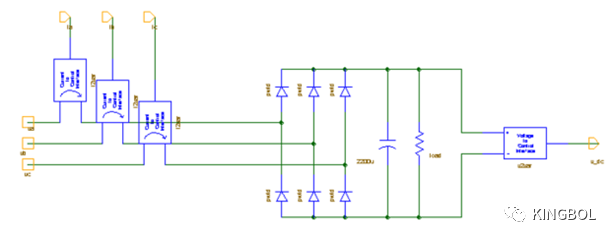

圖9顯示了三相整流器的Saber設計示例。

設計可以在SaberRD安裝目錄examples/OtherExamples/FMI2.0/export_cs/ precfier_3p中找到。

本設計有兩個設計參數:

*von:六個開關器件的導通壓降。默認值是0.7V。

load:輸出級的電阻性負載。默認為0.5歐姆。

本設計有三個電壓輸入接口:

*va,vb,vc:這三個輸入都是物理電結點,沒有方向。我們希望從父模擬器獲得這些端口的跨接電壓輸入。因此,在這三個符號端口上需要一個屬性,與輸入值之間的因果關系。

本設計有四個輸出端口:

*ia,ib,ic:這三個節點將相電流發送回父模擬器。它們是連續的模擬輸出,具有輸出的因果關系,不需要在這些符號端口上添加特定的因果關系

*v_dc:這個節點是整流器的輸出電壓,它已經從兩個差分電壓轉換成一個控制信號。它有輸出的方向,所以不需要為它定義因果關系

Figure9**Three-Phase Rectifier Example

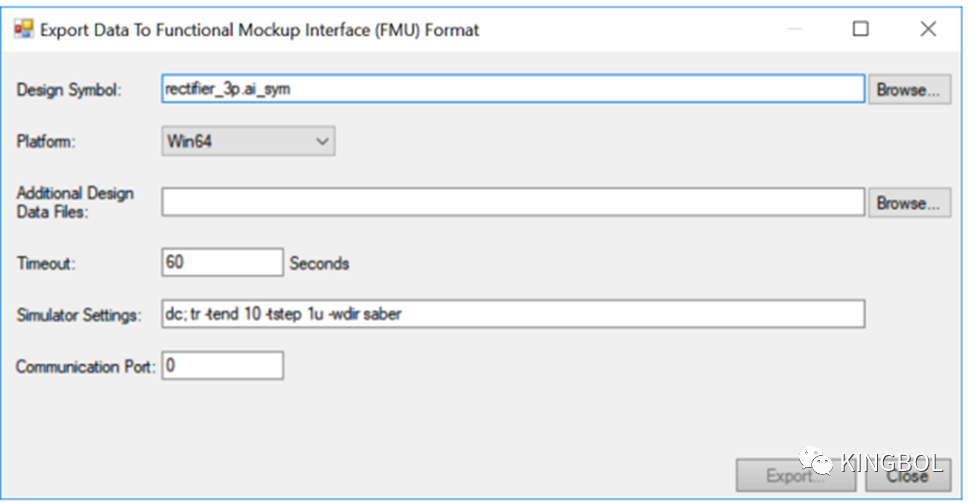

輸出Saber 示例設計到FMU

要將Saber示例設計導出到FMU,請執行以下步驟:

1.將rectifier_3p示例從安裝文件夾復制到本地目錄。

2.調用SaberRD并打開這個設計。

3.導出rectifier_3p_saberhdl.fmu。

*選擇File->Export,選擇Functional Mockup Interface (FMI)....系統彈出“Export Data To Functional Mockup Interface (FMU) Format”對話框。

*選擇rectifier_3p.ai_sym為Design Symbol。

*Simulation Settings設置為:dc;tr -tend 10-tstep 1u -wdir saber。

*單擊Export,rectifier_3p saberhdl.fmu在同一目錄下生成

Figure 10**Export Data To Functional Mockup Interface (FMU) Format

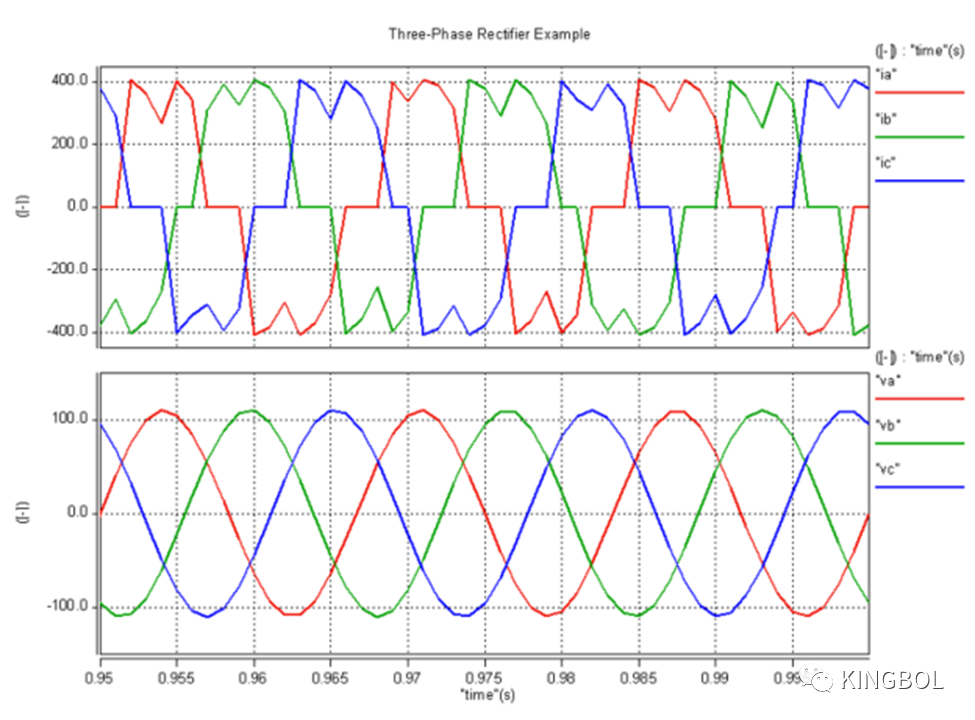

仿真導出的Saber FMU

*任何FMI模擬器都可以用來測試導出的FMU,rectifier_3p. fmu。

*在FMI標準頁面上有許多可用的工具:https://fmi-standard.org/download

*在這個例子中,使用了一個免費的模擬器fmuChecker。

*要運行這個示例,請執行以下步驟:

1.將環境變量SABER_FMU_SOLVER設置為Saber的安裝路徑。例如,C:SynopsysSaberRD64P-2019.06.

2.運行64位版本的fmuChecker: fmuCheck.win64.exe -e log.txt -i v_3p.csv -o result.csv -s 2 -h 1e-3 -n 0 rectifier_3p_saberh.fmu

它運行瞬態模擬2秒,通信步長為1e-3。輸出信息保存在log.txt文件中,仿真結果保存在result.csv文件中。

3.在任何兼容的波形查看器(如Scope)中打開result.csv文件。

*結果如圖11所示。

*Figure 11 *Three-Phase Rectifier Results

-

連接器

+關注

關注

98文章

14345瀏覽量

136200 -

仿真器

+關注

關注

14文章

1016瀏覽量

83647 -

VHDL語言

+關注

關注

1文章

113瀏覽量

17988 -

模擬器

+關注

關注

2文章

870瀏覽量

43167 -

AMS

+關注

關注

10文章

209瀏覽量

86976

發布評論請先 登錄

相關推薦

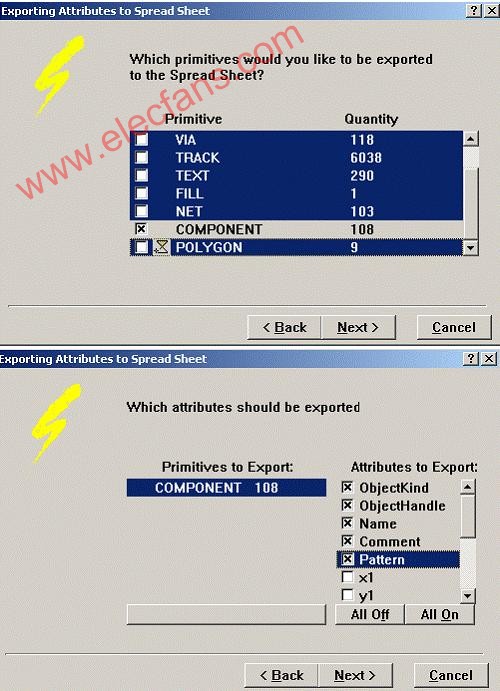

如何在Protel軟件中導出元件清單

matlab中導出數據為txt文件~~ 怎么導出二維數組中的一列

關于PCB EDITOR 中導入DXF文件的問題

怎么從一個項目的文件中導出原理圖庫和pcb庫

如何使用VSCODE編輯Keil中導出的代碼

如何從PADS-LAYOUT中導出BOM清單方法

LabVIEW中導出波形圖或圖表至文件

OrCAD將原理圖中導出并保存至器件庫的詳細步驟

在SaberRD中導出FMU的步驟詳解

在SaberRD中導出FMU的步驟詳解

評論