串擾是芯片后端設計中非常普遍的現象,它會造成邏輯信號的預期之外的變化。消除串擾的影響是后端的一個重要課題。

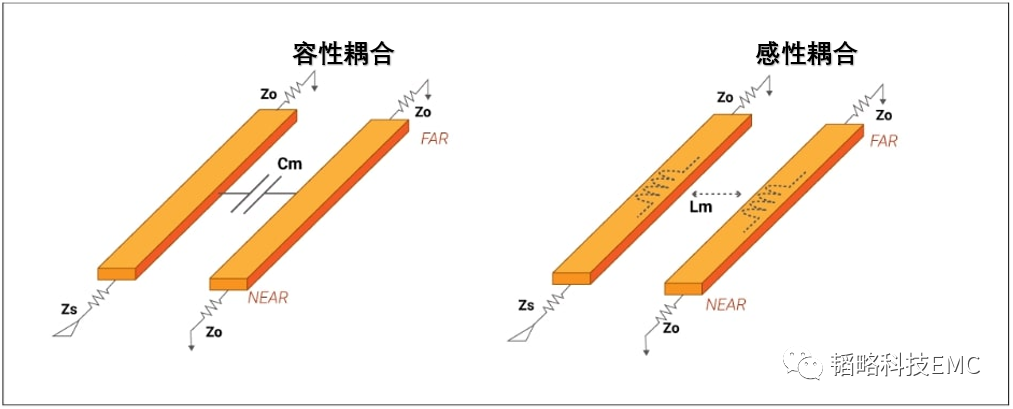

首先,什么是串擾?它是如何產生的?芯片的信號線之間會存在耦合電容,因此一條信號線的變化會影響周圍的線(信號線之間的耦合電感一般可以忽略)。

對于工程師來說了解這么多就可以了,不過這樣的解釋有點循環論證的感覺,因為耦合電容就是因為兩端金屬線互相影響而抽象出來的概念。

最根本的原因就是一條信號線的跳變會造成周圍空間電磁場的變化,而變化的電磁場會在周圍的導線感應出電流。

十幾年前老的工藝可能還可以忽略寄生電容,現在的先進工藝下寄生電容已經到了萬萬不可忽略的地步了,不過對于電感好像還是不會過多考慮。

兩段很近的導線發生串擾時,假設一段導線從0跳變為1,會影響另一段導線電勢小幅上升一點,再回落下來。我們稱產生跳變的導線為attacker,受影響的導線為victim,那一小段電勢的變化稱為glitch。

相應的,如果attacker從1變0,victim會有一個電勢下降的glitch。如果這個glitch過大,就可能產生一個錯誤的邏輯信號出來,這個時候就發生了glitch的violation。

Attacker和victim的角色是可以互相轉化的,一個victim在需要翻轉的時候就成為了attacker,attacker信號保持不變的時候就是victim。如果兩段信號線同時反轉,他們就都既是attacker又是victim。

Glitch violation也是信號完整性(SI,signal integrity)violation的一種,SI據我所知也就只和crosstalk有關。

另一種情況,如果attacker和victim同時跳變,如果attacker和victim的跳變方向一致,比如說都從0變為1,victim受attacker的影響跳變速度會更快一些,也就是transition/slew time更小。注意這個時候兩者都既是attacker也是victim,所以兩根導線的transition都會變快。

相反地,如果attacker和victim跳變方向不同,transition會變慢。Transition的變化可能會產生timing的violation,這一類violation也可以說是由SI帶來的。但是一般這種violation不如glitch來的嚴重。

一種比較嚴重的violation叫做DS(double switch),也是由于串擾帶來的邏輯錯誤。

就是說attacker和victim同時跳變并且方向相反,假設attacker從1到0,victim從0到1,假設某個時刻victim已經過了邏輯1的電壓閾值,后面的cell已經可以捕捉到信號1了,但之后由于crosstalk,victim的電勢會有一個向下(邏輯0方向)的glitch。

而這個glitch可能導致后級cell捕捉到信號0,之后victim電勢再升高為邏輯1,所以總的來說victim的信號傳播就從0、1變為0、1、0、1.這就叫做double switch violation。

消除SI violation的方法還是要從繞線著手。第一就是加shielding net,就是在attacker旁邊加一段地線,稱為shielding,減弱attacker與victim的耦合電容。

一般的時鐘trunk都會加一定比例的shielding。第二種就是把發生violation的兩段shape分開,距離越遠越好,具體做法可以把很直的一段shape讓它拐一下,做個detour出來。

第三種就是把其中一個net換到另一層去,因為我們metal layer的preferred routing direction都是一層橫的一層豎的,換層之后能有效減少耦合電容。

-

芯片設計

+關注

關注

15文章

1005瀏覽量

54819 -

信號完整性

+關注

關注

68文章

1398瀏覽量

95391 -

寄生電容

+關注

關注

1文章

291瀏覽量

19195 -

電磁場

+關注

關注

0文章

790瀏覽量

47236 -

感應電流

+關注

關注

0文章

88瀏覽量

11931

發布評論請先 登錄

相關推薦

高頻電路設計中的串擾問題

嵌入式開發中引起串擾的原因是什么?

串擾產生的原因是什么

在PCB設計中,如何避免串擾?

PCB產生串擾的原因及解決方法

如何使用SigXplorer進行串擾的仿真

怎么樣抑制PCB設計中的串擾

什么是串擾crosstalk?它是如何產生的?

什么是串擾crosstalk?它是如何產生的?

評論