作為現代科技的基石,半導體已經滲透到各個領域。無論是智能手機、電動汽車,還是物聯網、人工智能,都關注半導體的應用。隨著科技的持續發展和對高性能、高效能產品需求增長,半導體市場的前景將持續迎來巨大的增長。據臺積電預測,到2030年,全球半導體產值將達到1萬億美元。

11月23日,在上海浦東臨港新片區,在由臨港新片區管委會、上海市經濟信息化委指導,由臨港集團主辦、臨港科投與AspenCore承辦的“2023中國臨港國際半導體大會”上,臺積電(中國)有限公司副總經理陳平博士以“半導體制程技術發展趨勢”為主題,就工藝技術/制程技術發展以及趨勢進行了分享。

顛覆式創新“生成式AI”出現,計算無所不在

陳平博士認為,生成式AI的橫空出世成為了劃時代顛覆式的應用,重要意義不亞于計算機誕生與互聯網誕生,甚至瓦特蒸汽機。他表示,大數據、大模型、大算力是支持生成式AI基礎的三大要素,前兩個部分是AI科學家的工作,而提供支持大算力的晶體管,則是制造企業的工作。

盡管Chat GPT是去年9月份才出現,至今僅一年多時間就已發生了兩次迭代,同時端側已經有很多應用應運而生,如高通發布的新的驍龍 8 Gen 3 SoC和聯發科天璣8300,已經在端側算力提高到新的高度。陳平博士預測大模型將很快在智能手機,PC,平板端落地。

而在智能汽車應用上,在過去的兩年,中國汽車在電氣化上面已做出了很大的進展,此外,隨著大模型AI的出現,汽車智能化程度預計也會迎來突飛猛進的發展,同時也給半導體工藝提出了挑戰。

大算力對芯片工藝提出更高要求

無論是云端,還是在端側的應用,生成式AI將對半導體工藝提出了高算力和高能效比的要求。大算力是支撐大模型的一個必要條件,而大算力對于工藝來說就是更高的集成度,在單位面積里集成更多的晶體管。高能效比則是為了降低整體成本,如在數據中心中,目前主要成本是電和冷卻,若器件端功耗可降低20-30% ,對整體成本而言影響是巨大的。

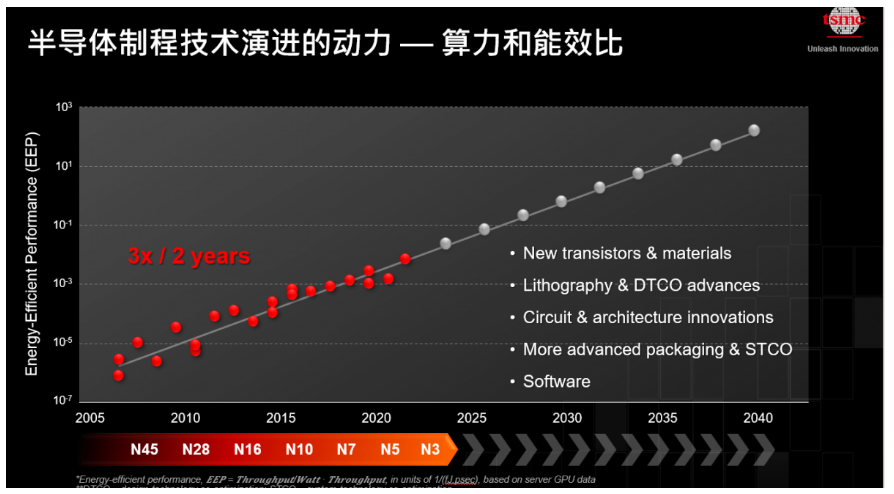

用GPU運算的算力除上單位功耗算力的能效來看,2005年到現在是每兩年有3倍的增長。

陳平博士指出,如果我們用能效比去看,其實我們一直在摩爾定律這條曲線上,而且往前還必須沿著這個曲線前進。

那芯片如何才能不斷實現高算力和高能效比的提升?陳平博士指出有兩大元素,首先是傳統工藝制程微縮上繼續前行,再者是2.5D、3D整合。他認為這些微縮本身給我們提供了最有效的算力密度和能效比的提升。

而針對Chiplet能否取代先進工藝的爭論,陳平博士直言不行“Chiplet只是擴展了芯片,但是改變不了芯片的品質,就是能效比和算力密度,所以我們需要繼續提升。現在3納米已經進入了大規模量產,2納米看起來也已經呼之欲出了。再繼續往下,我們的工藝工程師還在繼續往前在努力。”

此外,制程與設計協同優化 (DTCO)成為必要。DTCO的核心就是設計工程師與光刻工程師共同協作,尋找最佳的設計和光刻工藝方案。這個方案要既能滿足器件性能的要求,又能在Fab里實現。陳平博士介紹:“從7納米開始大概有25%的工藝是基于DTCO的,到5納米的時候就到40%,到3納米就更多。也就是說,我們在設計和工藝協同下面達到最好的輸出,不拘泥于一些很機械的參數。那些說摩爾定律死的人很多是拘泥于摩爾在某一個時代的定義,其實我們對那個已經沒有太大的興趣。”

微縮工藝還能發展多久呢?陳平表示他對人類的智慧和工程師的創造性充滿自信。目前制程工藝在FinFET節點上,28納米是平面結構最后一代,到16納米,12納米引用了新的晶體管結構一直用到7納米,5納米,3納米,現在又碰到了新的挑戰,陳平表示:“臺積電在2納米上會引入所謂Nanosheet,類似于GAA結構。在2納米以后現在有一種結構叫CFET,再往后還有很多新的黑科技,所以大家要對半導體科學工作者有信心,就是往前走我們還沒有看到盡頭在哪里。”

3D系統集成將成為先進工藝的重要組成部分

回顧半導體的發展歷史,1947年貝爾實驗室發明晶體管,1960年德州儀器發明了集成電路,把晶體管和一些小型電路集成在一起,到2010年左右的時候,開始把集成電路集成在一起,發展到3D堆疊和2.5D先進封裝技術。

陳平博士表示,隨著數字化時代數據量的快速增加,SoC上的微縮已不足以滿足系統發展的需要。3D系統的引入將使得在SoC工藝基礎上大幅擴展集成度,實現所謂的Chiplet,同時,2.5D和3D工藝可以幫助實現異構集成,讓邏輯芯片和存儲芯片得以方便地集成在一起。因此,2.5D和3D系統集成已成為先進工藝的有機組成部分。

據介紹,臺積電的3D堆疊封裝技術有兩種,一種是wafer on wafer的堆疊,還有一種是chip on chip的堆疊,chip on chip的堆疊叫SoIC。臺積電的平行的整合就是2.5D,其中比較有名的是2012年臺推出的CoWoS工藝,還有iPhone里面的info,都是屬于2.5D的技術。

CoWoS技術面臨的最大挑戰是大型模型對計算的高要求。目前,CoWoS把邏輯和存儲芯片平行放置在一個中介層上,臺積電計劃于2025年將中介層的尺寸增加到六個六分之一掩模版,是目前的3.3倍。

而3D堆疊技術提供了更高的集成度,更好的帶寬,更好的性能,已可將十幾個HBM堆疊在一起。

另外,由于計算的引入,光電器件也成為了熱門,陳平表示:“由于計算的結果要通過光學網絡傳遞出去,因此光和電之間的集成整合也是給我們平臺提出了一個需要。”

陳平介紹到,目前的計算體系大概分為幾個層次。第一個層次是計算單元,比如GPU和DSA,通過3D打印技術整合在一起,這是最底層的計算部分,在這個部分,要實現最好的能效比,不僅涉及到邏輯工藝,還包括供電,如現在最熱的概念IBR,也是為了提高能效比。最終的計算需要依靠大數據和大的內存實現,而內存的集成是下一級的集成。最終,還需要進行單個相集成,直接將計算與光學結合。

上述系統非常復雜,需要使用系統架構的共同優化(STCO),這比DTCO更復雜。陳平博士表示:“如果使用先進的工藝和技術加上STCO設計,有可能會降低幾個數量級,這是我們在工藝上目前正在努力實現的目標。”

最后,陳平博士總結表示,顛覆式技術的出現使半導體含量持續增加,算力和能效比需求的不斷提升驅動制程技術發展,他指出制程技術發展趨勢主要有三點:首先是器件微縮和2.5D/3D系統集成并行發展;其次,電學與光學技術的結合,同時提升算力、運力、存力各類產品的性能;最后,DTCO/STCO技術,推動系統、設計、制程的協同發展。

-

大數據

+關注

關注

64文章

8863瀏覽量

137303 -

大模型

+關注

關注

2文章

2330瀏覽量

2486 -

生成式AI

+關注

關注

0文章

488瀏覽量

459

發布評論請先 登錄

相關推薦

臺積電:半導體制程技術發展的三大趨勢

臺積電:半導體制程技術發展的三大趨勢

![[<b class='flag-5'>半導體</b>前端工藝:第二篇] <b class='flag-5'>半導體制程</b>工藝概覽與氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

評論