共讀好書

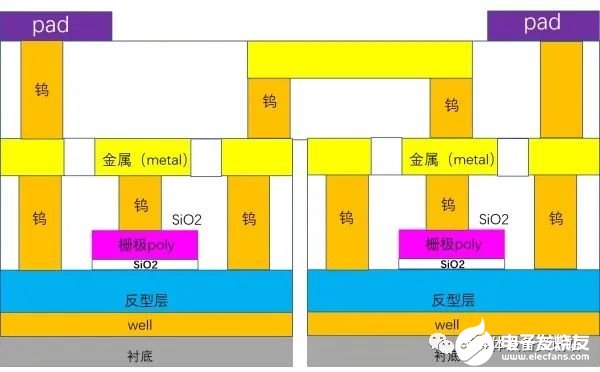

你即使從來沒有學(xué)過物理,從來沒學(xué)過數(shù)學(xué)也能看懂,但是有點(diǎn)太簡單了,適合入門,如果你想了解更多的CMOS內(nèi)容,就要看這一期的內(nèi)容了,因為只有了解完工藝流程(也就是二極管的制作流程)之后,才可以繼續(xù)了解后面的內(nèi)容。那我們這一期就了解一下這個CMOS在foundry公司是怎么生產(chǎn)的(以非先進(jìn)制程作為例子,先進(jìn)制程的CMOS無論在結(jié)構(gòu)上還是制作原理上都不一樣)。

首先要知道foundry從供應(yīng)商(硅片供應(yīng)商)那里拿到的晶圓(也叫wafer,我們后面簡稱wafer)是一片一片的,半徑為200mm(8寸廠)或者是300mm(12寸廠)的晶圓。如下圖,其實就是類似于一個大餅,我們把它稱作襯底。

但是呢,我們這么看不太方便,我們從下往上看,看截面圖,也就是變成了下圖這個樣子。

下面我們就看看怎么出現(xiàn)我們上一期提到的CMOS模型,由于實際的process需要幾千個步驟,我在這里就拿最簡單的8寸晶圓的主要步驟來聊。

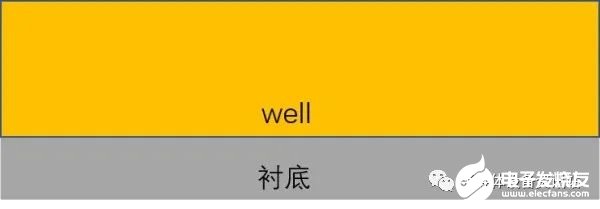

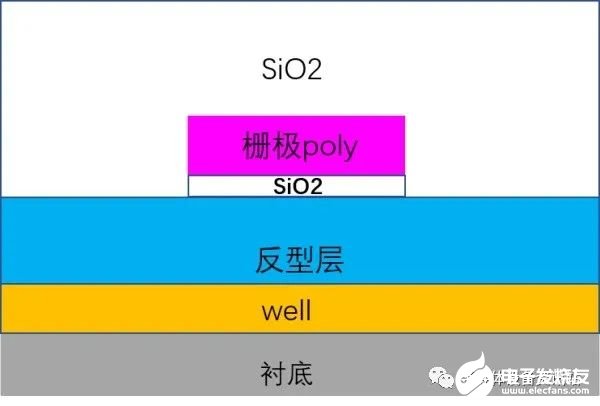

制作Well和反型層:

也就是通常說的阱,well是通過離子植入(Ion Implantation,后面簡稱imp)的方式進(jìn)入到襯底上的,如果要制作NMOS,需要植入P型well,如果制作PMOS,需要植入N型well,為了方便大家了解,我們拿NMOS來做例子。離子植入的機(jī)器通過將需要植入的P型元素打入到襯底中的特定深度,然后再在爐管中高溫加熱,讓這些離子活化并且向周圍擴(kuò)散。這樣就完成了well的制作。制作完成后是這個樣子的。

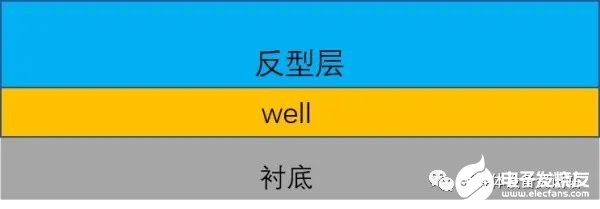

在制作well之后,后面還有其他離子植入的步驟,目的就是控制溝道電流和閥值電壓的大小,大家可以統(tǒng)一叫做反型層。如果是要做NMOS,反型層植入的是P型離子,如果是要做PMOS,反型層植入的是N型離子。植入之后是下面這個模型。

這里面有很多內(nèi)容的,比如離子植入時的能量,角度,離子的濃度等等,那些不在這一期當(dāng)中,而且我相信你了解那一些的話,肯定是圈內(nèi)人,你肯定有方法了解到。

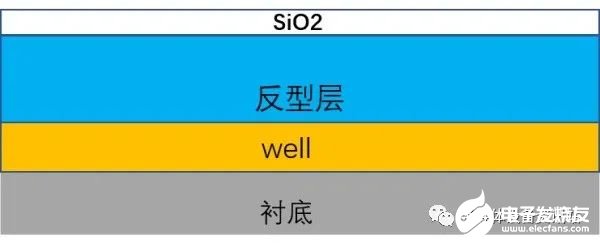

制作SiO2:

后面就會制作二氧化硅(SiO2,后面簡稱Oxide),在CMOS的制作流程中,制作oxide的方法有很多。在這里由的SiO2是用在柵極下面的,它的厚度直接影響了閥值電壓的大小和溝道電流的大小。所以大多數(shù)foundry在這一步都是選擇質(zhì)量最高,厚度控制最精確,均勻性最好的爐管氧化方法。其實很簡單,就是在通氧氣的爐管中,通過高溫,讓氧氣和硅發(fā)生化學(xué)反應(yīng),生成SiO2。這樣就在Si的表面生成了薄薄的一層SiO2,如下面的圖形。

當(dāng)然這里面也有很多具體的信息,比如需要具體多少度啊,需要多少濃度的氧氣啊,需要高溫多長時間啊等等,這些都不是我們現(xiàn)在考慮的,那些太具體了。

柵端Poly的形成:

但是到這里還沒結(jié)束,SiO2只是相當(dāng)于螺紋,真正的柵極(Poly)還沒有開始做呢。所以我們下一步就是在SiO2上面鋪一層多晶硅(多晶硅也是單一的硅元素組成,但是晶格排列方式不同。你千萬不要問我為什么襯底用單晶硅,柵極用多晶硅,這個有一本書叫半導(dǎo)體物理,您可以了解下,尷尬~)。Poly也是CMOS非常關(guān)鍵的一個環(huán)節(jié),但是poly的成分是Si,不能像生長SiO2那樣通過直接和Si襯底直接反應(yīng)生成。這就需要傳說中的CVD(化學(xué)氣相沉淀,Chemical Vapor Deposition),就是在真空中發(fā)生化學(xué)反應(yīng),將生成的物體沉淀到wafer上,在這個例子中,生成的物質(zhì)就是多晶硅,然后沉淀到wafer上(這里要多說一句,poly是用CVD的方法在爐管中生成的,所以poly的生成不是用的純正CVD的機(jī)臺)。

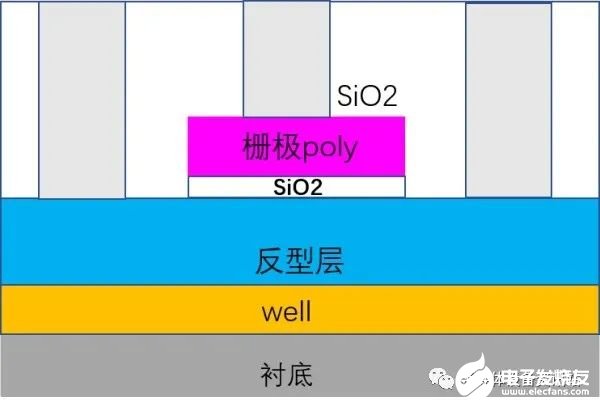

但是這種方法形成的多晶硅會在整片wafer都沉淀下來,沉淀之后是這個樣子。

Poly和SiO2的曝光:

到了上面這一步,其實已經(jīng)形成我們想要的垂直結(jié)構(gòu)了,最上面是poly,下面是SiO2,再到下面是襯底。但是現(xiàn)在整片wafer都是這樣,其實我們只需要一個特定位置是“水龍頭”結(jié)構(gòu)。于是就有了整個工藝流程中最最關(guān)鍵的一步—曝光。

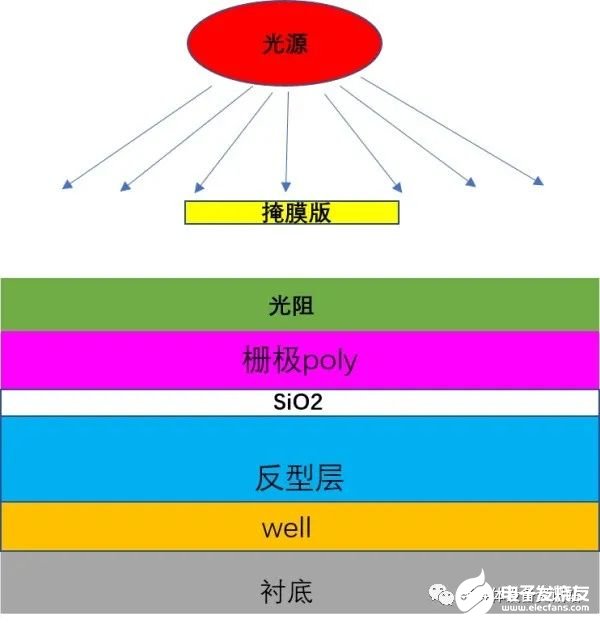

我們先在wafer表面鋪一層光刻膠,也叫光阻(很難解釋光刻膠的概念是什么,我相信你看著看著就懂了)就變成了這個樣子。

然后再用定義好的掩膜版(掩膜版上已經(jīng)定義好了電路圖形)放在上面,最后用特定波長的光線照射,被照射的地方光阻會變活化,由于被掩膜版擋住的地方?jīng)]有被光源照到,所以這塊光阻沒有被活化。

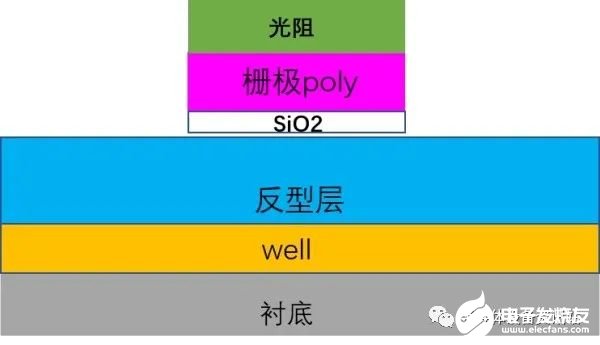

由于被活化的光刻膠特別容易被特定化學(xué)液體洗掉,而沒有被活化的光刻膠不能被洗掉,所以通過照射后,再用特定的液體洗掉已經(jīng)活化的

膠,最后就變成了這個樣子,在需要保留Poly和SiO2的地方留下光阻,在不需要保留的地方除去光阻。

Poly和SiO2的刻蝕:

這之后就是把那些多余的Poly和SiO2刻蝕掉,也就是除去掉,這個時候使用的是定向刻蝕。在刻蝕的分類中,有一種分法是定向刻蝕和非定向刻蝕,定向刻蝕就是指在某個特定方向進(jìn)行刻蝕,而非定向刻蝕就是不定向的(一不小心又說多了,總之就是通過特定的酸堿,在某個特定的方向除去SiO2)。在這個例子中我們采取向下的定向刻蝕除去SiO2,變成了這個樣子。

最后再除去光阻,這個時候除去光阻的方法就不是上面提到的通過光的照射活化,而是通過其他方式,因為我們不需要在這個時候定義特定的大小,而是將光阻全部除掉。最后變成如下圖所示。

這樣我們就完成了保留特定位置Poly個SiO2的目的。

源端和漏端的形成:

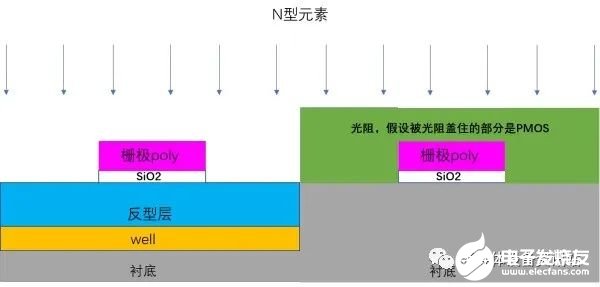

最后我們再考慮一下源端和漏端是怎么形成的。大家還記得在上一期中我們聊過,源端和漏端都是離子植入相同類型的元素。這個時候,我們可以在需要植入N型的源/漏區(qū)域上用光阻開口。由于我們是只拿NMOS做例子,所以上圖中的所有部分都會開口,如下圖

由于被光阻蓋住的部份是不能被植入的(光阻擋著了嘛),所以只有在需要的NMOS上才會植入N型元素。由于poly下面的襯底被poly和SiO2擋住,所以也不會被植入,于是就變成了這個樣子。

到這里,一個簡單的MOS模型就制作出來了,理論上來講,在source,drain,poly和襯底上加上電壓,這個MOS是可以工作的,但是我們總不能直接在source和drain拿個探針直接加上電壓吧。這個時候就需要MOS的布線,也就是在這個MOS上面,連導(dǎo)線,讓很多MOS連在一起。我們就看看這個布線的過程。

制作VIA:

首先第一步就是在整個MOS上蓋一層SiO2,如下圖

當(dāng)然這個SiO2是通過CVD的方式產(chǎn)生的,因為這樣速度會很快,很節(jié)省時間。下面的話還是鋪光阻,曝光的那一套,結(jié)束之后是長這個樣子。

然后再用刻蝕的方法在SiO2上刻蝕出一個洞,如下圖灰色的部分,這個洞的深度直接接觸Si表面。

最后再除去光阻,得到下面的樣子。

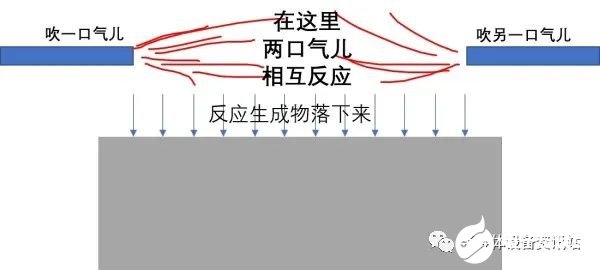

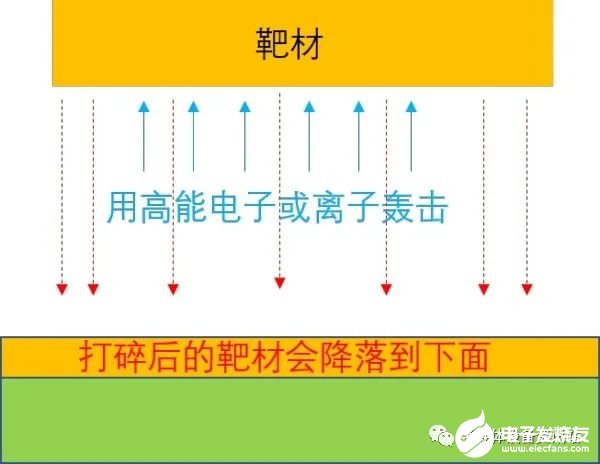

這個時候要做的就是在這個洞里填導(dǎo)體,至于這個導(dǎo)體是什么?各家都不一樣,大部分都是鎢(Tungsten)的合金,那怎么才能填好這個洞呢?用的是PVD(Physical Vapor Deposition,物理氣相沉淀)的方式,原理類似于下圖。

使用高能量的電子或離子轟擊靶材,被打碎的靶材,會以原子的形式降落到下面,就這樣形成了下面的鍍膜。我們平時看新聞中提到的靶材就是指這里的靶材。

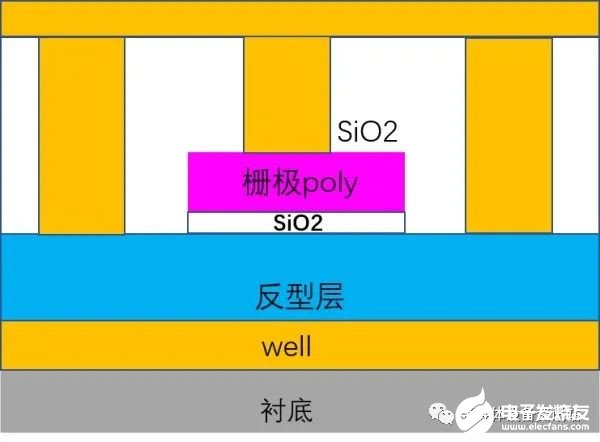

填完洞之后,就長這個樣子。

當(dāng)然我們在填的時候,不可能控制鍍膜的厚度正好等于洞的深度,所以會多余一些,這樣就用到了CMP(Chemical Mechanical polishing,化學(xué)機(jī)械研磨)技術(shù),聽起來很高大上,其實就是磨,將多余的部分都給磨掉。結(jié)果就是這個樣子。

到了這里我們就完成了一層via的制作,當(dāng)然,via制作主要是為了后面的金屬層布線。

金屬層制作:

在上面這個條件下,我們用PVD的方式再dep一層金屬(metal)。這個金屬主要是以銅為主的合金。

然后再經(jīng)過曝光,刻蝕,得到我們想要的樣子。然后不斷的往上疊加,直到滿足我們的需求。

我們在畫layout時,會告訴你使用的工藝最多有多少層metal,多少層via,就是指它可以疊加多少層。

最終就得到這樣的結(jié)構(gòu)。最上面的pad就是這顆芯片的引腳,封裝之后就成了我們能看到的管腳(當(dāng)然我這是胡亂畫的,沒有什么實際意義,只是為了舉例子)。

這就是一顆芯片制作的大概流程。這一期我們了解了半導(dǎo)體foundry中最重要的曝光,刻蝕,離子植入,爐管,CVD,PVD,CMP等等

審核編輯 黃宇

-

CMOS

+關(guān)注

關(guān)注

58文章

5680瀏覽量

235136 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27003瀏覽量

216265 -

光刻

+關(guān)注

關(guān)注

8文章

318瀏覽量

30115

發(fā)布評論請先 登錄

相關(guān)推薦

簡述半導(dǎo)體超純水設(shè)備工藝流程及標(biāo)準(zhǔn)參考分析

SMT貼裝基本工藝流程

倒裝晶片的組裝工藝流程

半導(dǎo)體材料的工藝流程

smt工藝流程圖

功率半導(dǎo)體分立器件工藝流程

半導(dǎo)體圖案化工藝流程之刻蝕(一)

這可能最簡單的半導(dǎo)體工藝流程

這可能最簡單的半導(dǎo)體工藝流程

評論