通常在理想狀況下,如果mos管關斷時是不流過電流的。但漏/源與襯底之間是兩個pn結。即使mos管沒有溝道,漏源之間還是有反向的飽和電流,這就是所謂的漏電流。由于漏電流的存在,整個電路的靜態功耗會有所增加.正常一般都在uA級別吧.

下面時我能想到的異常漏電幾種情況:

?門電路的輸入端懸空,有可能導致PMOS和NMOS同時導通,存在短路電流,如果MOS管的尺寸越大表現出來的漏電流就越大.

?buffer輸入高阻態,電位不固定.

?發生了latchup .

?之前遇到foundry rule不完善,導致添加AA(OD) dummy不合理導致漏電問題.

?芯片物理性的損壞.

這次芯片回片測試時發現系統進入sleep模式后漏電異常,幾個毫安級.不正常!分析發生latchup的可能性不大,大概率時有門級輸入懸空或高阻態.

產生輸入floating或高阻,在電路或版圖上有哪些場景?

先說floating gate,其實這個地方是有坑的,我們習慣認為這個問題可以在drc或lvs驗證中cover住.

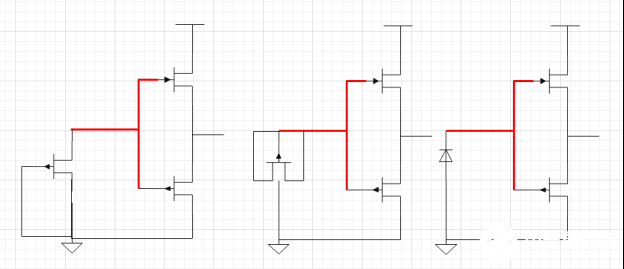

But意外往往都是這么發生的.根據經驗教訓下面有些場景在drc lvs中無法檢查到.上圖畫visio圖不熟練:

我們認為紅色gate輸入端雖然接diode或ggnmos或mosbase dio但電位還是不固定的,仍然floating的,但是drc lvs都不會報錯.風險越留到后面,修改的代價就越大.設計階段需要介入排除.

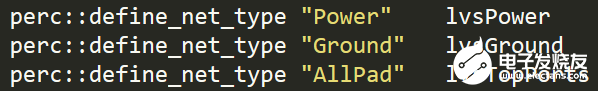

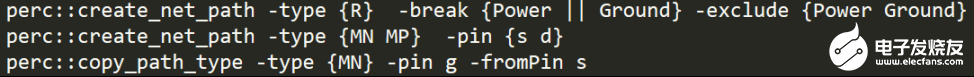

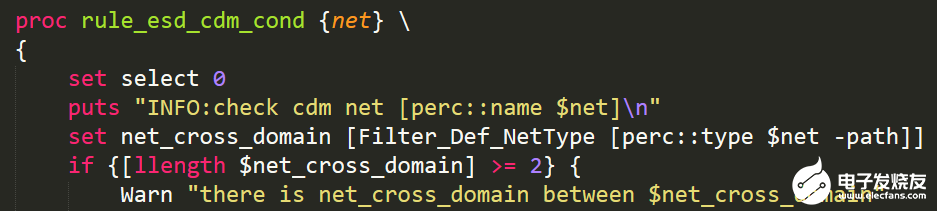

對此問題可以定制perc rule排除.

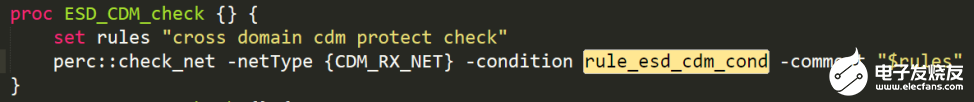

我們這個問題有些相似,原因是sleep模式關掉LDO輸出,但是沒有下拉到地.后一級buffer電壓常在不掉電,從而導致漏電發生,檢查方式需要檢查是否有net跨不同的電源域,電路設計分析前后級電源上下電關系判斷是否有風險.

對此問題也可以定制perc rule排除.

簡述下流程:

定義net type

芯片回片后出現漏電,定位常見的方式時EMMI(也就是微光拍照)閎康宜碩等廠家都可以提供服務.從照片看亮點位置有亮點說明有大的漏電流.

總結:使用第三方IP時也會遇到相同的問題,都會有輸出高阻態.有必要加上預防措施.風險排除越早,代價越小.認為有風險就要指定排除措施,并落實到flow中.

審核編輯:黃飛

-

芯片

+關注

關注

454文章

50430瀏覽量

421866 -

ldo

+關注

關注

35文章

1918瀏覽量

153176 -

MOS管

+關注

關注

108文章

2396瀏覽量

66603 -

門電路

+關注

關注

7文章

199瀏覽量

40125 -

漏電流

+關注

關注

0文章

261瀏覽量

16996

發布評論請先 登錄

相關推薦

芯片異常漏電幾種情況分析

芯片異常漏電幾種情況分析

評論