鎖存器的工作原理

鎖存器(latch)是一種用于存儲和記憶數字信號的電路。它被廣泛用于計算機和數字電子電路中,用于實現內存存儲、寄存器和其他計算單元。

鎖存器的工作原理是通過反饋電路和放大開關的組合來實現的。在數字電路中,鎖存器通常由邏輯門(例如與門或非門)組成。它可以采用不同的設計方式,包括SR鎖存器、D鎖存器和JK鎖存器等。

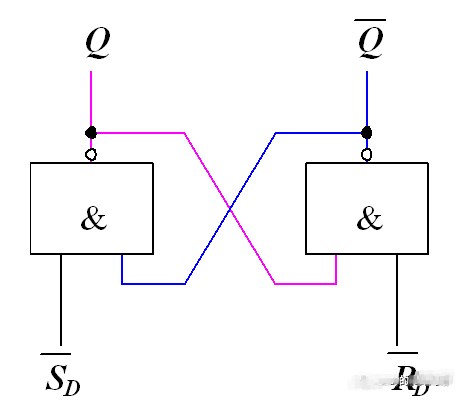

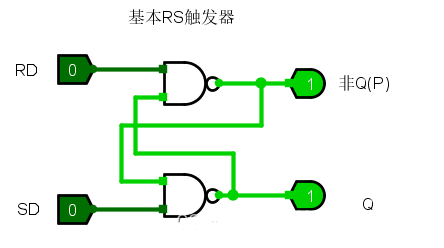

SR鎖存器是最基本的鎖存器類型之一。它由兩個反饋連接的門電路組成,輸入信號被存儲在其中。SR鎖存器有兩個輸入端(通常標記為S和R)和兩個輸出端(通常標記為Q和Q')。當S和R輸入分別激活時,鎖存器會將數據存儲在輸出端上。

具體來說,當S輸入為高電平(1)時,Q輸出為高電平,當R輸入為高電平(1)時,Q輸出為低電平(0)。當S和R都為低電平(0)時,鎖存器保持之前的狀態不變。當S和R同時為高電平(1)時,鎖存器會處于未定義狀態。

D鎖存器是SR鎖存器的一種變體,它只有一個輸入端(通常標記為D)。D鎖存器是通過使用一個與門和一個非門組合實現的。當D輸入為高電平(1)時,鎖存器將數據存儲在輸出端上。

JK鎖存器是SR鎖存器的另一種變體,它具有更靈活的功能。JK鎖存器由兩個輸入端(通常標記為J和K)和兩個輸出端(通常標記為Q和Q')組成。當J和K輸入同時為高電平(1)時,鎖存器將翻轉輸出端的狀態。當J輸入為高電平(1)而K輸入為低電平(0)時,鎖存器將Q輸出設置為高電平(1)。當J輸入為低電平(0)而K輸入為高電平(1)時,鎖存器將Q輸出設置為低電平(0)。當J和K都為低電平(0)時,鎖存器保持之前的狀態。

鎖存器的輸出取決于其當前狀態和輸入信號,并且可以通過適當的輸入信號來改變其狀態。這種能力使得鎖存器成為實現存儲和記憶功能的關鍵電路元件。在計算機和其他數字電子電路中,鎖存器通常用于存儲和操作數據,以實現不同的計算和控制任務。

鎖存器的工作原理可以通過邏輯門的真值表和邏輯公式來推導。例如,對于一個SR鎖存器來說,其真值表可以如下所示:

S | R | Q(t) | Q(t+1)

--+---+------+---------

0 | 0 | 0 | 0

0 | 0 | 1 | 1

1 | 0 | 0 | 0

0 | 1 | 0 | 1

1 | 1 | 0 | 0

其中,t表示當前時刻,t+1表示下一個時刻,Q(t)表示當前存儲的數據,Q(t+1)表示下一個時刻存儲的數據。從真值表中可以看出,鎖存器的輸出取決于當前時刻的輸入和上一個時刻的輸出。

鎖存器的工作原理還可以通過邏輯門電路進行仿真和實現。例如,可以使用邏輯門(與門、非門等)來實現SR鎖存器、D鎖存器和JK鎖存器。通過適當的選擇和組合邏輯門,可以構建不同類型的鎖存器電路。

總結來說,鎖存器是一種用于存儲和記憶數字信號的電路,它通過反饋電路和放大開關的組合來實現。不同類型的鎖存器具有不同的功能和特性,例如SR鎖存器、D鎖存器和JK鎖存器等。鎖存器的工作原理可以通過邏輯門的真值表和邏輯公式進行推導和理解。鎖存器在計算機和其他數字電子電路中被廣泛應用,用于實現內存存儲、寄存器和其他計算單元。

-

邏輯門

+關注

關注

1文章

141瀏覽量

24025 -

鎖存器

+關注

關注

8文章

904瀏覽量

41444

發布評論請先 登錄

相關推薦

RS鎖存器的置位端口是哪個

Rs鎖存器的工作原理、優缺點及應用

sr鎖存器為啥q和q非不是反向

rs鎖存器和sr鎖存器有什么區別嗎

RS鎖存器的工作原理和應用實例

鎖存器的工作原理

鎖存器的工作原理

評論