在以往的項(xiàng)目中,要控制FPGA內(nèi)部某個信號的值,往往是通過配置寄存器來實(shí)現(xiàn)的。其實(shí)Xilinx還提供了一個叫VIO的core,可以動態(tài)改變FPGA內(nèi)部某個信號的值,但是一直沒有用過,一來對于以前的項(xiàng)目來說,沒有應(yīng)用場景,通過寄存器就可以配置了;二來感覺這個東西不是很“實(shí)用”。

背景

在項(xiàng)目中,本來是通過PCIe來配置寄存器的,但是由于某些原因PCIe接口一直有問題,無法配置。FPGA內(nèi)實(shí)現(xiàn)了一個功能,可以根據(jù)寄存器的值來執(zhí)行不同的操作,這個時候就發(fā)現(xiàn)無法上板測試,因?yàn)闆]有辦法配置寄存器。這個時候突然想到了VIO這個core。

VIO介紹

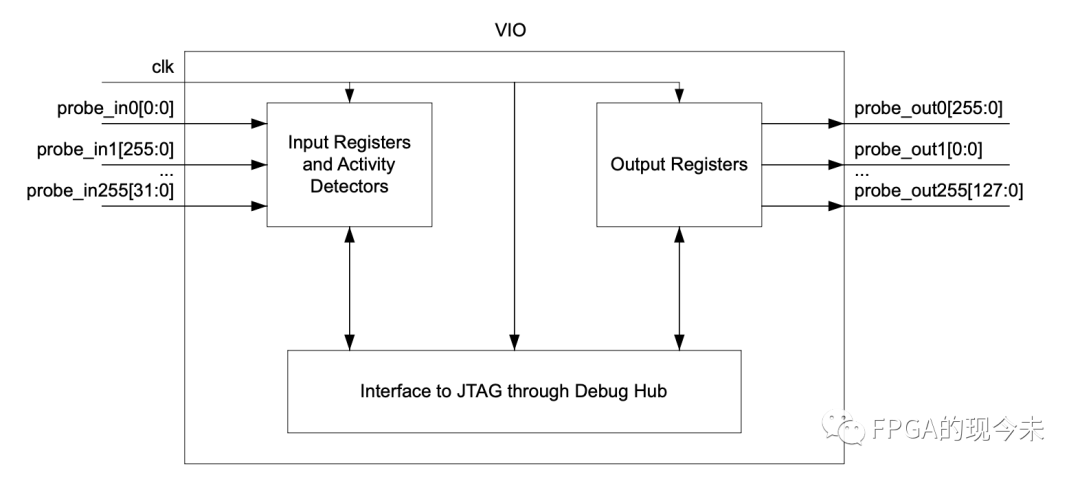

VIO 這個core其實(shí)非常的簡單,沒有什么太多需要介紹的,可以參考 PG159 ,這里做一個簡單的說明。框圖如下圖所示:

該模塊就是定義了一些輸入和輸出,其中可以定義的輸入和輸出信號的個數(shù)最多為256個,每個信號的位寬最大為256bit。在例化的時候只需要確定需要監(jiān)控的信號個數(shù),以及每個信號的位寬;或者需要控制的信號個數(shù)和每個信號的位寬即可。

場景應(yīng)用

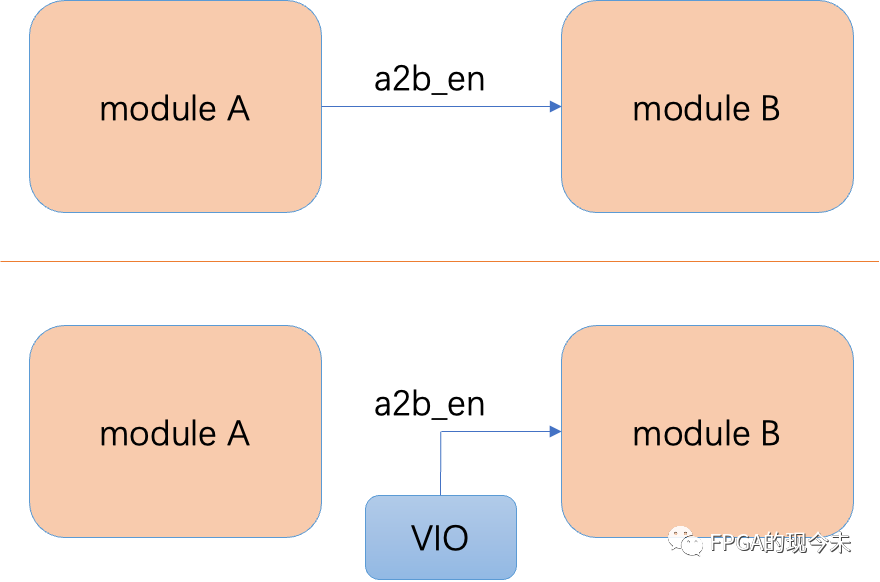

比如我們有如下一個場景,A模塊輸出一個控制信號a2b_en給B模塊,從而控制B模塊的工作方式。但是A模塊目前還不能產(chǎn)生該信號,筆者的項(xiàng)目中,A模塊就是PCIe模塊,由于沒有調(diào)通,還無法通過配置來控制a2b_en信號。

這個時候,我們例化了一個VIO模塊,只用它的輸出,并將這個輸出連接到B模塊的輸入信號a2b_en上即可。

在加載后,vivado會彈出調(diào)試窗口,通過該窗口,我們可以看到控制信號a2b_en,這個時候就可以設(shè)置它的值為0還是為1.

當(dāng)然上述例子中我們只是用了它的output,其input的使用就和ila有點(diǎn)類似了。

總結(jié)

當(dāng)我們需要動態(tài)的修改FPGA內(nèi)某些寄存器的值時,除了通過軟件寄存器配置的方式,還可以通過例化VIO的方式來實(shí)現(xiàn)修改。另外VIO和ila一樣也可以監(jiān)控內(nèi)部信號的值,當(dāng)我們只是簡單的觀測下某個信號時,可以采用VIO,因?yàn)橄啾萯la,它不需要緩存,當(dāng)然對于復(fù)雜的問題分析,ila還是更勝一籌。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601807 -

寄存器

+關(guān)注

關(guān)注

31文章

5317瀏覽量

120002 -

Xilinx

+關(guān)注

關(guān)注

71文章

2163瀏覽量

121004 -

PCIe

+關(guān)注

關(guān)注

15文章

1217瀏覽量

82436 -

VIO

+關(guān)注

關(guān)注

0文章

11瀏覽量

10125

發(fā)布評論請先 登錄

相關(guān)推薦

XILINX FPGA Debug with VIO and TCL

MOS管的應(yīng)用場景

this的使用場景及與C,Java中的this的區(qū)別

FPGA的應(yīng)用場景

幾種LED調(diào)光協(xié)議分析及具體應(yīng)用場景介紹

Firefly集群服務(wù)器的應(yīng)用場景資料介紹

SMT組裝工藝流程的應(yīng)用場景

labview 和 wincc 的區(qū)別 使用場景

Vivado之VIO原理及應(yīng)用

Xilinx VIO介紹和應(yīng)用場景

Xilinx VIO介紹和應(yīng)用場景

評論