在本系列第二篇文章中,我們主要了解到半導體封裝的作用。這些封裝的形狀和尺寸各異,保護和連接脆弱集成電路的方法也各不相同。在這篇文章中,我們將帶您了解半導體封裝的不同分類,包括制造半導體封裝所用材料的類型、半導體封裝的獨特制造工藝,以及半導體封裝的應用案例。

半導體封裝的分類

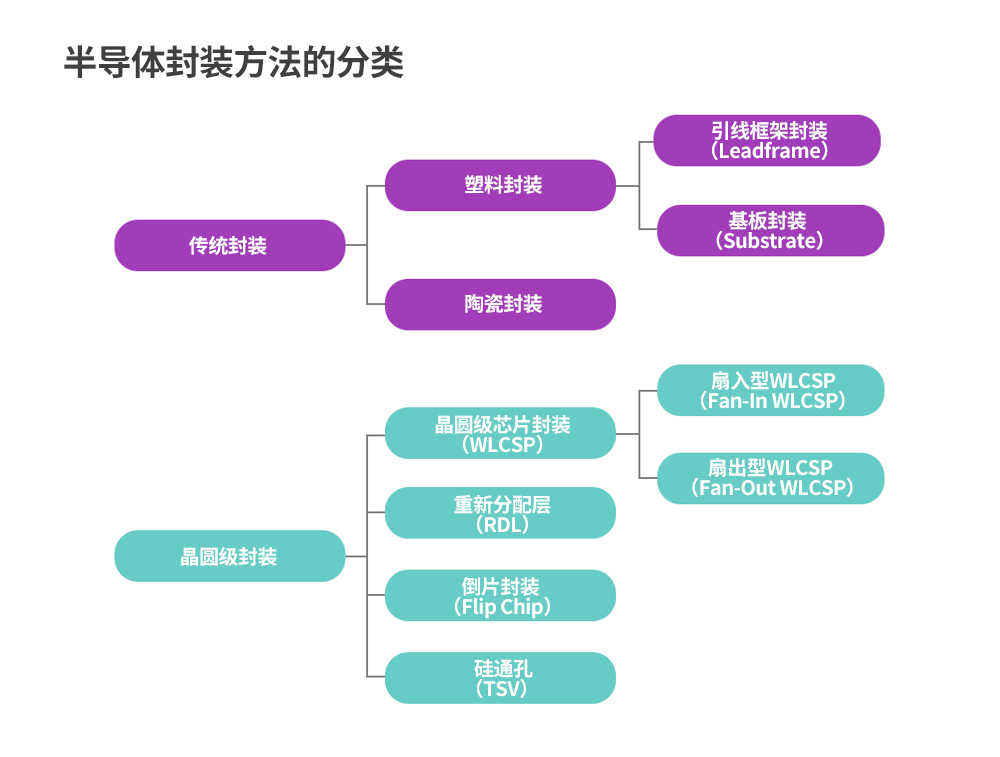

圖1為您呈現了半導體封裝方法的不同分類,大致可以分為兩種:傳統封裝和晶圓級(Wafer-Level)封裝。傳統封裝首先將晶圓切割成芯片,然后對芯片進行封裝;而晶圓級封裝則是先在晶圓上進行部分或全部封裝,之后再將其切割成單件。

▲圖1:半導體封裝方法的分類(? HANOL出版社)

根據封裝材料的不同,傳統封裝方法可進一步細分為陶瓷封裝和塑料封裝。根據封裝媒介的不同,塑料封裝又可進一步分為引線框架封裝(Leadframe)或基板封裝(Substrate)。

晶圓級封裝方法可進一步細分為四種不同類型:1)晶圓級芯片封裝(WLCSP),可直接在晶圓頂部形成導線和錫球(Solder Balls),無需基板;2)重新分配層(RDL),使用晶圓級工藝重新排列芯片上的焊盤位置1,焊盤與外部采取電氣連接方式;3)倒片(Flip Chip)封裝,在晶圓上形成焊接凸點2進而完成封裝工藝;4)硅通孔(TSV)封裝,通過硅通孔技術,在堆疊芯片內部實現內部連接。

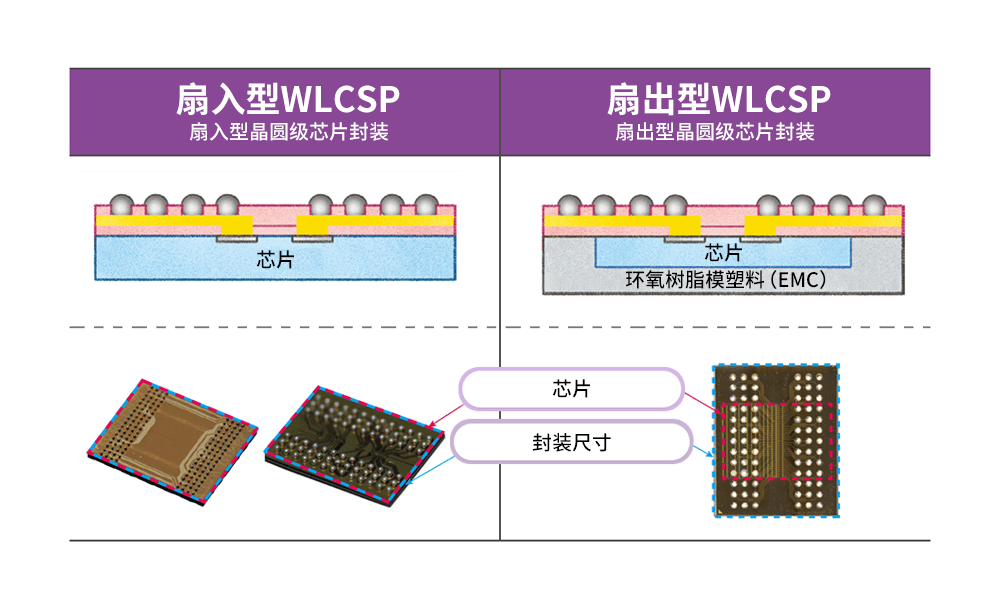

晶圓級芯片封裝分為扇入型WLCSP和扇出型WLCSP。扇入型WLCSP工藝將導線和錫球固定在晶圓頂部,而扇出型WLCSP則將芯片重新排列為模塑3晶圓。這樣做是為了通過晶圓級工藝形成布線層,并將錫球固定在比芯片尺寸更大的封裝上。

1焊盤 (Pad):一種以電氣方式連接至其他媒介的通道。在芯片上,焊盤通過導線或倒片凸點與外部實現電氣連接;在基板上,焊盤用于芯片之間的連接。

2焊接凸點 (Solder bump):一種通過倒片鍵合將芯片連接到基板的導電凸點。它還可以將球柵陣列(BGA)或芯片尺寸封裝(CSP)連接至電路板。

3模塑 (Molding):使用環氧樹脂模塑料(EMC)密封引線鍵合結構或倒裝芯片鍵合結構半導體產品的過程。

01傳統( Conventional )封裝

塑料封裝:引線框架

▲圖2:引線框架封裝方法的分類(? HANOL出版社)

在塑料封裝方法中,芯片被環氧樹脂模塑料(EMC)4等塑料材料覆蓋。引線框架封裝是一種塑料封裝方法,采用一種被稱為引線框架的金屬引線作為基板。引線框架采用刻蝕工藝在薄金屬板上形成布線。

4環氧樹脂模塑料(EMC):一種熱固性塑料,具有優異的機械、電絕緣和耐溫特性。環氧樹脂模塑料是一種分子量相對較低的樹脂,能夠在固化劑或催化劑的作用下進行三維固化。

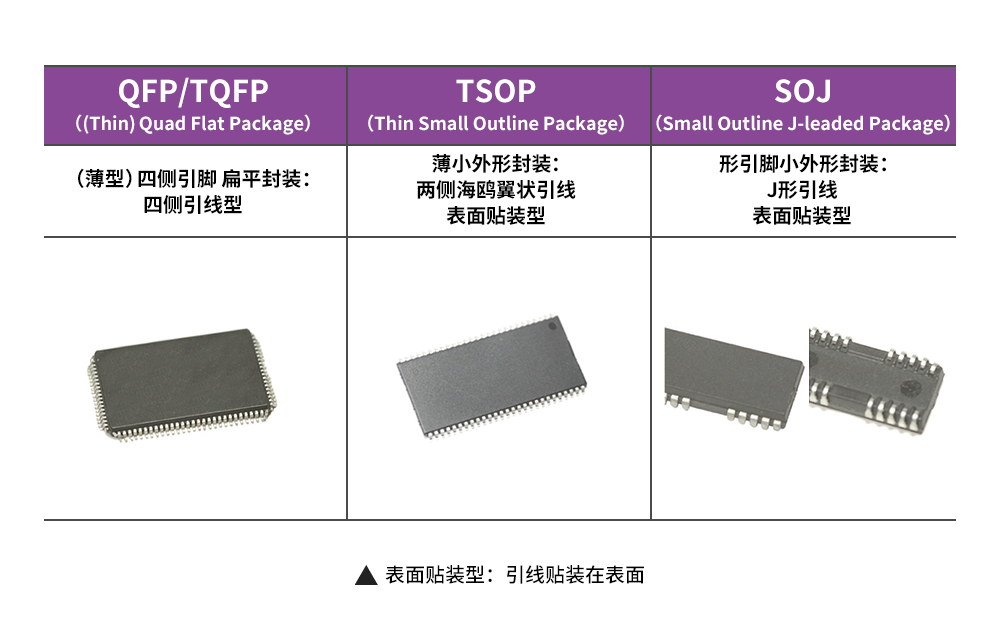

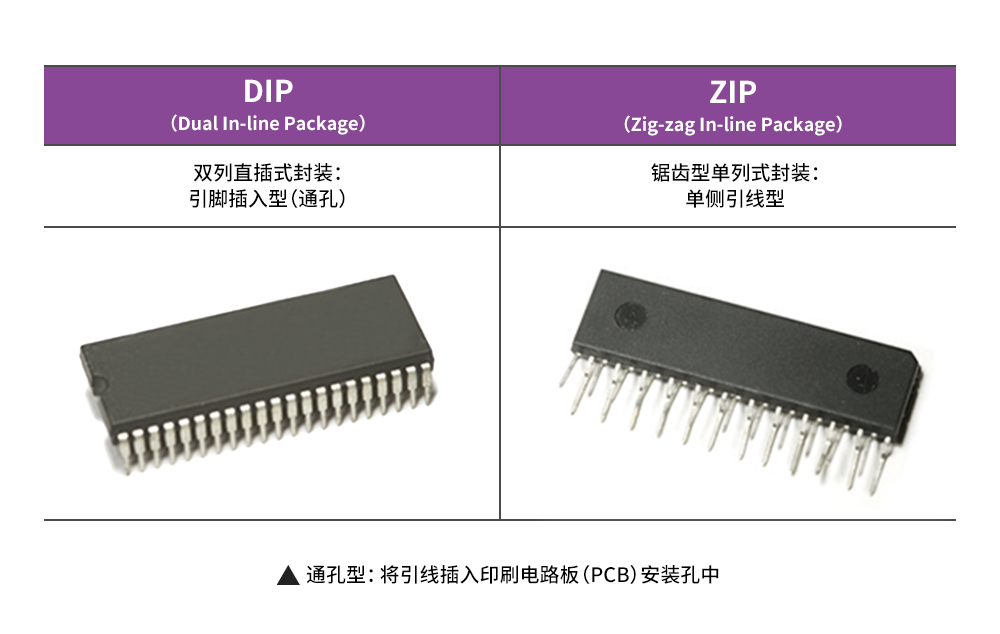

圖2呈現了引線框架封裝方法的各種分類。20世紀70年代,人們通常采用雙列直插式封裝(DIP)或鋸齒型單列式封裝(ZIP)等通孔型技術,即,將引線插入到印刷電路板(PCB)的安裝孔中。后來,隨著引腳(Pin)數量的不斷增加,以及PCB設計的日趨復雜,引線插孔技術的局限性也日益凸顯。在此背景下,薄型小尺寸封裝(TSOP)、四方扁平封裝(QFP)和J形引線小外形封裝(SOJ)等表面貼裝型技術陸續問世。對于需要大量輸入/輸出(I/O)引腳(如邏輯芯片)的產品而言,可采用四方扁平封裝(QFP)等封裝技術,將引線固定在四個邊上。為了滿足系統環境對薄型化封裝的需求,薄型四方扁平封裝(TQFP)和薄型小尺寸封裝也應運而生。

隨著半導體產品向更高速度邁進,支持多層布線的基板封裝方法成為主流封裝技術。但是,TSOP封裝等引線框架封裝方法因其制造成本較低,仍然得到廣泛使用。引線框架通過在金屬板上沖壓或刻蝕布線形狀制成,而基板的制造工藝則相對復雜,因此,引線框架的制造成本比基板的制造成本更低。綜上,在生產不追求高速電氣特性的半導體產品時,引線框架封裝方法仍然是一種理想選擇。

塑料封裝:基板封裝

顧名思義,基板封裝方法使用基板作為媒介。由于基板使用多層薄膜制成,因而基板封裝有時也被稱為壓層式封裝。不同于引線框架封裝只有一個金屬布線層(因為引線框架這種金屬板無法形成兩個以上金屬層),基板封裝可以形成若干布線層,因此電氣特性更加優越且封裝尺寸更小。引線框架封裝和基板封裝的另一個主要區別是布線連接工藝。連接芯片和系統的布線必須分別在引線框架和基板上實現。當需要交叉布線時,基板封裝可將導線交叉部署至另一個金屬層;引線框架封裝由于只有一個金屬層,因而無法進行交叉布線。

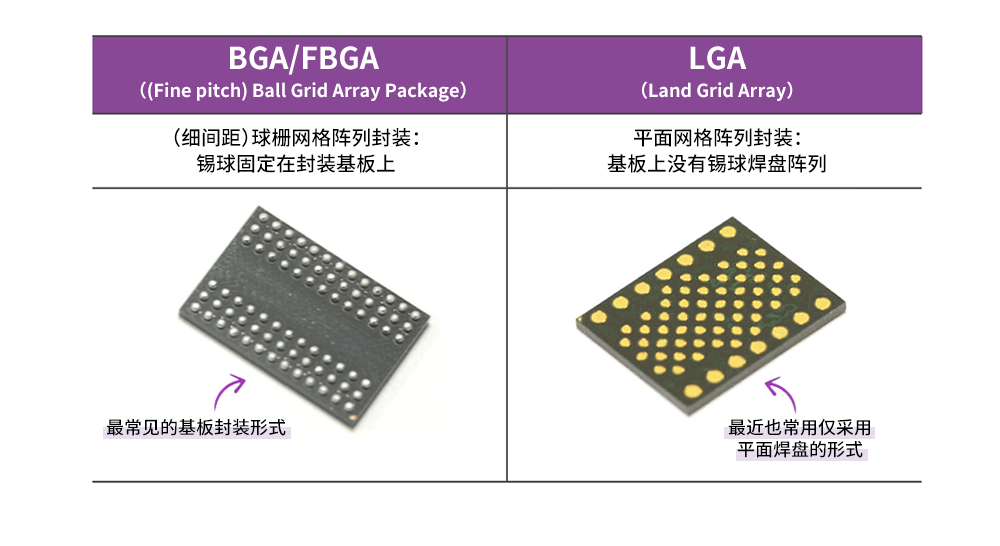

如圖3所示,基板封裝可以將錫球全部排列在一個面作為引腳,由此獲得大量引腳。相比之下,引線框架封裝采用引線作為引腳,而引線只能在一側的邊緣形成。這樣的部署也改善了基板封裝的電氣特性。在封裝尺寸方面,引線框架封裝由主框架和側面引線所占空間構成,因而尺寸通常較大。而基板封裝的引腳位于封裝底部,可有效節省空間,因而尺寸通常較小。

▲圖3:球柵陣列(BGA)和平面網格陣列(LGA)封裝對比(? HANOL出版社)

鑒于上述優勢,如今大多數半導體封裝都采用基板封裝。最常見的基板封裝類型是球柵網格陣列(BGA)封裝。但近年來,平面網格陣列(LGA)封裝日益盛行,這種封裝方法采用由扁平觸點構成的網格平面結構替代錫球。

陶瓷封裝

陶瓷封裝采用陶瓷體,具有良好的散熱性和可靠性。然而,由于陶瓷制造工藝成本高昂,導致這種封裝類型的總制造成本也相對較高。因此,陶瓷封裝主要用于對可靠性有著極高要求的邏輯半導體,以及用于驗證CMOS圖像傳感器(CIS)的封裝。

02晶圓級封裝

扇入型 (Fan-In)

WLCSP

(Wafer Level Chip Scale Package)

晶圓級芯片封裝的大多數制造過程都是在晶圓上完成的,是晶圓級封裝的典型代表。然而,從廣義上講,晶圓級封裝還包括在晶圓上完成部分工藝的封裝,例如,使用重新分配層、倒片技術和硅通孔技術的封裝。在扇入型WLCSP和扇出型WLCSP中,“扇”是指芯片尺寸。扇入型WLCSP的封裝布線、絕緣層和錫球直接位于晶圓頂部。與傳統封裝方法相比,扇入型WLCSP既有優點,也有缺點。

在扇入型WLCSP中,封裝尺寸與芯片尺寸相同,都可以將尺寸縮至最小。此外,扇入型WLCSP的錫球直接固定在芯片上,無需基板等媒介,電氣傳輸路徑相對較短,因而電氣特性得到改善。而且,扇入型WLCSP無需基板和導線等封裝材料,工藝成本較低。這種封裝工藝在晶圓上一次性完成,因而在裸片(Net Die,晶圓上的芯片)數量多且生產效率高的情況下,可進一步節約成本。

扇入型WLCSP的缺點在于,因其采用硅(Si)芯片作為封裝外殼,物理和化學防護性能較弱。正是由于這個原因,這些封裝的熱膨脹系數與其待固定的PCB基板的熱膨脹系數5存在很大差異。受此影響,連接封裝與PCB基板的錫球會承受更大的應力,進而削弱焊點可靠性6。

5熱膨脹系數 (Coefficient of thermal expansion):在壓力恒定的情況下,物體的體積隨著溫度升高而增大的比率。膨脹或收縮的程度與溫度的升高或降低呈線性關系。

6焊點可靠性 (Solder joint reliability):通過焊接方式將封裝與PCB連接時,確保焊點的質量足以在封裝生命周期內完成預期的機械和電氣連接目的。

存儲器半導體采用新技術推出同一容量的芯片時,芯片尺寸會產生變化,扇入型WLCSP的另一個缺點就無法使用現有基礎設施進行封裝測試。此外,如果封裝錫球的陳列尺寸大于芯片尺寸,封裝將無法滿足錫球的布局要求,也就無法進行封裝。而且,如果晶圓上的芯片數量較少且生產良率較低,則扇入型WLCSP的封裝成本要高于傳統封裝。

扇出型WLCSP

扇出型WLCSP既保留了扇入型WLCSP的優點,又克服了其缺點。圖4顯示了扇入型WLCSP和扇出型WLCSP的對比。

▲圖4:扇入型WLCSP和扇出型WLCSP的對比(? HANOL出版社)

扇入型WLCSP的所有封裝錫球都位于芯片表面,而扇出型WLCSP的封裝錫球可以延伸至芯片以外。在扇入型WLCSP中,晶圓切割要等到封裝工序完成后進行。因此,芯片尺寸必須與封裝尺寸相同,且錫球必須位于芯片尺寸范圍內。在扇出型WLCSP中,芯片先切割再封裝,切割好的芯片排列在載體上,重塑成晶圓。在此過程中,芯片與芯片之間的空間將被填充環氧樹脂模塑料,以形成晶圓。然后,這些晶圓將從載體中取出,進行晶圓級處理,并被切割成扇出型WLCSP單元。

除了具備扇入型WLCSP的良好電氣特性外,扇出型WLCSP還克服了扇入型WLCSP的一些缺點。這其中包括:無法使用現有基礎設施進行封裝測試;封裝錫球陳列尺寸大于芯片尺寸導致無法進行封裝;以及因封裝不良芯片導致加工成本增加等問題。得益于上述優勢,扇出型WLCSP在近年來的應用范圍越來越廣泛。

重新分配層

(ReDistribution Layer, RDL)

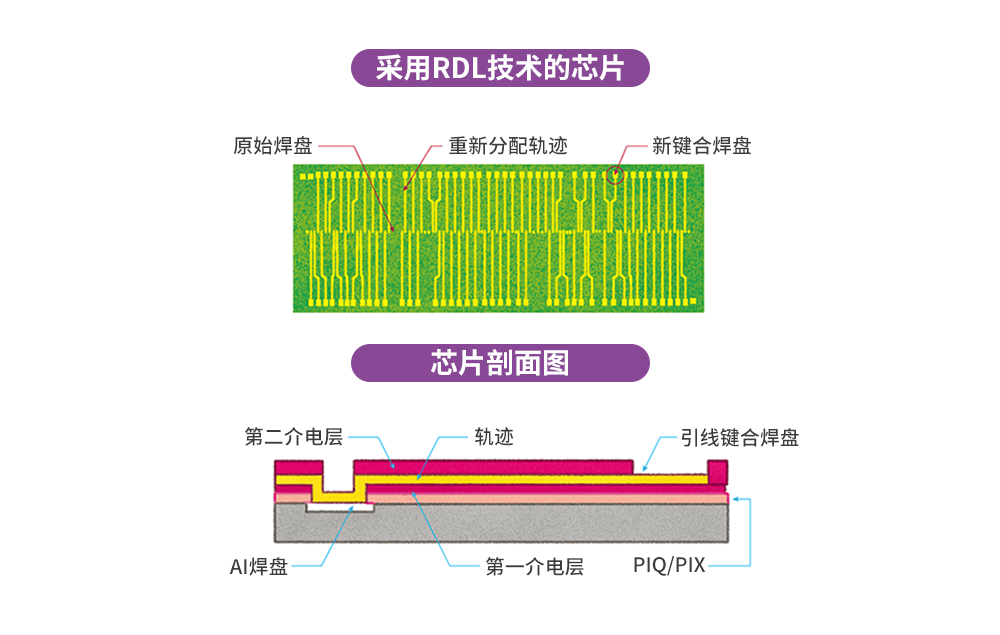

RDL技術指重新布線的行為。RDL技術旨在通過添加額外的金屬層,對晶圓上已經形成的鍵合焊盤進行重新排列。圖5顯示了使用RDL技術將焊盤重新分配到邊緣的中心焊盤芯片示意圖和剖面圖。RDL技術是一種晶圓級工藝,僅用于重新配置焊盤,經過RDL技術處理的晶圓需采用傳統封裝工藝完成封裝。

▲圖5:采用RDL技術的芯片與剖面圖(? HANOL出版社)

如果客戶想要以獨特的方式排列晶圓上的焊盤,那么,相較于引入新的晶圓制造工藝,在封裝過程中采用RDL技術重新排列現有晶圓上的焊盤更加高效。此外,RDL技術也可以用于中心焊盤芯片的芯片堆疊。

倒片封裝

(Flip Chip)

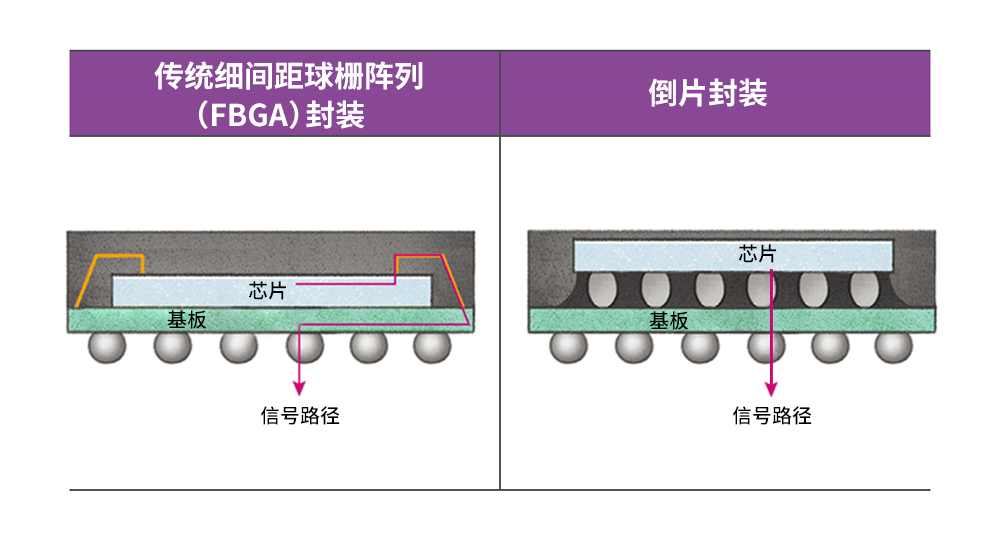

倒片封裝技術因其將芯片上的凸點翻轉并安裝于基板等封裝體上而得名。與傳統引線鍵合一樣,倒片封裝技術是一種實現芯片與板(如基板)電氣連接的互連技術。

然而,倒片封裝技術憑借其優越的電氣性能,已經在很大程度上取代了引線鍵合。這其中有兩方面的原因:一是引線鍵合對于可進行電氣連接的輸入/輸出(I/O)引腳的數量和位置有限制,而倒片封裝不存在這方面的限制;二是倒片封裝的電信號傳輸路徑短于引線鍵合。

在引線鍵合方法中,金屬焊盤在芯片表面采用一維方式排列,因此無法出現在芯片邊緣或中心位置。而倒片鍵合方法在鍵合至基板或形成焊接凸點的過程中不存在任何工藝方面的限制。因此,在倒片封裝方法中,金屬焊盤可以采用二維方式全部排列在芯片的一個側面,將金屬焊盤的數量增加了2的次方。此外,用于形成凸點的焊盤可以布置在芯片頂部的任何位置。同時,用于供電的焊盤可以布置在靠近需要供電的區域,以進一步提升電氣性能。如圖6所示,在將信息從芯片導出至同一封裝球時,倒片鍵合的信號路徑要比引線鍵合短得多,電氣性能也由此得到進一步改善。

▲圖6:引線鍵合與倒片鍵合的信號傳輸路徑對比(? HANOL出版社)

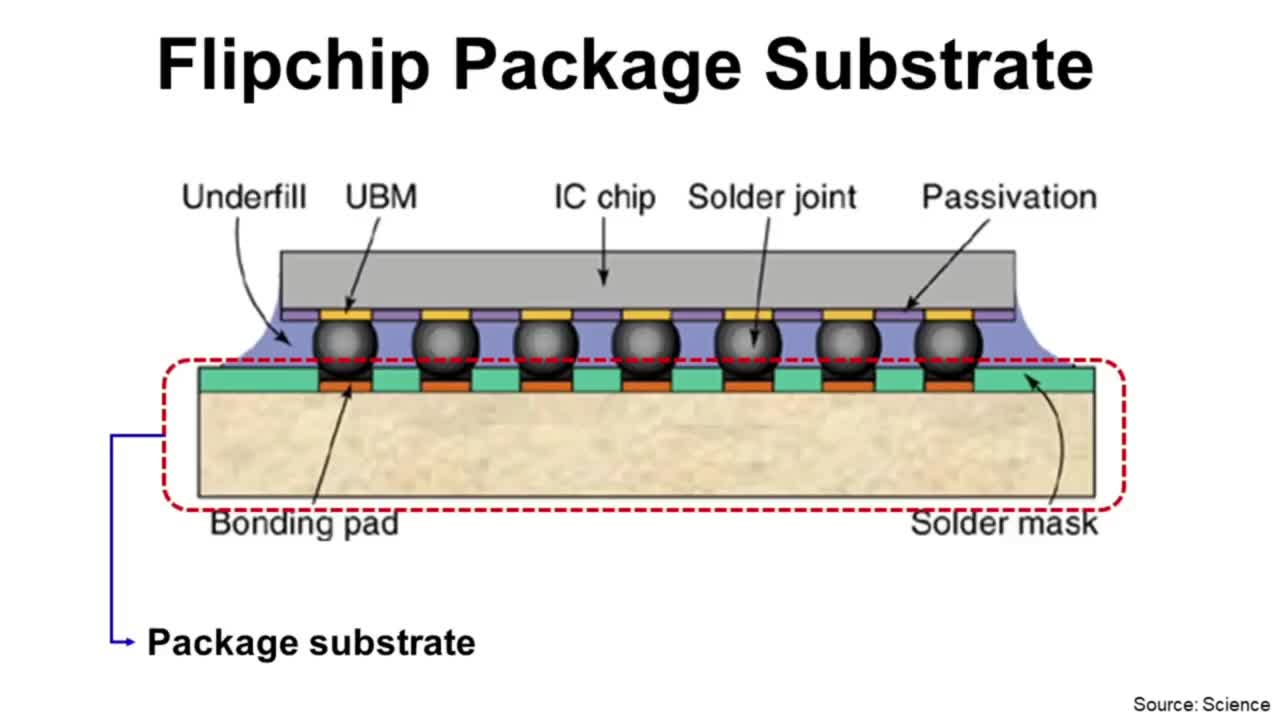

如前所述,WLCSP和倒片封裝均可以在晶圓頂部形成錫球。盡管兩種技術都可以直接安裝在PCB板上,但兩者之間在錫球大小方面卻存在根本區別。

WLCSP封裝中的錫球直徑通常為幾百微米(μm),而倒片封裝技術形成的錫球直徑僅為幾十微米(μm)。由于尺寸較小,我們通常將倒片封裝技術形成的錫球稱為“焊接凸點”,而僅僅依靠這些凸點很難保障焊點可靠性。WLCSP封裝技術形成的錫球能夠處理基板和芯片之間熱膨脹系數差異所產生的應力,但倒片封裝技術形成的焊接凸點卻無法做到這一點。因此,為了確保焊點可靠性,必須使用聚合物型底部填充材料填充倒片凸點之間的空間。底部填充材料可以分散凸點所承擔的應力,由此確保焊點可靠性。

除了本篇所述的封裝技術之外,還有許多不同的半導體封裝類型。在下一篇文章中,我們將重點介紹堆疊封裝和系統級封裝,同時還將介紹引線鍵合和硅通孔等子類別。

審核編輯:湯梓紅

-

芯片

+關注

關注

450文章

49636瀏覽量

417144 -

制造工藝

+關注

關注

2文章

168瀏覽量

19649 -

半導體封裝

+關注

關注

4文章

236瀏覽量

13623 -

焊盤

+關注

關注

6文章

535瀏覽量

37929 -

晶圓級封裝

+關注

關注

5文章

33瀏覽量

11496

原文標題:半導體后端工藝|第三篇:了解不同類型的半導體封裝

文章出處:【微信號:SKhynixchina,微信公眾號:SK海力士】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體封裝的分類和應用案例

半導體封裝的分類和應用案例

評論