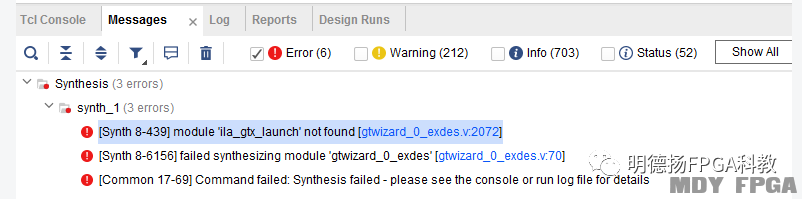

【關(guān)鍵問題!!!!重要!!!】VIVADO會(huì)在MESSAGE窗口出提示很多錯(cuò)誤和警告信息!

但建議大家不要看此信息,原因如下:

這些信息有可能是過(guò)時(shí)的,可能是之前報(bào)錯(cuò)了,因此修正了,這些信息沒有更新。

有些信息是錯(cuò)誤的,但不影響整個(gè)工程的運(yùn)行,例如某個(gè)IP核出錯(cuò),但實(shí)際工程沒使用此IP核。

這些信息沒有順序,即哪些錯(cuò)誤是先發(fā)生的不知道,影響定位。

總之不要看MESSAGE欄的內(nèi)容。

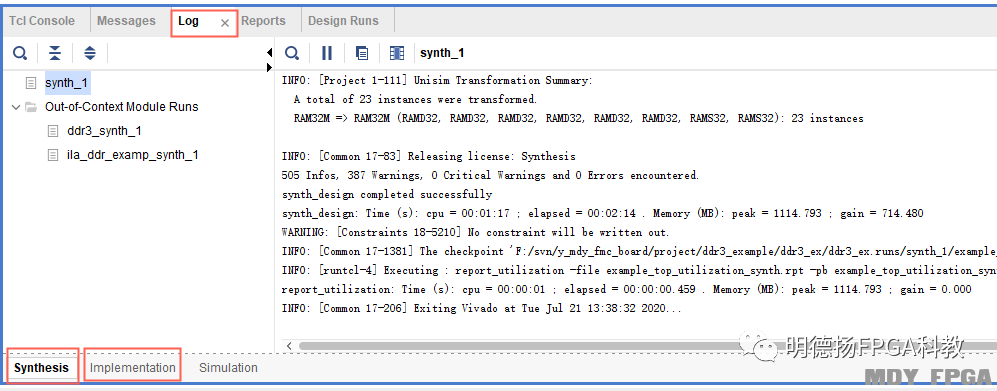

最權(quán)威的信息,應(yīng)該看LOG。如下圖

要看LOG這一欄。 這一欄中,有Synthesis和Implementation這兩部分內(nèi)容。建議整個(gè)工程運(yùn)行后,再看LOG中,第一個(gè)報(bào)錯(cuò)的地方,解決第一個(gè)報(bào)錯(cuò)的問題。

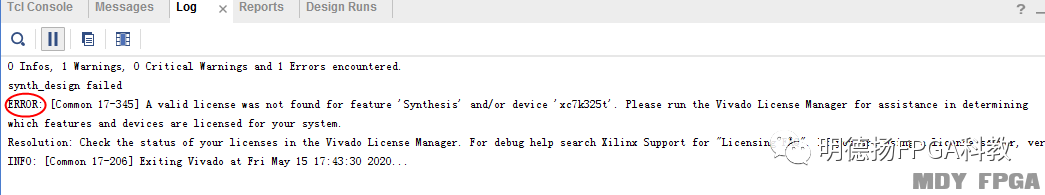

【問題1】使用VIVADO編譯時(shí)出現(xiàn)如下錯(cuò)誤,我使用的是K7芯片。

答:仔細(xì)閱讀提示,該提示是說(shuō)本軟件沒有K7芯片的license。您需要去官方下載一個(gè)K7芯片的LICENSE使用,該LICENSE是免費(fèi)的。

LICENSE的申請(qǐng)方法,請(qǐng)參考:https://blog.csdn.net/wxh0000mm/article/details/84068162

注意,上面鏈接中講的是申請(qǐng)VIVADO LICENSE的方法,本問題是指K7芯片的LICENSE,要選擇時(shí)注意選正確。

【問題2】ILA報(bào)如下錯(cuò)誤,大概意思是有一些信號(hào)沒有連接。

The debug port 'u_ila_0/probe4' has 1 unconnected channels (bits). This will cause errors during implementation

答:1. 該報(bào)錯(cuò)是指ILA里有一些接口沒有連接。您要檢查一下例化時(shí),是否全部的probe都已經(jīng)連接了,尤其需要注意的是:里面的每個(gè)probe位寬都要正確,也就是probe的位寬和信號(hào)位寬要一樣。

2. 在message界面顯示的是之前殘留的信息,需要點(diǎn)一次reset synthesis run,重新RUN一遍,查看最新的提示信息。

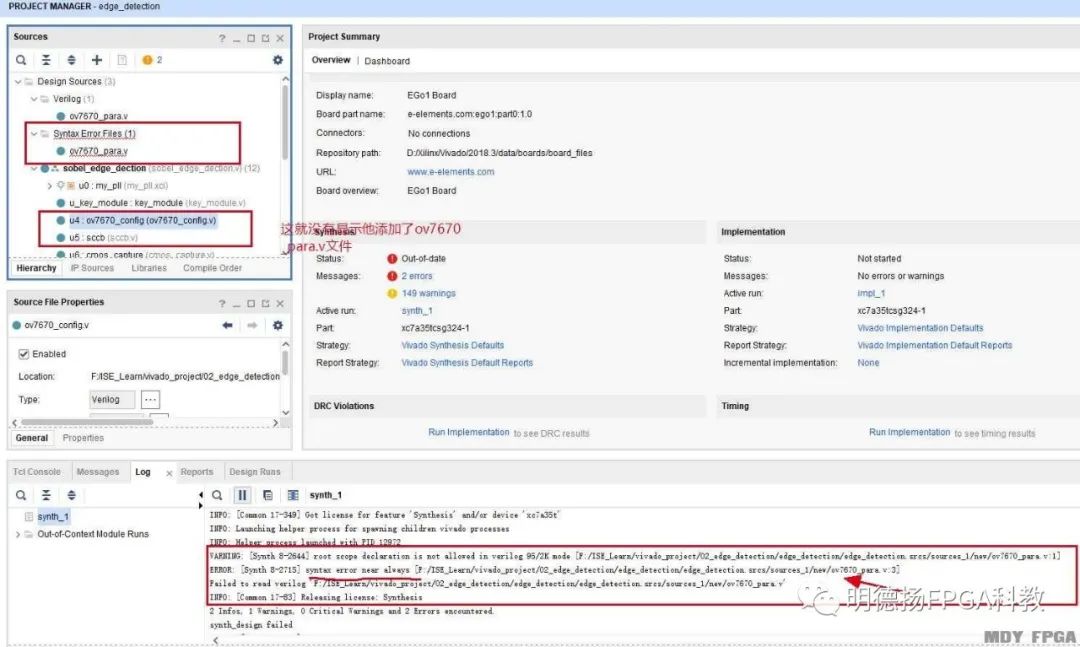

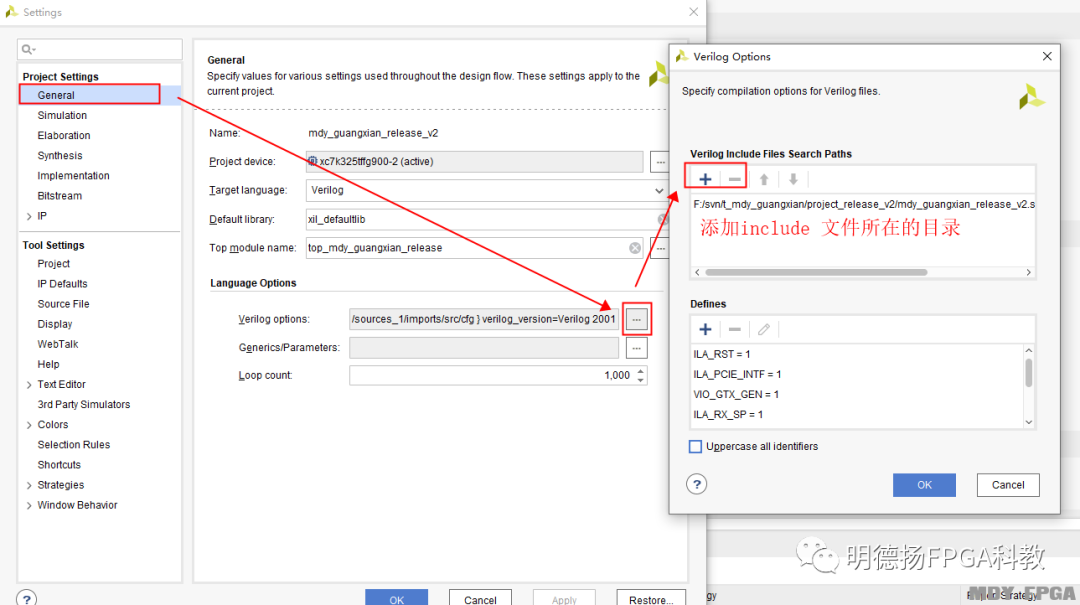

【問題3】VIVAOD添加include文件報(bào)錯(cuò)。

答:

一般include進(jìn)來(lái)的文件,不是一個(gè)完整的module代碼。

該代碼是不能像其他代碼那樣,通過(guò)添加文件的方式加到本工程,這是不正確的。

正確的方式是,在VIVADO的設(shè)置界面(在最左邊的窗口,PROJECT MANAGER,點(diǎn)擊setting),然后按下圖設(shè)置。

如果還報(bào)錯(cuò),注意要把該文件從工程中remove掉。

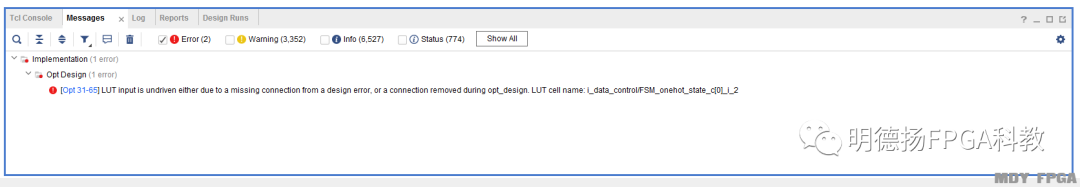

【問題4】不添加ILA,可以順利生成bit流文件。添加ILA后,就在布局布線這里報(bào)錯(cuò),這是什么原因呢?

答:使用ILA的時(shí)候,特別注意ILA的信號(hào)個(gè)數(shù)、信號(hào)位寬要與被測(cè)信號(hào)一致,否則會(huì)存在編譯不通過(guò)的風(fēng)險(xiǎn)

像這種錯(cuò)誤提示,如果看不懂,則看關(guān)鍵詞和提示的信號(hào)。如上圖中的FSM_onehot_state_c[0]信號(hào),從代碼上檢查該信號(hào)是否存在以下問題。

該信號(hào)是不是沒有被驅(qū)動(dòng)(也就是沒被賦值);

該信號(hào)是不是被 優(yōu)化(包括直接或者間接未被使用);

信號(hào)位寬不正確;

該信號(hào)與其他信號(hào)有哪些不同。

再不行,嘗試改改該信號(hào)信號(hào),重新綜合看

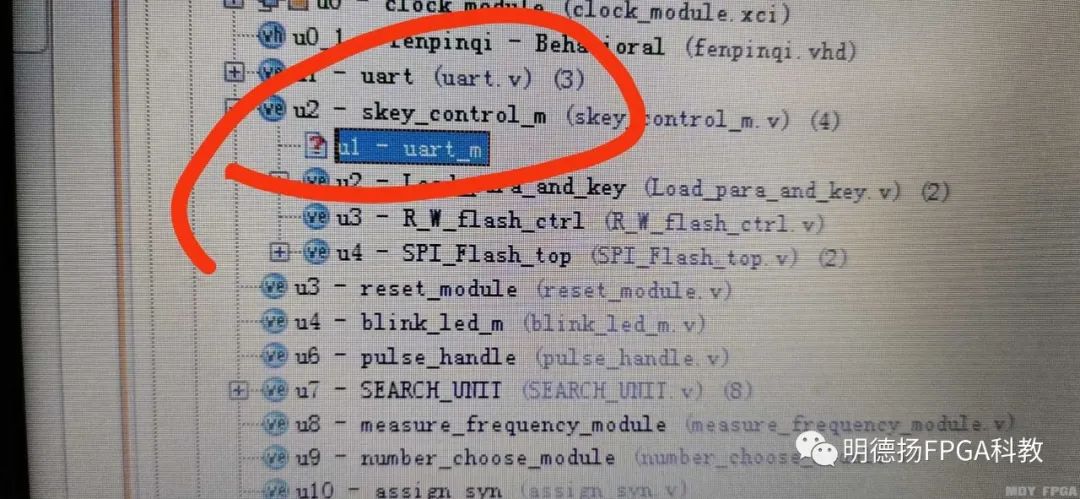

【問題5】以下圖片出現(xiàn)?號(hào)問題是怎么回事?

答:出現(xiàn)問號(hào),是表示該文件沒有添加到文件,請(qǐng)把該代碼添加到工程

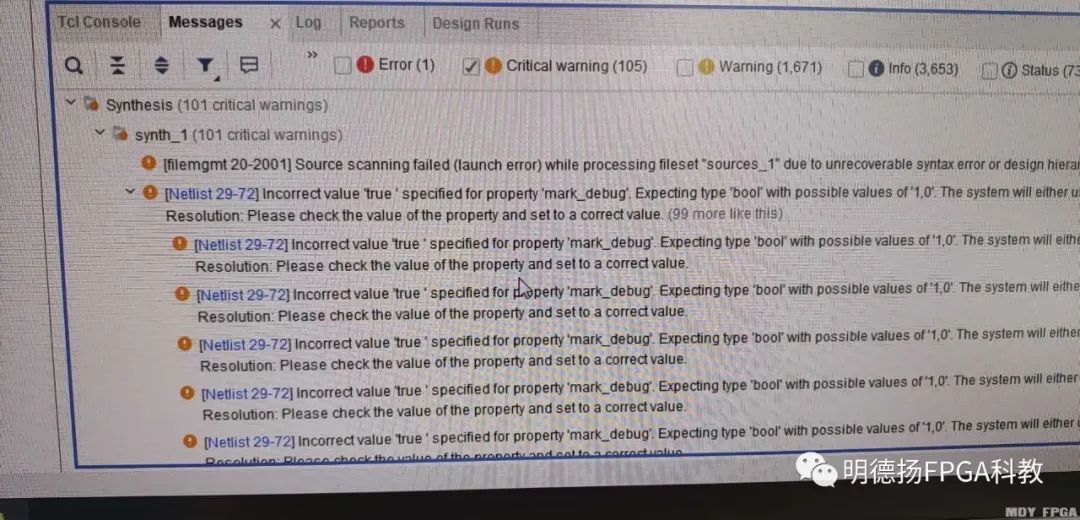

【問題6】 出現(xiàn)以下警告 Synthesis(101 critical warnings),請(qǐng)問如何解決?

答:拉信號(hào)到調(diào)試工具引起的警告,MDY不使用此方法,所以沒遇到過(guò)。建議使用例化ILA的方法,我們已經(jīng)形成了一套規(guī)范方法,有興趣可以看下面鏈接 :

VIVADO使用教程http://www.mdy-edu.com/wentijieda/20210409/1209.html?1617940294

請(qǐng)看 第六集:VIVADO教程06-MDY的ILA使用經(jīng)驗(yàn)

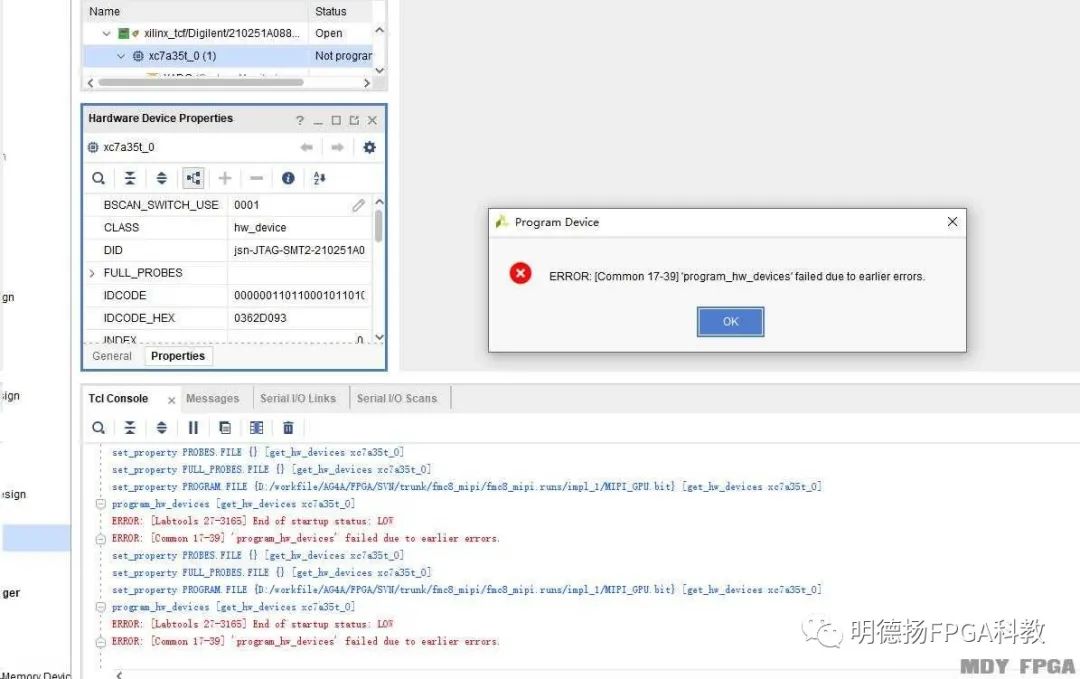

【問題7】 出現(xiàn)器件識(shí)別不到有如下可能原因,如下圖所示,請(qǐng)問是什么原因 ?

答:

1.下載器有問題,可以換一個(gè)下載器看看。

2.硬件電路有問題,需要檢查。

3.電源未開。

4.下載器插反了。

5.FPGA芯片有問題,以上是可能原因。

【問題8】老師,什么情況下不用sdk?

答:只有純邏輯設(shè)計(jì),沒有用到軟核和ARM的時(shí)候,可以不用sdk。

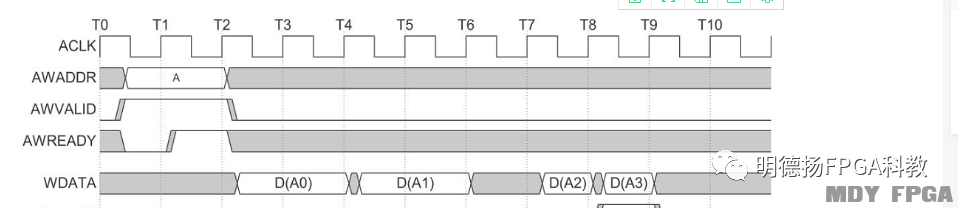

【問題9】下面是AXI總線的時(shí)序圖,但我仿真發(fā)現(xiàn),在AWVALID之前,AWREADY就變高了,這是錯(cuò)誤的嗎?

答:上面時(shí)序沒有說(shuō),在AWVALID之后,AWREADY才為1。上圖只是要說(shuō)明的是:AWVALID和AWREADY同時(shí)為1,才表示一個(gè)有效的數(shù)據(jù)。AWREADY是可以任意時(shí)候?yàn)?的。 這也告訴我們,時(shí)序不要想當(dāng)然地理解。

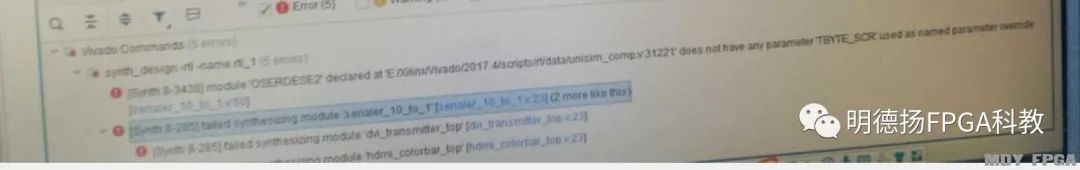

【問題10】Vivado-Synthesis: Verilog parameter overridden within instantiation fails with "ERROR:[Synth 8-3438]"

答:這句提示是說(shuō):在例化的時(shí)候,參數(shù)TBYTE_SCR在設(shè)計(jì)文件里找不到。即原設(shè)計(jì)文件里沒有TBYTE_SCR,但例化的時(shí)候又使用了。

【問題11】布線里route design跑很久,不知是什么回事?

答:1.使用增量編譯的方法,會(huì)節(jié)省一些時(shí)間。具體做法可以百度;

2.換一臺(tái)性能更好的電腦。

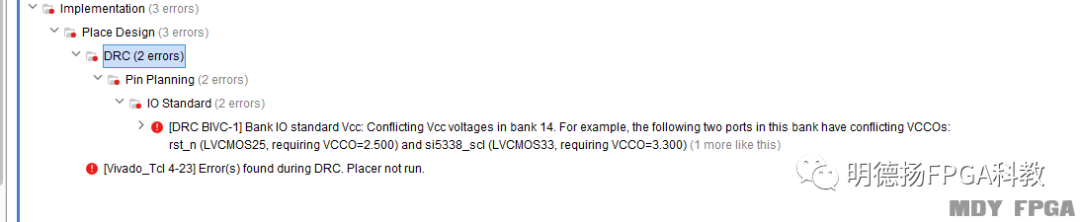

【問題12】在布局布線時(shí),提示DRC錯(cuò)誤,錯(cuò)誤如下圖。

答:看提示,一般抓關(guān)鍵詞。

注意圖中的關(guān)鍵詞:

bank 14,rst_n,LVCMOS25,si5388_scl,LVCMOS33。

在開發(fā)過(guò)程,要和這些詞關(guān)聯(lián)起來(lái)的步驟就是配置管腳,并且這些管腳與BANK14有關(guān)。

所以根據(jù)提示,可以去檢查配置管腳的頁(yè)面。

其實(shí)這里的問題是:

在同一個(gè)BANK的管腳,其電壓標(biāo)準(zhǔn)必須是相同的,例如都使用2.5V標(biāo)準(zhǔn),或者都用3.3V標(biāo)準(zhǔn)。

LVCMOS25是2.5V的,LVCMOS33是3.3V的。

解決方法:

將rst_n配置成LVCMOS33,或者將si5388_scl配置成LVCMOS25

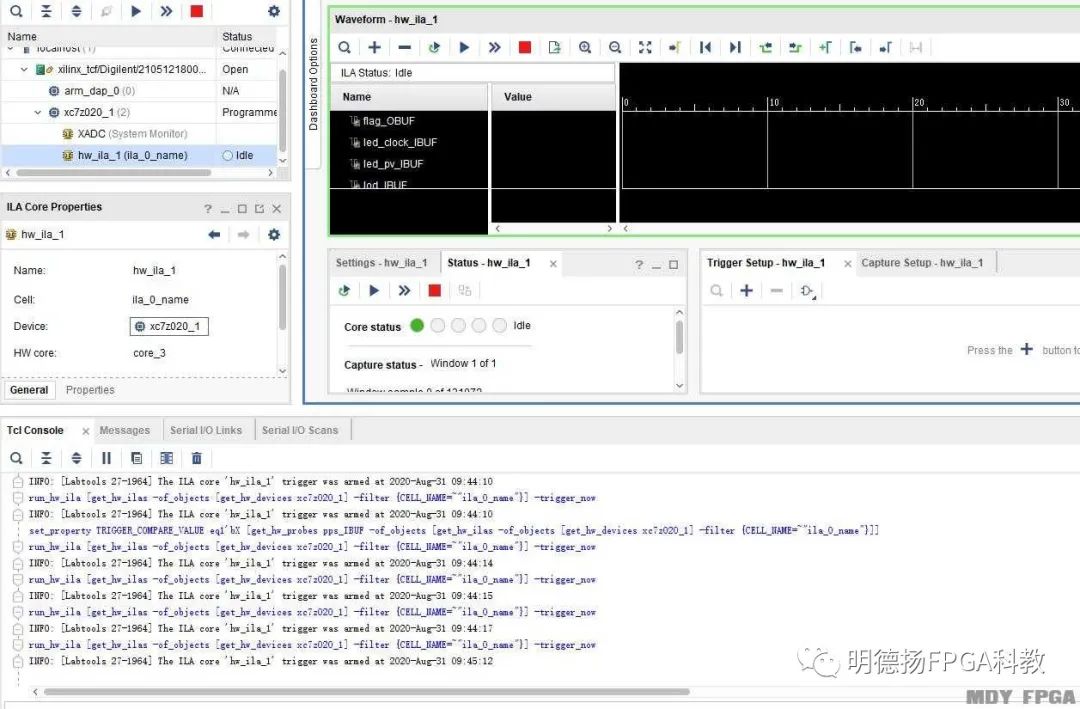

【問題13】老師使用ILA采樣的時(shí)候 說(shuō)明波形也沒有 并且有這個(gè)警告是怎么回事啊-----Vivado INFO [Labtools 27-1964]

答:

1、檢查是否添加了siganls,并且您能夠更早地看到它們,現(xiàn)在它們消失了?

2、可以關(guān)閉hw_ila1窗口,然后重新打開并檢查是否可以看到任何信號(hào)嗎?

如果不是,請(qǐng)單擊“ +”按鈕并手動(dòng)添加信號(hào)。

同時(shí)點(diǎn)擊立即觸發(fā)并重新檢查

【問題14】老師這個(gè)管腳驅(qū)動(dòng)強(qiáng)度是什么意思啊 選擇的時(shí)候應(yīng)該怎么選?

答:

可以使用默認(rèn)值,一直沒改過(guò)

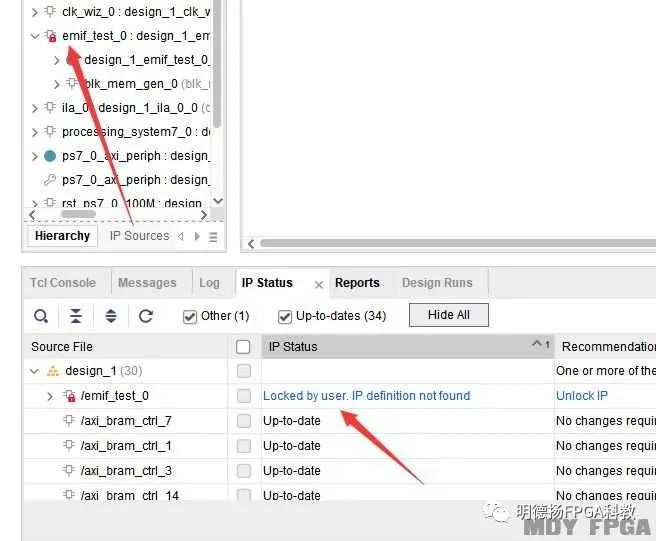

【問題15】我的iP顯示鎖定,更新IP怎么是locked by user

答:

這是設(shè)計(jì)師對(duì)自己寫的代碼鎖定了,其他人無(wú)法修改。所以這個(gè)就是直接使用即可。如果使用有問題,請(qǐng)找原設(shè)計(jì)師。

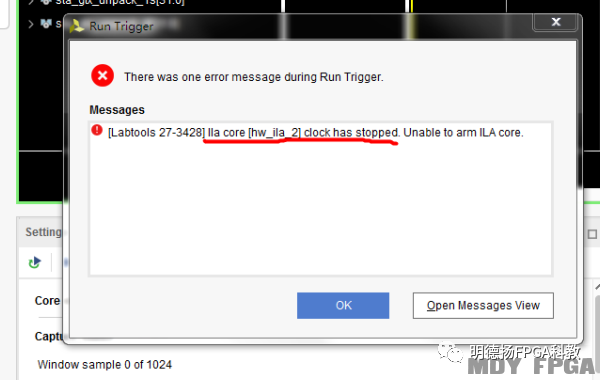

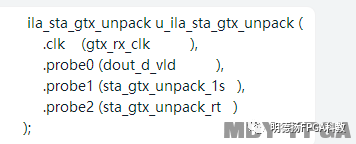

【問題16】使用VIVADO的DEBUG工具時(shí),提示“clock has stopped,unable to arm ILA”

答:

該提示是說(shuō),時(shí)鐘信號(hào)停止了,也就是說(shuō)上述做對(duì)中g(shù)tx_rx_clk沒有像時(shí)鐘那樣,高低高低變化。請(qǐng)檢查該信號(hào),是不是拼寫錯(cuò)誤,還是說(shuō)該時(shí)鐘確實(shí)沒有。

【問題17】Unrouted nets:4 net(s) are unrouted .The problem bus(es) and/or net(s) are............

答:出現(xiàn)這個(gè)錯(cuò)誤的原因一般是:

xdc文件中的約束不正確或者沖突,解決方法如下

1、根據(jù)實(shí)際使用情況重新進(jìn)行約束

2、在將IOB屬性更改為TRUE

【問題18】

在vivado軟件中燒寫比特流時(shí),打開硬件目標(biāo)找不到JTAG,open target連接不上,顯示信息為:INFO: [Labtools 27-2285] Connecting to hw_server url TCP:localhost:3121

答:1.確認(rèn)已經(jīng)鏈接了下載器?

2.確認(rèn)開發(fā)板已經(jīng)通電狀態(tài)?

3.有可能是下載器壞了,可以更換下載器看看?

4.有可能是板子硬件有問題 可以換板子試試看

5.有可能是Vivado的驅(qū)動(dòng)沒有安裝好,只需要將驅(qū)動(dòng)安裝上即可,建議在安裝的過(guò)程中,將vivado關(guān)閉以及Jtag連接器先拔掉,安裝驅(qū)動(dòng)成功后在重新開始打開vivado進(jìn)行連接;否則可能會(huì)在安裝后也不能正常連接。在點(diǎn)擊open target時(shí),請(qǐng)將設(shè)備電源打開。

【問題19】

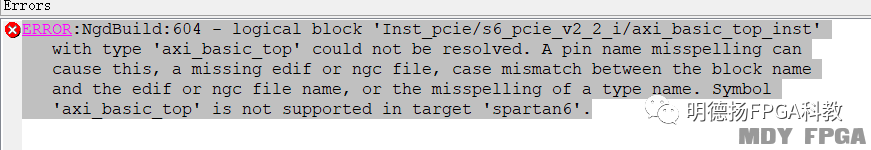

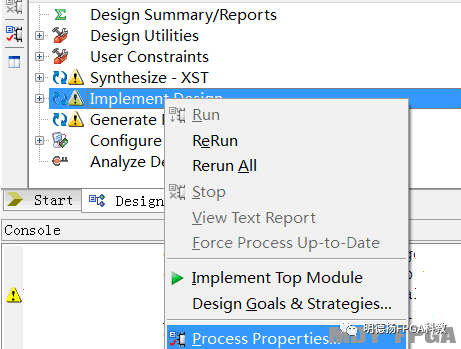

答:這是因?yàn)槲覀冊(cè)谔砑游募r(shí)候,忘記添加NGC文件到工程目錄中。下面就演示如何添加NGC文件到工程目錄中。NGC文件既要添加到Synthesize的目錄下,也要添加到Implement目錄下。

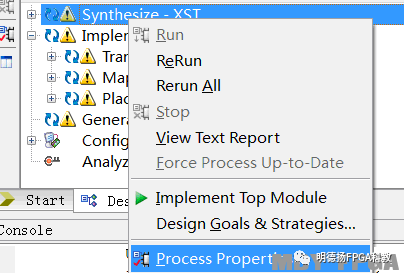

第一步:在Synthesize下添加NGC文件

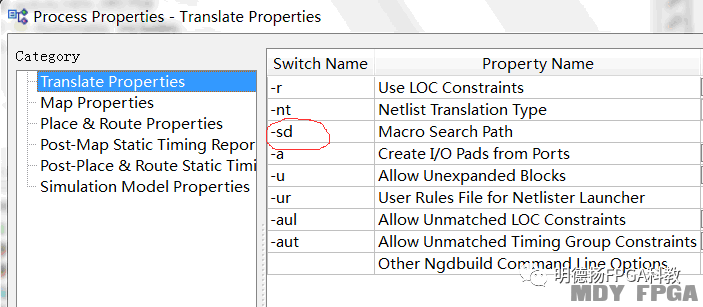

如圖在SynSynthesize中選擇Process Properities

在Synthesis Options中可以看到-sd和-vlgincdir。在-sd一欄中添加工程中所有的ngc或的edn文件的路徑目錄。在-vlgincdir中添加define.v文件的目錄。

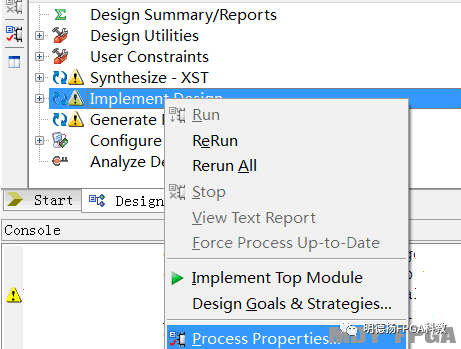

第二步:在到Implement目錄下添加NGC文件

如圖在Implement Design中選擇Process Properities。

在Translate Properties中的-sd一欄中添加添加工程中所有的ngc或的edn文件的路徑目錄否則translate的時(shí)候會(huì)出錯(cuò)。

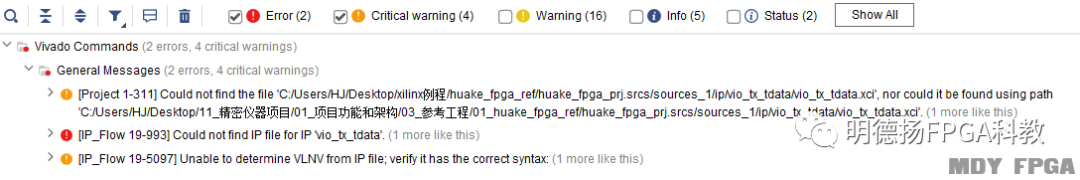

【問題20】打開MDY的工程后,會(huì)提示如下錯(cuò)誤信息。

答:1. 工程中的路徑,不要有中文的。

上面提示是IP核找不到。但這些IP核有可能是沒有用到的,所以這個(gè)錯(cuò)誤可以不用理會(huì)。

【問題21】打開MDY的工程,IP核如下顯示,無(wú)法打開。

答:MDY的工程,在分享的時(shí)候會(huì)減少大小,會(huì)刪除很多無(wú)用的文件。用戶下載后,需要重新生成IP核或升級(jí)IP核。

方法是在IP核右鍵,reset IP,然后重新“generate” IP。

另外,不同的VIVADO版本,也會(huì)造成此情況,要特別留意。VIVADO版本要保持一致。

-

軟件

+關(guān)注

關(guān)注

69文章

4770瀏覽量

87156 -

IP核

+關(guān)注

關(guān)注

4文章

326瀏覽量

49428 -

Vivado

+關(guān)注

關(guān)注

19文章

808瀏覽量

66322

原文標(biāo)題:VIVADO軟件問題

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Vivado SDK軟件

Proteus應(yīng)用軟件訓(xùn)練總結(jié)報(bào)告要求

Vivado使用誤區(qū)與進(jìn)階

利用Vivado HLS加速運(yùn)行慢的軟件

Vivado高效設(shè)計(jì)案例分享

基于linux系統(tǒng)實(shí)現(xiàn)的vivado調(diào)用VCS仿真教程

Vivado軟件仿真DDS核的過(guò)程中應(yīng)該注意的問題

VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)

?Vivado開發(fā)軟件下板驗(yàn)證教程

Vivado調(diào)用Modelsim仿真

vivado軟件和modelsim軟件的安裝方法

VIVADO軟件使用問題總結(jié)

VIVADO軟件使用問題總結(jié)

評(píng)論