內(nèi)存條DIMM

在80286時(shí)代,內(nèi)存顆粒(Chip)是直接插在主板上的,叫做DIP(Dual In-line Package)。到了80386時(shí)代,換成1片焊有內(nèi)存顆粒的電路板,叫做SIMM(Single-Inline Memory Module)。由陣腳形態(tài)變化成電路板帶來(lái)了很多好處:模塊化,安裝便利等等,由此DIY市場(chǎng)才有可能產(chǎn)生。當(dāng)時(shí)SIMM的位寬是32bit,即一個(gè)周期讀取4個(gè)字節(jié),到了奔騰時(shí),位寬變?yōu)?4bit,即8個(gè)字節(jié),于是SIMM就順勢(shì)變?yōu)镈IMM(Double-Inline Memory Module)。這種形態(tài)一直延續(xù)至今,也是內(nèi)存條的基本形態(tài)。

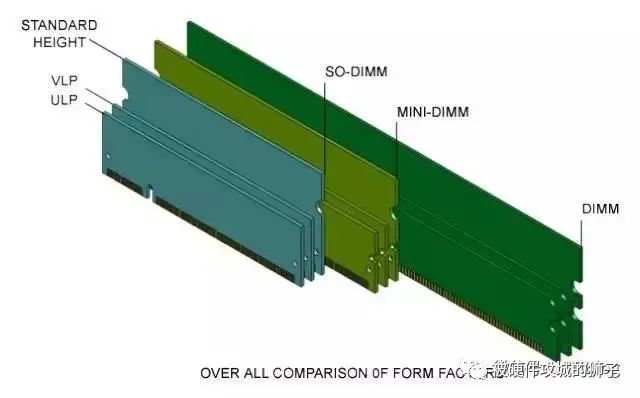

說(shuō)到這里,小張著急了:”這和我的內(nèi)存有啥關(guān)系?“。當(dāng)然有關(guān)系,就是和10600S的S有關(guān),現(xiàn)在DIMM分為很多種:

RDIMM: 全稱(Registered DIMM),寄存型模組,主要用在服務(wù)器上,為了增加內(nèi)存的容量和穩(wěn)定性分有ECC和無(wú)ECC兩種,但市場(chǎng)上幾乎都是ECC的。

UDIMM:全稱(Unbuffered DIMM),無(wú)緩沖型模組,這是我們平時(shí)所用到的標(biāo)準(zhǔn)臺(tái)式電腦DIMM,分有ECC和無(wú)ECC兩種,一般是無(wú)ECC的。

SO-DIMM:全稱(Small Outline DIMM),小外型DIMM,筆記本電腦中所使用的DIMM,分ECC和無(wú)ECC兩種。

Mini-DIMM:DDR2時(shí)代新出現(xiàn)的模組類型,它是Registered DIMM的縮小版本,用于刀片式服務(wù)器等對(duì)體積要求苛刻的高端領(lǐng)域。

一般內(nèi)存長(zhǎng)度 133.35mm,SO-DIMM為了適應(yīng)筆記本內(nèi)狹小的空間,縮短為67.6mm而且一般為側(cè)式插入。高度也有些變種,一般的內(nèi)存條高度為30mm,VLP(Very Low Profile)降低為18.3mm,而ULP(Ultra Low Profile)更是矮化到17.8mm,主要是為了放入1U的刀片服務(wù)器中。

大小關(guān)系如下圖:

小張這下知道10600S中S代表了SO-DIMM,看來(lái)大小沒錯(cuò)。不過(guò)速度呢?

DDR到DDR4

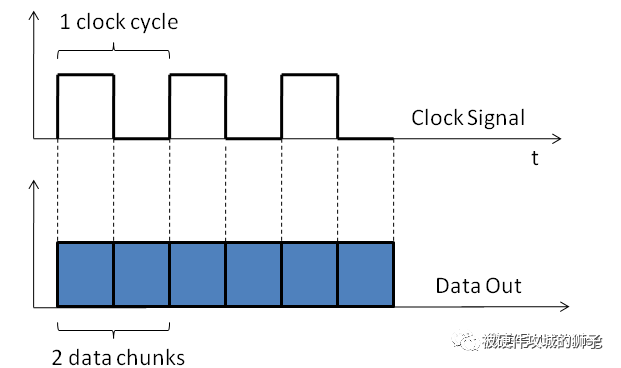

為了照顧小張的急性子,我就跳過(guò)了SDRAM后DDR和Rambus/RDRAM爭(zhēng)天下的故事。DDR SDRAM全稱為Double Data Rate SDRAM,中文名為“雙倍數(shù)據(jù)流SDRAM”。DDR SDRAM在原有的SDRAM的基礎(chǔ)上改進(jìn)而來(lái)。也正因?yàn)槿绱耍珼DR能夠憑借著轉(zhuǎn)產(chǎn)成本優(yōu)勢(shì)來(lái)打敗昔日的對(duì)手RDRAM,成為當(dāng)今的主流。顧名思義,和原本的SDRAM相比,DDR SDRAM一個(gè)時(shí)鐘周期要傳輸兩次數(shù)據(jù):

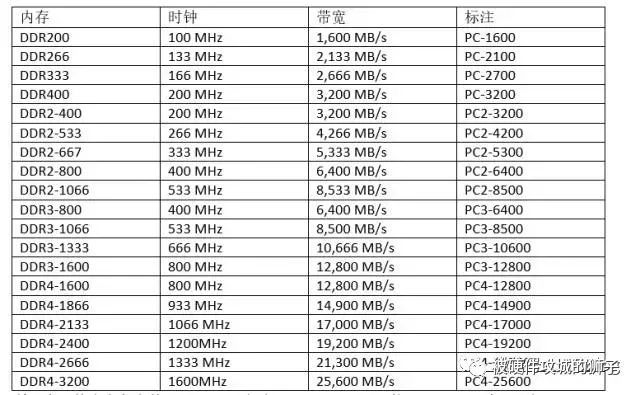

從DDR到DDR4主要的區(qū)別是在于傳輸速率的不同,隨著時(shí)鐘周期的不斷降低,傳輸率也不斷提高。還有電壓也越來(lái)越低。有趣的是命名規(guī)則,大部分臺(tái)式機(jī)DIMM廠商都會(huì)標(biāo)注DDRx-yyy,x代表第幾代,yyy代表數(shù)據(jù)傳輸率。而大部分的SO-DIMM和RDIMM等則標(biāo)注PCx-zzzz,x還代表第幾代,zzzz則代表最大帶寬。因?yàn)镈DR位寬為64位,8個(gè)字節(jié),所以zzzz=yyy * 8,而yyy又是時(shí)鐘的兩倍。下面這張表是主要的各代DDR內(nèi)存的速度:

所以小張的內(nèi)存條上的PC3-10600S代表DDR3,1333MHz的SO-DIMM。小張又問,那2R*8啥意思呢?

RANK和BANK

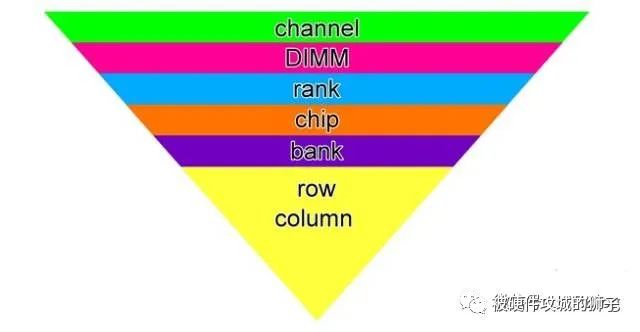

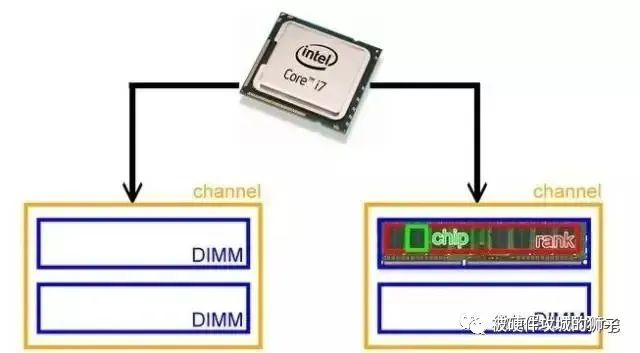

其實(shí)從外觀上就可以看出來(lái)小張的內(nèi)存條由很多海力士的內(nèi)存顆粒組成。從內(nèi)存控制器到內(nèi)存顆粒內(nèi)部邏輯,籠統(tǒng)上講從大到小為:channel>DIMM>rank>chip>bank>row/column,如下圖:

一個(gè)現(xiàn)實(shí)的例子是:

在這個(gè)例子中,一個(gè)i7 CPU支持兩個(gè)Channel(雙通道),每個(gè)Channel上可以插倆個(gè)DIMM,而每個(gè)DIMM由兩個(gè)rank構(gòu)成,8個(gè)chip組成一個(gè)rank。由于現(xiàn)在多數(shù)內(nèi)存顆粒的位寬是8bit,而CPU帶寬是64bit,所以經(jīng)常是8個(gè)顆粒可以組成一個(gè)rank。所以小張的內(nèi)存條2R X 8的意思是由2個(gè)rank組成,每個(gè)rank八個(gè)內(nèi)存顆粒。由于整個(gè)內(nèi)存是4GB,我們可以算出單個(gè)內(nèi)存顆粒是256MB。

首先RDIMM 16GB 2R*8是什么意思

16GB代表總的容量是16GB,

2R代表一共有2Rank的總線寬度,不考慮ECC的時(shí)候,一個(gè)Rank是64位,

8代表一個(gè)Chip的位寬是X8,

總結(jié):一個(gè)Rank包含8個(gè)X8的Chip,那么2R就說(shuō)明一共16個(gè)Chip;假設(shè)每個(gè)Chip都是單die的,那么Chip的大小就是1GB的。

其次RDIMM 16GB 2R*4是什么意思

16GB代表總的容量是16GB

2R代表一共64*2的總線寬度

4代表Chip的位寬是X4,

總結(jié):假設(shè)一個(gè)Chip中只有一個(gè)die那么Chip的數(shù)量就是2*64/4=32顆,每一顆的容量就是16GB/32=0.5GB,也就是4Gb;

再次RDIMM 32GB 2R*4是什么意思

32GB的容量

2*64的寬度

X4的位寬,

總結(jié):顆粒=2*64/4=32顆,那么每一顆的容量就是1GB,也就是8Gb;

再次LRDIMM 64GB 4R*4 是什么意思

64GB的容量

4*64的寬度

X4的位寬,

總結(jié)代表顆粒是4*64/4=64顆,但是其實(shí)DIMM最大只能放32個(gè)Chip,每個(gè)Chip上有兩個(gè)Die,每個(gè)Die是1GB;

最后3DS LRDIMM 64GB 4R*4是什么意思

64GB的容量

4*64的寬度

X4的位寬,Die一共是64顆,每顆1GB,一個(gè)Chip兩個(gè)Die

問題來(lái)了3DS代表3維堆疊,如果一個(gè)Chip中可以放4個(gè)Die那么這個(gè)DIMM怎么命名呢

4個(gè)Die,一個(gè)Die1GB,一個(gè)Chip是4GB,那么32個(gè)Chip最大是128GB,一個(gè)die的位寬是X4的話,32Chip*4Die*X4位寬/64=8Rank,因此可以稱為是3DS LRDIMM 128GB 8R*4或者3DS RDIMM 128GB 8R*4

最后一個(gè)問題RDIMM代表寄存器DIMM就是將地址和控制總線進(jìn)行緩存的DIMM,這樣信號(hào)更好一些,LRDIMM比前者更進(jìn)一步,將數(shù)據(jù)總線也進(jìn)行緩存,進(jìn)一步提高可靠性。

內(nèi)存顆粒chip

DDR4 協(xié)議標(biāo)準(zhǔn)中規(guī)定了幾種 DRAM 顆粒的容量規(guī)格,這些規(guī)格包含哪些方面?本文將討論這個(gè)話題。

DRAM 容量規(guī)格

DDR4 (下文可能混合使用 DDR4/DDR/DRAM, 皆為同義)顆粒在容量上有四種規(guī)格,分別為 2Gb、4Gb、8Gb 以及 16Gb。

DRAM 顆粒的容量 = 地址數(shù)量 x 位寬

每種顆粒容量規(guī)格,提供了 3 種地址數(shù)量和位寬的組合,以 2Gb 顆粒為例:

| 容量 (Gb) | 位寬 (b) | 選址數(shù)量 |

|---|---|---|

| 2 | 4 | 512M |

| 2 | 8 | 256M |

| 2 | 16 | 128M |

提供多種組合目的是為了提供靈活的配置方案。因?yàn)橐粋€(gè)嵌入式系統(tǒng)的 DRAM 位寬一般為 32 或者 64 比特(在 PC 上有更大的位寬),需要拼接多片 DDR4 顆粒才能提供這么多比特,那么使用不同位寬的 DDR 顆粒就會(huì)有不同拼接方案。

以 32 比特位寬,嵌入式系統(tǒng)為例,使用不同位寬的 2Gb 顆粒,有以下幾種組合:

| 系統(tǒng)位寬 (b) | 系統(tǒng)容量 (Gb) | 2Gb x4 顆粒數(shù)量 | 2Gb x8 顆粒數(shù)量 | 2Gb x16 顆粒數(shù)量 |

|---|---|---|---|---|

| 32 | 16 | 8 | ||

| 32 | 8 | 4 | ||

| 32 | 4 | 2 |

一般系統(tǒng)位寬的需求是固定的,而顆粒容量和位寬是一對(duì)可調(diào)整的參數(shù),提供不同的系統(tǒng)容量,仍以 32 比特系統(tǒng) DRAM 位寬為例:

|

2Gb 顆粒 |

4Gb 顆粒 | 8Gb 顆粒 | 16Gb 顆粒 | |||||

|---|---|---|---|---|---|---|---|---|

| 顆粒位寬 (b) | 系統(tǒng)容量(Gb) | 數(shù)量 | 系統(tǒng)容量 (Gb) | 數(shù)量 | 系統(tǒng)容量 (Gb) | 數(shù)量 | 系統(tǒng)容量 (Gb) | 數(shù)量 |

| x4 | 16 | 8 | 32 | 8 | 64 | 8 | 128 | 8 |

| x8 | 8 | 4 | 16 | 4 | 32 | 4 | 64 | 4 |

| x16 | 4 | 2 | 8 | 2 | 16 | 2 | 32 | 2 |

上表中的數(shù)量指的是系統(tǒng)的 DDR 顆粒總數(shù)量。有點(diǎn)與直觀感覺違背的事實(shí)是,采用的位寬更大的顆粒,系統(tǒng)的總?cè)萘扛汀?/p>

這是因?yàn)橄嗤萘康念w粒,位寬越大,地址數(shù)量也就越少,所以系統(tǒng)位寬固定時(shí),決定系統(tǒng)容量的是顆粒的地址數(shù)量:

系統(tǒng)容量 = 地址數(shù)量 x 系統(tǒng)位寬

接下來(lái)我們來(lái)看顆粒的地址數(shù)量以及其尋址方式。我們知道 DDR4 的尋址由 COL - ROW* - BANK- BANKGROUP 組成(單個(gè) RANK 時(shí))。

*COL, column, 指 DRAM 內(nèi)部存儲(chǔ)陣列中的列

**ROW, row , 指 DRAM 內(nèi)部存儲(chǔ)陣列中的行

顆粒的列數(shù)量是固定的 1024 列,而行、Bank(BA)、Bank Group (BG) 數(shù)量在不同位寬時(shí)則是不同的。

| 位寬 (b) | 選址數(shù)量(M) | 行數(shù)量 | 列數(shù)量 | BG 數(shù)量 | 每個(gè) BG 中 BA 數(shù)量 |

|---|---|---|---|---|---|

| 4 | 512 | 32768 | 1024 | 4 | 4 |

| 8 | 256 | 16384 | 1024 | 4 | 4 |

| 16 | 128 | 16384 | 1024 | 2 | 4 |

地址所屬的行、列、BA 以及 BG 的尋址是通過(guò)對(duì)應(yīng)的地址線尋址得到,所以不同位寬的顆粒地址線的數(shù)目也不同。

| 位寬 (b) | 行地址線數(shù)目 | 列地址線數(shù)目 | BA 地址線數(shù)目 | BG 地址線數(shù)目 |

|---|---|---|---|---|

| 4 | 15 | 10 | 2 | 4 |

| 8 | 14 | 10 | 2 | 4 |

| 16 | 14 | 10 | 2 | 2 |

由于行列地址線是分時(shí)復(fù)用的,以 x4 位寬為例,行列共享 A0-A14 地址線中的 A0-A9,所以 x4 位寬總地址數(shù)量為 15 (A) + 2 (BA) + 2 (BG) = 19。

這里我們看到使用小位寬顆粒雖然能夠拼接更多顆粒,提供更大的系統(tǒng)容量,但是所需要的地址線較 x8 和 x16 的顆粒也更多。這是更大系統(tǒng)容量的代價(jià),或者說(shuō)是系統(tǒng)容量與地址線數(shù)量的折中考量( trade-off)。

| 位寬 (b) | 總地址線數(shù)目 | 行地址線 | 列地址線 | BA 地址線 | BG 地址線 |

|---|---|---|---|---|---|

| 4 | 19 | A0-A14 | A0-A9 | BA0-BA1 | BG0-BG1 |

| 8 | 18 | A0-A13 | A0-A9 | BA0-BA1 | BG0-BG1 |

| 16 | 17 | A0-A13 | A0-A9 | BA0-BA1 | BG0 |

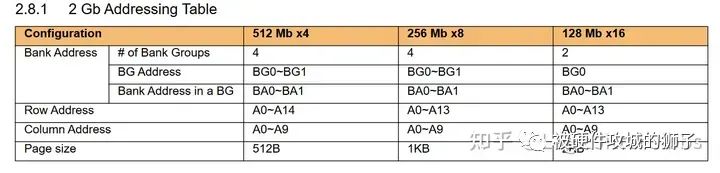

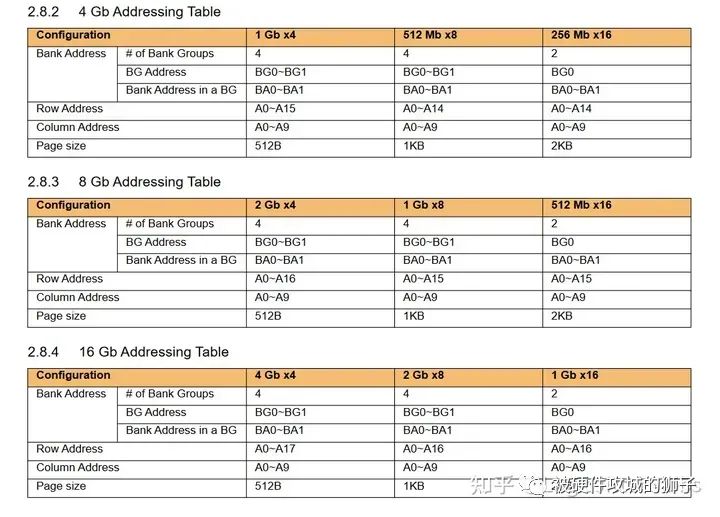

下面幾張圖都摘自 DDR4 協(xié)議 2.8 節(jié),列出了 DDR4 支持的四種容量顆粒的屬性,從中我們可以發(fā)現(xiàn)幾點(diǎn):

地址線最多的是 16Gb 容量的 x4 顆粒,使用 A0-A17 地址線。需要注意的是所有 PHY 都會(huì)有 A0-A16 (因?yàn)?RAS_n 復(fù)用為 A16),但有些 PHY 可能不支持 A17。

所有顆粒每個(gè) Bank Group 都有 4 個(gè) Bank

但是,x16 顆粒只支持 2 個(gè) Bank Group,而其他顆粒支持 4 個(gè)

x4 顆粒的地址線最多,而 x8 和 x16 顆粒的地址線數(shù)目相同,比 x4 少 1。x8 和 x16 的選址數(shù)目差異體現(xiàn)在 x16 的 Bank Group 少一半

另外值得一提的是頁(yè)大小(Page size),等于一行中的數(shù)據(jù)數(shù)量,直觀來(lái)說(shuō)頁(yè)大小與位寬直接相關(guān)。

Page size = 位寬 x 列數(shù)量 = 位寬 x 1K

對(duì)于 x4 顆粒,頁(yè)大小 = 4b x 1k = 4kb = 512B

順序讀取同頁(yè)數(shù)據(jù)時(shí),每次讀取之間是基本無(wú)需等待的。而非同頁(yè)數(shù)據(jù)之間,則需要按照協(xié)議要求,在兩次讀取之間增加延遲。舉例而言, x16 顆粒上可以無(wú)延遲順序讀取 2KB 數(shù)據(jù),但是如果是一個(gè) x8 顆粒,則需要在讀取完 1KB 數(shù)據(jù)后,關(guān)閉當(dāng)前行并且打開下一行,才能讀取后 1KB 數(shù)據(jù),需要增加的延遲大約在幾十個(gè)時(shí)鐘周期量級(jí)。

最后,我們?cè)谇拔闹惺褂?4b x 512M 來(lái)描述一個(gè) x4 顆粒,這是從顆粒位寬 x 地址數(shù)量的角度出發(fā)。協(xié)議中的稱呼為 512Mb x 4,個(gè)人覺得兩種稱呼都可使用吧,筆者自己平時(shí)也沒特別在意。

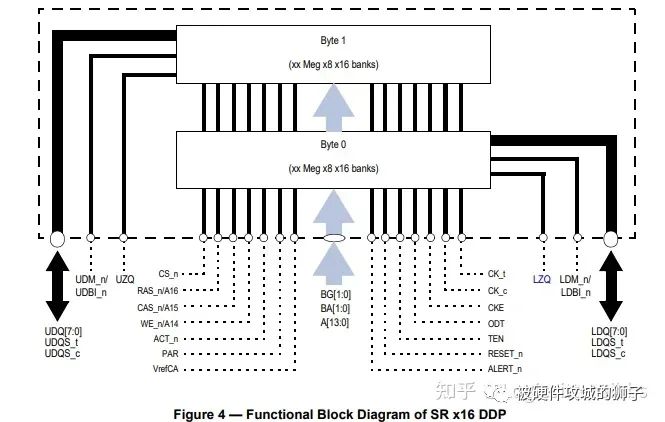

DDP 顆粒

最后討論一種容量比較特別的顆粒,也是最近工作中遇到的。事情是這樣的,客戶提問說(shuō) SoC 能不能支持一種 4GB 的 DDR4 顆粒。閱讀完本文的讀者知道,DDR4 最大只有 16Gb(2GB)的顆粒,哪來(lái)的單顆 4GB 顆粒?

看了客戶發(fā)來(lái)的顆粒 spec (是三星的顆粒)才知道,客戶想使用的是一種特殊封裝的顆粒,DDP(Dual Die Package),在協(xié)議的 2.9 節(jié)有簡(jiǎn)略的介紹。

DDP 顆粒顧名思義就是將兩個(gè) x8 Die 封裝在一起,這樣最大能夠提供單顆 32Gb (2 x8 16Gb)的容量。

兩個(gè) Die 的連接方式如下圖所示,它們的 CA 在封裝內(nèi)被堆疊(或者焊接)到一起,往封裝外引出各自的 DQ 和 DQS 引腳。

協(xié)議中提到,除了具體產(chǎn)品手冊(cè)的特殊注明外,DDP 顆粒的特性以及時(shí)序和普通的 x8 顆粒相同。

DDP 的好處是可以節(jié)省 PCB 的空間和布局布線時(shí)的難度,另外,因?yàn)閮蓚€(gè) Die 之間的 CA 信號(hào)延遲會(huì)非常小,筆者覺得或許可以跳過(guò)兩個(gè) Die 之間的 write leveling 訓(xùn)練。

DDP 的劣勢(shì)就顯然易見,或許因?yàn)轭~外的封裝成本,價(jià)格會(huì)相對(duì)更高,自然用戶就會(huì)比較少,用戶越少,價(jià)格也就越昂貴,供貨越得不到保證,半導(dǎo)體行業(yè)典型的惡性循環(huán)就出現(xiàn)了。基于這些考慮,我們的客戶后來(lái)也放棄了這個(gè)想法。

審核編輯:湯梓紅

-

電路板

+關(guān)注

關(guān)注

140文章

4911瀏覽量

97452 -

內(nèi)存條

+關(guān)注

關(guān)注

0文章

143瀏覽量

19504 -

DIMM

+關(guān)注

關(guān)注

0文章

26瀏覽量

9561 -

內(nèi)存顆粒

+關(guān)注

關(guān)注

0文章

5瀏覽量

1534

原文標(biāo)題:解讀內(nèi)存條和內(nèi)存顆粒的標(biāo)簽

文章出處:【微信號(hào):被硬件攻城的獅子,微信公眾號(hào):被硬件攻城的獅子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DDR內(nèi)存條對(duì)比分析

內(nèi)存條顆粒哪個(gè)好?內(nèi)存條顆粒排行!快來(lái)看看你的內(nèi)存條顆粒排在哪里 #電腦 #電腦知識(shí)

內(nèi)存條芯片參數(shù)

FPGA對(duì)DDRSDRAM內(nèi)存條的控制

詳解內(nèi)存條和內(nèi)存顆粒

詳解內(nèi)存條和內(nèi)存顆粒

評(píng)論