點擊藍字關注我們

點擊文末的“贊”和“在看”,并發送截圖和您的郵箱地址到后臺,即可領取原版PDF文檔哦~

對于外部條件可能出現極端變化的汽車應用而言,了解并準確估計器件的熱響應是一個長期存在的挑戰。以瞬態或連續溫度波動形式表現的超過器件熱容量的熱過應力,是該領域中最常遇到的故障模式之一,尤其是功率器件,在其壽命期間經常觀察到這種瞬態。此外,隨著硅特征幾何形狀、芯片和封裝尺寸不斷縮小,產生“熱斷裂”的可能性越來越大。這需要全面了解器件的熱響應和外部因素的影響,例如器件安裝情況、應用板、外圍熱源/熱匯等。從設計角度看,布局、結構和保護特性(包含在器件中)應考慮對目標應用中熱性能的影響。本部分描述上述內部和外部因素在確定和/或實現系統所需熱行為方面的作用。此外,本部分還會解釋量化熱性能的相關指標以及相應的示例性數據表規格。最后將討論限流和熱關斷(絕對和差分)等保護特性的設計理念,以及由此帶來的熱性能改進。

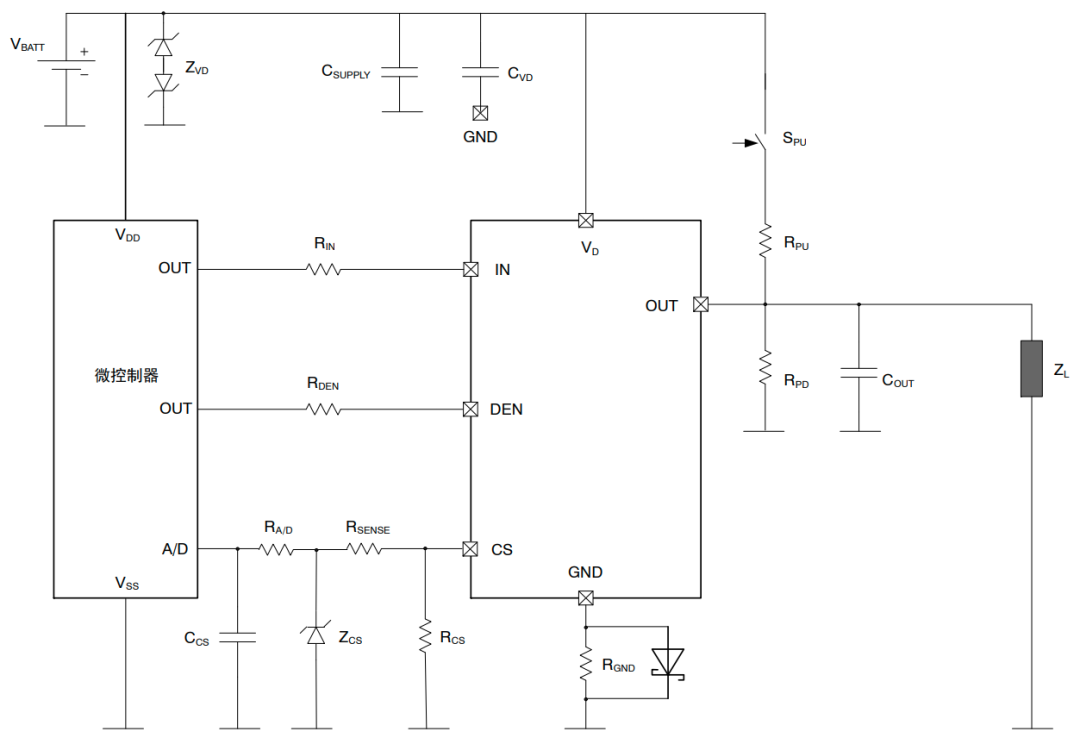

在半導體行業中,瞬態和穩態熱阻參數常被用來量化器件的熱性能。此參數通常在產品數據表中的某一組條件下指定。而在數學上,此參數被描述為 °C/W,即施加于器件的功率所造成的溫度變化;該物理表示類似于其電學上的對應物——通過產生熱勢(類似于電壓)來阻礙/抵抗熱流(類似于電流)的量。圖69描繪了逐層結構,即應用中的熱勢分割器階梯。

圖69:應用中的熱阻物理階梯

在解釋上面的分層結構之前,假設功率脈沖被施加到器件上。在這種情況下,器件和“周圍環境”的溫度將升高,熱量將開始以熱通量的形式流動。一旦電源關閉,溫度便開始下降,最終達到穩態或平衡。

現在,假設通過器件的電流密度均勻且沒有表面缺陷,那么器件的結將觀察到最大溫度擺幅。由于結被限制在相當淺的深度,因此在近表面區域可觀察到最高溫度。在電流密度不均勻的情況下,近表面區域的一部分會導通更多電流,從而產生熱點(可能會不可逆地損壞芯片),這使得我們難以模擬平均結溫。熱通量路徑中的下一層統稱為“硅”,包括基板、外延層和任何植入物(不在結附近)。芯片的厚度對實現所需的熱性能起著關鍵作用,尤其是在短時間的功率事件中(這將在后面討論)。芯片越厚,熱量流出器件所需的時間就越長,熱通量遇到的熱阻就越大。這就需要權衡參數,因為需要較大的外延厚度來支持所需的擊穿電壓并確保晶圓的機械穩定性(尤其是對于大直徑晶圓)。此外,基板的材料、有無體積缺陷也會影響熱量從器件流出。例如,相比于硅基板,在絕緣硅片基板上實現的器件具有更低的漏電流,閂鎖可能性更小,但熱阻更高。另一方面,SiC(碳化硅)之類的材料具有比 Si 更高的熱導率。因此,決定基板的材料和物理特性時,應該考慮最終器件的期望熱性能。

在基板之后,階梯中的下一層是背面金屬,接著是焊料。安森美高邊 SmartFET 系列中的所有產品都有背面漏極觸點,以通過將電流密度分布在整個基板接觸區域來管理高功率需求。金屬的選擇也決定了熱阻。圖69所示的結構假設漏極端子有一個背面凸耳或“裸露焊盤”連接(根據器件和技術的不同,它可能存在也可能不存在)。這通常是利用焊料作為凸耳的導電芯片連接來實現的。焊料層的厚度應均勻,并與漏極觸點共形。焊料中的空隙是已知的會導致高瞬態熱阻的故障模式。在源極側,源極觸點的功率金屬化和焊線組決定并限制了器件的熱性能。在凸耳層(包括引線框架、模塑料和封裝)之前,假設熱流模型為一維(這是合理的),熱流垂直流動。這一點之前的熱阻統稱為θJunction-Case,或稱為θJunction?Pin(如果沒有背面裸露焊盤),或稱為θJunction–Soldering Point。一旦熱量開始流出封裝,則還需要考慮所關注器件附近的任何其他熱源傳入的橫向熱通量,該模型可能會變成三維熱流網絡,這通常更難分析和估計。然而,這一假設并不總是適用于多通道器件,因為相鄰通道可能會導通功率并將熱量橫向散發到芯片中,從而使分析變得復雜。封裝層之后,安裝和應用條件決定熱阻。相關因素包括焊料量、應用PCB上的銅散熱器面積、走線的長度和寬度、PCB中的層數、用于熱導通的內部平面、應用PCB和ECU外殼之間使用的環氧樹脂(如有)的特性等。了解數據表曲線部分討論了其中一些因素對系統熱阻的影響。將所有這些階梯的電阻貢獻相加,即得到應用的結至環境總熱阻。

上面討論的階梯結構內的熱流范圍取決于脈沖時序和占空比。根據經驗和仿真結果,估計對于最長數百微秒的單脈沖功率事件,芯片有源面積、技術和物理特性決定了熱阻,外部應用環境對短脈沖持續時間內的熱響應的貢獻非常小。隨著(單)脈沖周期延長,引線框架、封裝、模塑料等開始對熱性能產生影響。對于幾毫秒的脈沖周期,這種影響通常很明顯。對于長達幾秒鐘的較長脈沖周期,應用條件(如上段所述)對熱阻的影響更大。當系統在長脈沖周期(通常超過100秒)內達到平衡時,器件本身對穩態熱阻的貢獻非常小,熱性能僅取決于測試條件。應注意的是,這些時間周期只是估計值,而且假設所施加的脈沖周期和功率水平完全在針對器件定義的邊界條件內,并且不會干擾針對保護電路定義的閾值,例如熱關斷。

重復功率脈沖事件情況下的熱阻取決于占空比。根據占空比的不同,功率脈沖中積累的熱量可能會也可能不會“結轉”到后續脈沖,這會使分析更加復雜。此外,電功率波和隨后的熱波之間有一個時間滯后,這點在重復脈沖事件的熱分析過程中必須考慮。參見下面示例性器件上的假設功率曲線對應的仿真熱波。

圖70:任意功率曲線的熱波滯后的仿真

如上一部分所述,相對較短時間(通常限于幾毫秒)內的瞬態熱阻更多地取決于器件,而不是應用條件。這里的“器件”包括來自芯片和封裝的貢獻。決定芯片的幾何和物理特性的主要考慮是為了優化性能參數,如導通損耗和擊穿電壓,因此芯片本身幾乎沒有任何改進的余地來提高熱能力。另一方面,封裝改進相對更站得住腳,與單脈沖和重復脈沖改進相比,它能顯著改善瞬態熱性能。

某些安森美高邊SmartFET(取決于技術和應用要求)集成了一個用于漏極端子的裸露焊盤或耳片連接,以改善散熱。圖 71 顯示了流經裸露焊盤的熱流。與尺寸相似的、漏極連接使用引腳分配或引腳組合(通過焊線焊接到背面漏極)的器件相比,裸露焊盤連接提供更好的瞬態熱性能。

圖71:漏極端子有裸露焊盤情況下的熱流

有了裸露焊盤,應用 PCB 上的焊料和散熱器面積也會增加,從而實現額外的散熱,幫助改善更長脈沖持續時間(>1秒)情況下的散熱。

除了漏極端子之外,功率流路徑中的另一個節點是源極端子。源極觸點、頂部功率金屬和引線框架的外合 (bond-out) 都會影響瞬態熱性能,從而決定器件的最大功率處理能力。大部分功耗發生在結深較淺的地方,因此必須考慮源極頂部金屬的熱導率和厚度,尤其是在設計高功率密度器件時。一些高功率安森美SmartFET采用銅頂部金屬代替傳統的鋁合金,以改善熱阻。如果器件的RDS(ON)極低(如NCV84004A、NCV84006A等),與“后端技術”(包括焊線)相關的間接電損耗往往會限制器件的參數性能。對于此類器件,“銅夾片”形式的焊接替代方案可提供出色的電氣和熱性能。銅夾片覆蓋功率 FET 的整個有源區域,并瞬間將熱量從硅片傳遞到引線框架,從而起到頂部散熱器的作用。

雖然對低RDS(ON)的高功率器件有利,但在高功耗的情況下,銅夾片布局和放置對于芯片的穩定性而言是一個重大問題。銅夾片邊緣周圍的任何未暴露區域都可能產生局部熱點,成為熱失控的場所。對于控制電路位于控制邏輯旁邊、饋通信號布線的空間狹窄的單片器件,解決這一問題尤為重要。布局一個銅夾片并保持其在整個FET區域上的一致性通常是很有挑戰性的。在這種情況下,應探索改善熱性能的其他途徑,包括但不限于改變頂部金屬疊層的組成和厚度、增加焊線的數量和/或厚度。

此外,對于功率需求較低的器件,由于可用于焊接的硅面積較小,銅夾片放置還面臨經濟和技術限制。這些器件采用焊線將漏極和源極連接到引線框架。通過采用多條焊線,以及(在某些情況下)為每條這樣的焊線使用多次縫合,可以增強熱性能。還應用了其他封裝增強方法,例如:改善模塑料化學特性,以及優化焊接參數以避免產生“熱破裂”。

總之,焊接類型和頂部金屬疊層取決于可制造性的難易程度和特定器件所需的電熱性能。

熱阻——物理解釋部分說明了熱阻的物理解釋。此解釋盡管對于了解熱網絡是必不可少的,但可能無法進行建模、仿真以及在產品數據表中從數學上加以規定,從而量化和比較器件的熱性能。

出于數據表的目的,對于給定的芯片和封裝,瞬態和穩態熱測量是在實驗室設置條件下的受控環境中進行的,熱阻是通過記錄已知功率脈沖引起的溫度變化來測量的。這種溫度變化通常通過分析預校準片內溫度計的參數變化——例如功率 FET 的體二極管的正向壓降——來測量。該溫度計在空間上應該靠近結;在某些情況下,它是專門制造的,用來模擬熱剖面。在固定溫度時,熱接地(對于結至環境測量,其為環境;對于結至外殼/結至引腳測量,其為外殼/引腳)通過強制對流和散熱保持穩定(以快速消散系統接地的熱量)。此外,利用 SPICE、ANSYS 等可用建模工具對器件進行熱仿真。完成測量并繪制圖形后,建立一個數學R-C仿真模型來擬合該測量曲線。圖 72 顯示了仿真的Foster R-C網絡。

圖72:Foster R-C網絡模型

R和C的連接使得階梯中的每個“梯級”具有唯一的時間常數,其中:

(公式18)

(公式18)

每個梯級的貢獻與其時間常數成反比;隨著系統向穩態發展,時間常數越長的梯級貢獻越大。盡管如此,但Foster網絡中的電阻和相應的時間常數沒有物理意義,即它們與熱阻——物理解釋部分中描述的物理梯形結構不相關。此外,階梯中梯級的順序和數量也是任意的,并且可以改變。換言之,Foster階梯是擬合實測熱阻曲線的純數學模型。梯級數越多,精度越高,相對于實際曲線的誤差系數越小。使用Foster模型的優點是易于仿真。一旦一個器件有了R-C網絡,那么為該系列中的其他器件創建R-C模型(從而生成瞬態熱阻曲線)就相對容易,只需改變仿真模型的輸入,如功率FET的器件有源面積、總硅面積等。梯形圖中R的總和就是系統的結至環境總熱阻。

另一類R-C階梯是Cauer網絡,如下圖73所示。在該網絡中,電容全都連接到系統的熱接地,每個階梯中的 R 和 C 與物理梯形結構直接相關。從階梯中可以直觀地觀察到,靠近結的梯級將首先充電(熱意義上),朝向接地的梯級只有當上面的梯級發生熱量飽和時才會充電。因此,靠近結的梯級可以與器件和封裝相關,而靠近環境地的梯級可以與外部應用條件(如 PCB)相關,但器件與其外圍之間沒有明確的界限。

圖73:Cauer R-C網絡模型

雖然Cauer網絡階梯中的電阻總和也能得出總熱阻,但各個梯級與Foster網絡不同。通過觀察Cauer R-C網絡的相應變化,可以更好地認知系統條件的變化(幾個具有相似時間常數的物理貢獻因素與其數學等價物之間的關系相當復雜)。Cauer網絡一般很難建模,也很難從一個器件轉置到另一個器件,而且它一般是利用已知算法根據其 Foster 對應網絡來計算。

安森美高邊SmartFET系列的數據表可能包括也可能不包括這些R-C模型,具體取決于特定產品。然而,這些模型可以根據客戶的具體要求提供。

除非另有說明,數據表列出了穩態結至環境熱阻和結至外殼/引腳/焊點的熱阻,同時給出了瞬態熱阻圖。應注意的是,這些熱阻是根據一組應用和安裝條件指定的,如PCB銅散熱器面積和厚度、FR4面積、電路板層數等。公布的曲線僅在這些條件下有效,如果應用條件與數據表中提到的條件不同,則不應使用這些曲線來估算結溫。按照同樣的思路,任何比較分析(安森美產品組合內的比較或與競爭器件的比較)只有在測試條件一致的情況下才能提供可靠結果。為此,應當遵循規定電路板幾何形狀和特性的某些標準,例如JEDEC JESD 51-3、51-7等。關于描述熱阻時遵循的一組條件,請參考相應的產品數據表。以圖74為例,考慮NCV84160的結至環境瞬態熱阻曲線:

圖74:瞬態熱阻示例性曲線-NCV84160

應注意的是,θ和R(t)可以互換使用,二者均用于描述器件的熱阻。上圖描繪了單個脈沖和一個PWM功率脈沖序列(由占空比定義)對應的熱阻。測量條件指定單層PCB,FR4面積為4.8cm*4.8cm,正面 1 盎司銅散熱器面積約為200mm2(一般只考慮漏極和源極端子),背平面覆蓋有 1 盎司銅散熱器,沒有內部平面。此外,假設被測器件附近沒有其他熱源在工作,否則這些熱源可能影響系統的熱剖面。走線/測試線的長度、過孔(如果有)的布置、測試板的方向和環境溫度的穩定性(通常通過強制對流實現)也是已知的會影響熱響應的因素,當然還有許多其他因素。因此,熱阻規格僅在上述條件下有效,而不能普遍適用于任何其他應用條件。為了量化應用條件變化的影響,圖75中的曲線描繪了同一器件 (NCV84160) 在與以上所述相同的條件下的熱阻,但正面銅散熱器面積從200mm2變為最小焊盤(銅區僅存在于封裝引腳的焊點處)。

圖75:瞬態熱阻示例性曲線-NCV84160,

正面銅面積為最小焊盤

在這種情況下,正面銅散熱器面積減少200mm2,穩態熱阻增加約16%。再舉一例,FR4 面積增加約75%,預計會使穩態電阻降低約7%(如圖73所示,FR4特性一般與非常長的時間常數相關,只有在脈沖持續時間較長的情況下才會有明顯的影響)。此處提供的數據僅對這種特定情況有效,不應擴展到其他器件,因為測試條件和對熱阻的相應影響可能不同。

假設在特定應用中,測試條件與圖74中公布的曲線所依據的條件相同,那么可通過下述近似計算來估計假想電感切換環境中的平均結溫。

考慮切換1 mH電感,峰值電流為5A,環境溫度為25°C,電池電壓為14V。忽略輸出導通路徑中的串聯電阻(這在實際應用中不一定如此)。下面的理想化波形集描述了這種情況:

圖76:假想電感切換事件的理想化波集-計算結溫

使用下面的公式計算tON和tAVAL,結果分別為約0.38ms 和約0.16ms。

(公式19)

(公式19)

(公式20)

(公式20)

這樣,充電和雪崩事件期間的平均功耗可以分別近似為2W和80W。這些功率水平的計算假設在充電和放電循環期間電流具有理想直線衰減曲線。在實際應用中,平均功率水平應該直接測量(大多數測量設備可以執行數學運算來輸出測量功率),而不是進行這些近似計算。

現在,參考圖74中的一組曲線,x 軸定義功率脈沖的時間周期,y軸指定不同占空比操作下的熱阻。從單脈沖曲線外推熱阻,在約0.38ms(充電周期)時熱阻約為 1.2°C/W,可以計算出溫升為1.2*2~2.4°C。對放電事件進行類似的外推,可以計算出溫升為0.8*80~64°C。將該溫升與環境溫度相加,SCIS事件結束時的結溫為25+2.4+64~92°C。

在重復開關的情況下,應參考占空比曲線,而不是單脈沖曲線。例如,如果圖76中的電感以100Hz的頻率切換,則時間周期為10ms。充電和放電事件的占空比分別為0.38/10~3.8% 和0.16/10~1.6%。可以對這些曲線進行插值以獲得估計的熱阻,并且可以用與上述類似的方式計算結溫。

這里的計算假設感應充電和放電事件具有一個平均矩形功率剖面當量,這并不完全準確,也不一定在每個應用中都成立。上述計算的目的是演示熱阻曲線的解釋和使用。如果對動態溫度變化感興趣,則需要將瞬時功率剖面輸入計算器,后者采用 Foster R-C 模型,并使用一組公式進行分段積分,以估計相應的溫度剖面。這種剖面可以根據客戶的具體請求提供。

所有上述計算和R-C網絡中展示的是結至環境熱阻模型,這是因為它在實際場景中更有意義。雖然結至外殼(或結至引腳)熱阻似乎是估算結溫的便捷工具,只需記錄功率事件期間的外殼溫度,但使用已公布的結至外殼熱阻數字可能會造成誤導。結至外殼測量背后的前提是假設器件的“外殼”被視為“熱接地”,無論結溫如何動態變化,它都應保持在固定的已知溫度。這種條件在實踐中很難實現,在短暫瞬變中幾乎不可能實現,因為外殼溫度隨著動態功率水平的變化而搖擺不定。此外,大多數溫度記錄器件(如熱電偶)的響應時間遠高于汽車 PWM 應用中施加的典型功率瞬變,因此很難預測準確的外殼溫度。相比之下,結至環境熱阻更可靠,因為在動態功率變化的情況下,我們可以更精確地控制環境溫度(通過適當的散熱和受控氣流)。

安森美高邊SmartFET中的保護特性(尤其是限流和溫度關斷)的設計考慮了器件的熱性能。低功耗器件采用線性限流和熱驅動的重試策略,而在密集技術上實現的高功率器件使用更精確的限流峰值檢測關斷和基于定時器的重試策略。從布局角度看,對芯片的熱圖進行仿真以評估該區域對施加的功率最敏感(就溫度變化而言)的部分。溫度檢測結構的布局是為了優化:a) 最大芯片溫度;b) 傳感器相對于芯片上最大溫度的線性度;c) 差分溫度檢測所需的變化量,以限制瞬態熱應力。在整合了銅夾片以覆蓋有源源極區域的器件中,這些傳感器的布置變得更具挑戰性。電流檢測結構的布局也考慮了電流密度分布的均勻性,同時避免形成制約通道,防止在芯片上產生熱點。除布局外,這些保護特性的模擬控制電路還需要針對所需的熱性能進行設計。在設計該電路時,主要考慮控制激活閾值和電路元件的溫度系數。

點擊文末的“贊”和“在看”,并發送截圖和您的郵箱地址到后臺,即可領取原版PDF文檔哦~

點個星標,茫茫人海也能一眼看到我

原文標題:SmartFET的熱響應,一文輕松get√

文章出處:【微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

-

安森美

+關注

關注

32文章

1650瀏覽量

91937

發布評論請先 登錄

相關推薦

TDK NTCRP系列熱敏電阻的熱響應性測量方法

一文搞懂用ZPC輕松拿捏數據上云

服務器對GET請求沒有響應是怎么回事?

一文掌握集成電路封裝熱仿真要點

一文讀懂車載紅外熱成像技術

文心一言APP上線數字分身功能

SmartFET模擬電流檢測解析(相關研討會預約中)

干貨 | 高邊SmartFET應用接口及開關特性的介紹

一文看懂Vue3響應式系統原理

SmartFET的熱響應,一文輕松get√

SmartFET的熱響應,一文輕松get√

評論