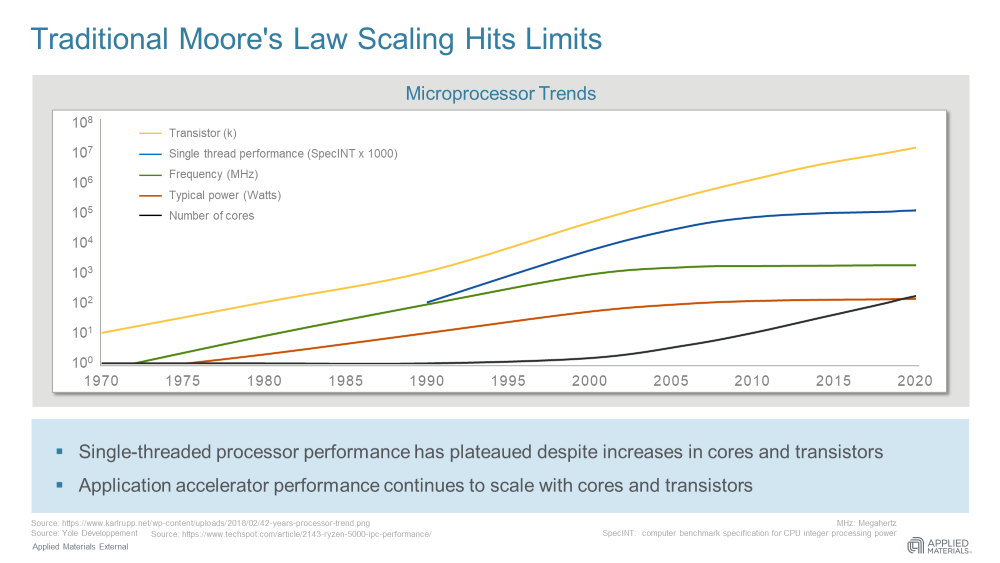

電子發(fā)燒友網(wǎng)報道(文/吳子鵬)幾年前,全球半導體產(chǎn)業(yè)的重心還是如何延續(xù)摩爾定律,在材料和設(shè)備端進行了大量的創(chuàng)新。然而,受限于工藝、制程和材料的瓶頸,當前摩爾定律發(fā)展出現(xiàn)疲態(tài),產(chǎn)業(yè)的重點開始逐步轉(zhuǎn)移到如何超越摩爾定律,時代的定義也從摩爾定律時代過渡到了后摩爾定律時代。

后摩爾定律時代,先進封裝和Chiplet技術(shù)被寄予厚望。近日,由博聞創(chuàng)意主辦的第七屆中國系統(tǒng)級封裝大會(SiP China 2023)上海站成功舉辦,活動上來自三星、安靠、芯和半導體等企業(yè)代表暢聊先進封裝和Chiplet技術(shù),讓我們感受到了產(chǎn)業(yè)的熱度,也對產(chǎn)業(yè)進程有了很清晰的了解。

Chiplet落地步驟和落地進展

Chiplet的中文翻譯為芯粒或小芯片。基于Chiplet的設(shè)計方案,從設(shè)計時就按照不同的計算單元或功能單元對其進行分解,系統(tǒng)中的不同組件在獨立的裸片上設(shè)計和實現(xiàn)。從芯片制造的角度來看,引入Chiplet概念之后,CPU、存儲器、模擬接口等功能單元可以靈活選擇工藝,并形成一種真正的IP復用——這些IP不需要再走后端與物理設(shè)計、流片制造、封裝測試等流程。雖然芯片制造不能擺脫對制程的依賴,但能夠降低先進制程上大芯片的設(shè)計復雜度,進而提升設(shè)計效率和制造良率,并降低芯片設(shè)計制造的成本。

總結(jié)來說,對于大芯片設(shè)計來說,Chiplet能夠在保證芯片設(shè)計PPA(性能、功耗和面積)指標的前提下,提升先進工藝的良率,并顯著降低芯片內(nèi)容錯電路的規(guī)模。真正的IP復用也是一種高性價比方式。

因此,芯和半導體創(chuàng)始人&CEO 凌峰博士在《Chiplet產(chǎn)業(yè)的發(fā)展和現(xiàn)狀》報告中指出,Chiplet是為了解決后摩爾定律時代,先進工藝制程逼近物理極限,芯片PPA提升放緩,經(jīng)濟效益降低等問題而應運而生的。

目前,Chiplet已經(jīng)成功落地于高性能計算應用,AMD、英偉達、英特爾、蘋果、谷歌、博通等公司均在自己的高性能運算芯片中使用了Chiplet技術(shù),代表產(chǎn)品包括AMD EPYC CPU和英偉達 H100 GPU等。2023年,國際大廠多款基于Chiplet技術(shù)的大芯片落地,比如AMD在MI3000X和RX 7000X中均使用了這項技術(shù)。發(fā)展至今,無論是同構(gòu)集成還是異構(gòu)集成,AMD均已經(jīng)有產(chǎn)品。

凌峰表示,目前已經(jīng)有超過100款基于Chiplet技術(shù)的系統(tǒng)設(shè)計,其中44%應用于服務器/人工智能領(lǐng)域,14%應用于網(wǎng)絡通信領(lǐng)域,13%應用于汽車電子領(lǐng)域。從封裝類型來看,56%的Chiplet系統(tǒng)設(shè)計使用標準基板,先進EMIB的占比為18%,先進CoWos和先進CoWos硅中介的占比分別是12%和8%。

未來5年內(nèi)多Chiplet系統(tǒng)設(shè)計將會實現(xiàn)5倍增長,并有四大發(fā)展趨勢:

·趨勢一:大規(guī)模高性能計算芯片推動Chiplet技術(shù)持續(xù)演進,面臨的挑戰(zhàn)與不足將逐步改善。

·趨勢二:后摩爾定律時代,Chiplet架構(gòu)的應用將由集群數(shù)據(jù)中心側(cè)逐步向邊緣和終端(手機、汽車等)下沉,算力普惠。

·趨勢三:Chiplet技術(shù)讓半導體產(chǎn)業(yè)生態(tài)更加開放多元,并催生新的協(xié)作模式和機遇。

·趨勢四:全球供應鏈受復雜局勢影響,助力加速Chiplet產(chǎn)業(yè)發(fā)展,自主創(chuàng)新與兼容互通是主旋律。

凌峰認為,Chiplet生態(tài)逐步走向成熟會分為四步。第一步是Chiplet全自研;第二步是接口標準制定;第三步是Chiplet外形規(guī)格標準;第四步是開放的Chiplet市場。很顯然,目前我們還處于第二步向第三步邁進的過程中。

從UCIe 1.0到UCIe1.1

從凌峰的演講不難看出,標準對于Chiplet發(fā)展是至關(guān)重要的。在SiP China 2023上海站,阿里云智能集團首席云服務器架構(gòu)師,CXL和UCIe董事會成員陳健分享了UCIe標準發(fā)展的一些進展,并闡述了從UCIe 1.0到UCIe1.1的具體改進。

作為一種開放的小芯片/芯粒互連協(xié)議,UCIe由UCIe 聯(lián)盟主導并發(fā)布,該聯(lián)盟成員包括AMD、Arm、ASE、Google Cloud、英特爾等科技巨頭。2023年8月,UCIe 聯(lián)盟公開發(fā)布UCIe 1.1規(guī)范,為芯片生態(tài)系統(tǒng)提供有價值的改進。

陳健詳細講解了UCIe 1.1規(guī)范帶來的新功能,包括將可靠性機制擴展到更多協(xié)議,支持更廣泛的使用模型,等等。且UCIe 1.1規(guī)范完全向后兼容UCIe 1.0規(guī)范。

綜合來看,UCIe 1.1規(guī)范帶來了具有完整 UCIe堆棧的流協(xié)議的新用途,包括具有端到端鏈路層功能的同步多協(xié)議支持。在UCIe 1.0規(guī)范中,只有原始模式支持串流協(xié)議,僅用于傳輸層。UCIe 1.1規(guī)范增加了串流協(xié)議,支持flit模式,堆棧多路復用器支持在單個UCIe實例中使用多個協(xié)議的組合。

汽車行業(yè)更新是UCIe 1.1規(guī)范的關(guān)鍵更新,包括用于汽車用途的其他增強功能,如預測性故障分析和健康監(jiān)測,以及實現(xiàn)更低成本的封裝實施。為了滿足汽車行業(yè)對高性能計算芯片的需求,UCIe 聯(lián)盟還特別成立了新的汽車工作組。

Chiplet和系統(tǒng)集成方案

根據(jù)Yole的統(tǒng)計數(shù)據(jù),2022年全球封測市場規(guī)模為815.0億美元,同比增長4.9%,預計到2026年市場規(guī)模有望達961.0億美元,2022年-2026年CAGR為4.2%。SiP China 2023上海站上,應用于Chiplet領(lǐng)域的系統(tǒng)集成技術(shù)也是一大亮點,包括安靠和三星等頭部企業(yè)都展示了自己的相關(guān)方案。

和Chiplet搭配,讓產(chǎn)業(yè)界對于先進封裝的重視程度更勝以往。先進封裝與Chiplet是兩個概念,但采用Chiplet的芯片大概率會采用先進封裝。反過來說,先進封裝能夠賦能Chiplet技術(shù)更好地發(fā)展。

安靠作為第二大封測龍頭廠商,一直致力于開發(fā)包括硅通孔、穿塑通孔、銅柱、銅混合鍵合等在內(nèi)的技術(shù)工藝,目前主要有WLCSP、WLFO、WL3D、DSMBGA、AiP/AoP和 SWIFT/HDFO六大先進封裝技術(shù)。一般來說,S-SWIFT設(shè)計有4個RDL(RDL優(yōu)先、芯片后上)結(jié)構(gòu),第1和第3層用于信號路由,第2層充當接地層。第4層則有多種用途,作為某個平面或用于銅柱 (CuP) 互連。

SWIFT封裝可以支持30到80微米凸塊節(jié)距(典型),第1-4 RLD層的線寬/線距為2/2微米。安靠的一些客戶考慮使用SWIFT技術(shù)來集成ASIC和小芯片(SerDes、HBM及其他)。憑借其出色的電屬性和靈活性,SWIFT技術(shù)還是晶片分割模塊的理想選擇。

三星電子總監(jiān)吳政達博士則主要介紹了三星的先進封裝技術(shù)(AVP)。根據(jù)他的介紹,AVP業(yè)務團隊利用三星在存儲器、邏輯芯片(系統(tǒng)LSI)和晶圓代工方面的前沿專業(yè)知識,為高性能、低功耗芯片提供先進的2.5D和3D封裝解決方案,使芯片的性能表現(xiàn)遠遠超過各部件的簡單累加。

三星AVP之所以能推動半導體行業(yè)進入“超摩爾定律時代”,背后的“秘密武器”是異構(gòu)集成技術(shù),這種先進封裝技術(shù)將多個芯片水平和垂直連接在一起。利用先進的異構(gòu)集成技術(shù),三星AVP可將多個存儲器和邏輯芯片集成到單一封裝中。相比傳統(tǒng)的分離式芯片組設(shè)計,集成式封裝芯片組速度更快、效率更高、適應性更強,同時生產(chǎn)成本更低。

當然,在SiP China 2023上海站上,很多嘉賓都提到,2.5D/3D封裝和Chiplet的結(jié)合依然有很大挑戰(zhàn)。比如,芯片必須保證在更小的封裝空間內(nèi)對更小尺寸的 Chiplet 芯片進行封裝,需要有很高的封裝造詣;如何用最佳的方式連接die并合理走線,也會帶來一些系統(tǒng)設(shè)計難題;如何進行合理的熱管理、散熱管理,如何實現(xiàn)芯片整體的高溫穩(wěn)定性,這些都具有挑戰(zhàn)性,等等。

結(jié)語

Chiplet技術(shù)的發(fā)展讓半導體產(chǎn)業(yè)界能夠重耕制造工藝和IP,也幫助降低基于先進制程的大芯片的復雜度,讓芯片設(shè)計重新變得經(jīng)濟高效。因此,Chiplet技術(shù)是后摩爾定律時代的關(guān)鍵技術(shù)之一。從SiP China 2023上海站能夠看出,目前Chiplet技術(shù)已經(jīng)取得了積極的進展,不過未來依然任重道遠。

-

摩爾定律

+關(guān)注

關(guān)注

4文章

632瀏覽量

78929 -

chiplet

+關(guān)注

關(guān)注

6文章

416瀏覽量

12558 -

先進封裝

+關(guān)注

關(guān)注

1文章

373瀏覽量

223 -

芯粒

+關(guān)注

關(guān)注

0文章

58瀏覽量

121

發(fā)布評論請先 登錄

相關(guān)推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

普渡機器人與香港特區(qū)政府簽約成為重點企業(yè)伙伴

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術(shù)迎百家爭鳴時代

“自我實現(xiàn)的預言”摩爾定律,如何繼續(xù)引領(lǐng)創(chuàng)新

封裝技術(shù)會成為摩爾定律的未來嗎?

依托廣立微建設(shè)的浙江省集成電路EDA技術(shù)重點企業(yè)研究院正式掛牌

摩爾定律的終結(jié):芯片產(chǎn)業(yè)的下一個勝者法則是什么?

Chiplet技術(shù)對英特爾和臺積電有哪些影響呢?

英特爾CEO基辛格:摩爾定律仍具生命力,且仍在推動創(chuàng)新

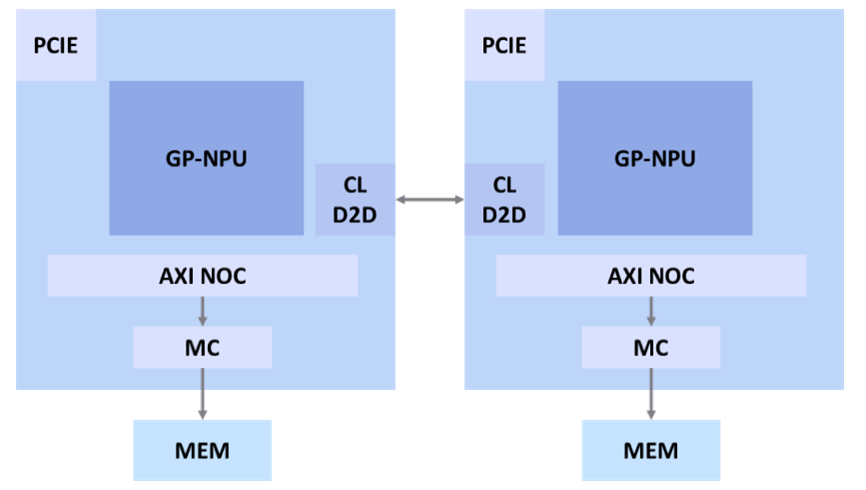

燧原科技和芯礪智能發(fā)布Chiplet高效NPU聯(lián)合計算架構(gòu)

后摩爾定律時代,Chiplet落地進展和重點企業(yè)布局

后摩爾定律時代,Chiplet落地進展和重點企業(yè)布局

評論