簡介

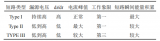

本文匯集了 SiC MOSFET 最新結果的特定方面,涉及由于應用交流柵極偏置應力(也稱為柵極開關應力)導致的閾值電壓 (VT) 退化及其影響溝槽幾何器件對負偏壓過應力 (NBO) 效應的強烈依賴。交流柵極偏置應力引起的退化是 SiC MOSFET VT 不穩定性的一個潛在重要方面,最近才被揭示。我們最近的工作表明,這種現象包括看似永久性的 VT 偏移和觀察到的 VT 滯后的增加。它還表明,這種退化效應與柵極開關周期的數量成正比,在開關周期期間從積累到強反轉再返回的更快轉換會導致每個周期更大的退化,并且這種退化可以在 300 ℃ 時退火。最后,當暴露于超過器件負偏壓額定值的 NBO 時,這種退化效應主要出現在溝槽幾何器件中。我們還發現,并非所有溝槽器件都同樣容易受到影響,這表明器件設計和加工細節對于這種影響的嚴重程度至關重要。由于研究的平面器件和應用的開關周期數量相對較少,早期研究雙極交流應力的工作未能發現任何有意義的東西。

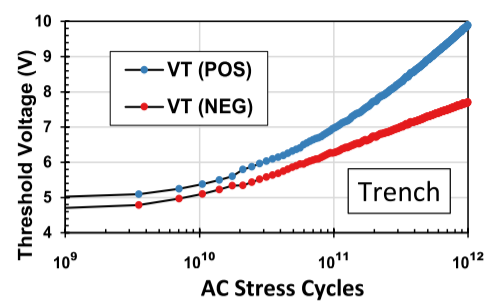

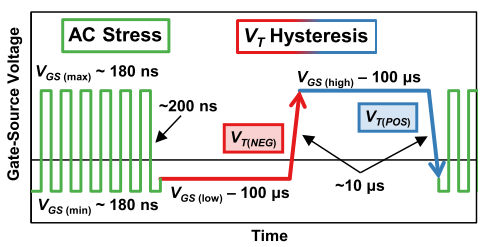

圖 1 說明了在某些溝槽幾何器件中觀察到的基本退化效應,顯示了 VT 磁滯測量序列的低側和高側變化圖,其中應用了第一個柵極偏置極性,并且測量 VT(通過在大約 10 μs 完成快速 I-V 測量后以固定電流水平提取 VGS),然后應用另一個極性并重新測量 VT,揭示存在的 VT 遲滯——作為總電壓的函數應用交流應力循環(均在室溫下)。在每個柵極極性下,測量 VT 磁滯的應力時間為 100 μs,這與 AC 應力本身施加的 200 ns 有效應力時間形成對比(參見圖 2 中所示的應力和測量示意圖)。觀察到的 VT 不穩定性變化非常顯著,在 1012 個總 AC 應力循環后,VT 磁滯從最初的 0.25 V 增加到約 2.25 V,VT 磁滯的低側增加約 3 V,從 4.7 V 增加到 7.7 V,高側增加約 5V,從約 5V 到 10V。還值得注意的是,觀察到的 VT 遲滯的增加僅在 VT 首次發生顯著變化后發生。這一點在下面的兩張圖中表現得更清楚。

圖 1. VT 磁滯測量的高側 [VT(POS)] 和低側 [VT(NEG)] 作為溝槽 SiC MOSFET 中交流應力循環(室溫)的函數(使用快速 I-V 進行測量) 。

圖 2. 示意圖顯示了交流應力循環和 VT 磁滯測量(在恢復應力之前僅描述了一次完整迭代)——全部在室溫下進行。

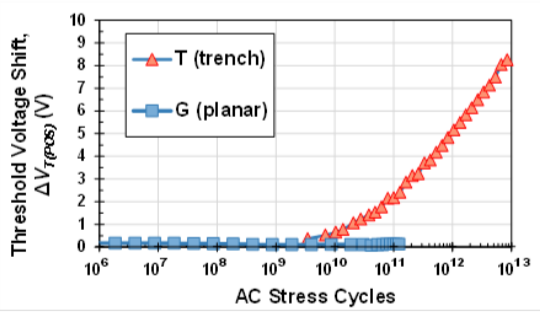

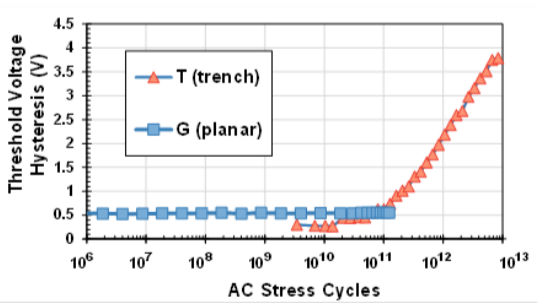

圖 3 將溝槽 SiC MOSFET 器件看似永久的 VT 偏移與平面 SiC MOSFET(來自同一制造商)中觀察到的沒有任何影響的情況進行了比較。溝槽器件的 VT 開始在 109 到 1010 個總交流應力周期之間發生明顯變化,在 1012 個總交流應力周期后變化了約 5V,在約 1013 個總應力周期后變化了超過 8V,沒有飽和的跡象!圖 4 顯示,最初,平面器件(不會退化)的 VT 磁滯是溝槽器件的兩倍,但超過大約 1011 個總 AC 應力循環后,溝槽器件的 VT 磁滯顯著增加(大約VT 已移動約 2 V 的時間)。由于下面將詳細討論的原因,這并不代表額外電荷陷阱的激活。相反,我們發現后一種效應是由于當 VGS - VT 正移幾伏時 VT 磁滯測量的低側顯著下降所致。還應該注意的是,大約 1 s 的慢速 I-V 測量顯示的 VT 偏移與快速 I-V 測量一樣多,如果 VT 偏移是由于某種永久電荷捕獲效應(永久電荷捕獲效應)造成的,則這是可以預料到的,至少在負偏壓下高溫退火之前)。另一方面,緩慢的 I-V 測量顯示出更小的 VT 磁滯效應(以及 VT 磁滯的變化),這也是可以預料的,因為 VT 磁滯是由動態、短暫的電荷俘獲引起的,其大小為測量速度依賴。

圖 3. 溝槽和平面 SiC MOSFET(來自同一制造商)的 VT 偏移與 AC 應力循環總數的比較。

圖 4. 溝槽和平面 SiC MOSFET(來自同一制造商)的 VT 磁滯與 AC 應力周期總數的比較。

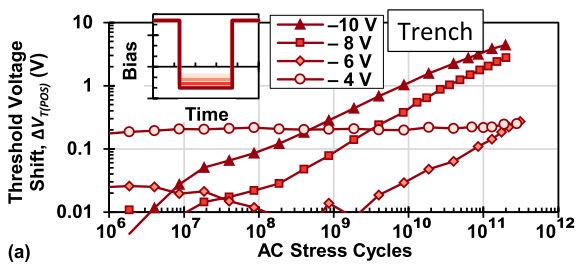

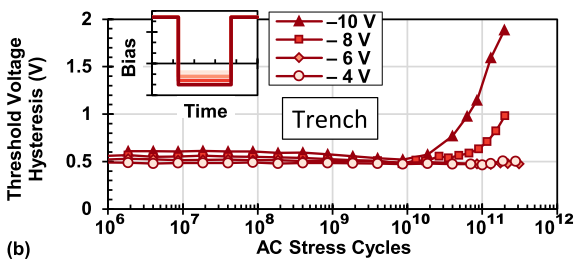

圖 5 顯示了 VT 偏移與交流應力周期總數的相關性,作為交流應力期間施加的低側柵極偏置 [VGS (min) - 見圖 2] 的函數。柵極偏壓越負,退化效應越強。 (對于圖 1、3 和 4 所示的結果,VGS (min) 為 -10 V。)計算 VT 偏移的參考點是 VT 磁滯測量值 [VT(POS)] 的高側。圖 6 顯示了低側柵極偏置與 VT 磁滯相應增加的關系。再次清楚的是,VT 遲滯的增加直到 VT 偏移超過至少 1 V 才開始,并且直到大約 2 V 偏移才顯著。

圖 5. 交流應力的低側柵極偏壓 VGS(最小值)對觀察到的 VT 偏移(在 VT 磁滯包絡的高側測量)的影響,作為總應力周期的函數。 VGS(最大值)= +22 V。

圖 6. 交流應力的低側柵極偏壓 VGS(最小值)對觀察到的 VT 磁滯(使用 +22 V / –4 V 測量)的影響,作為總應力周期的函數。 VGS(最大值)= +22 V。

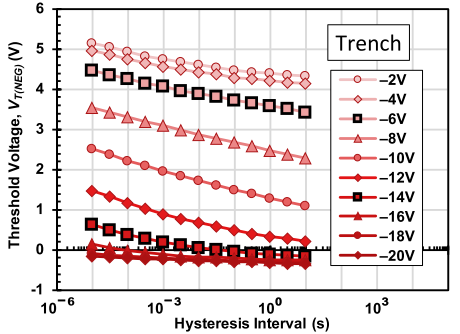

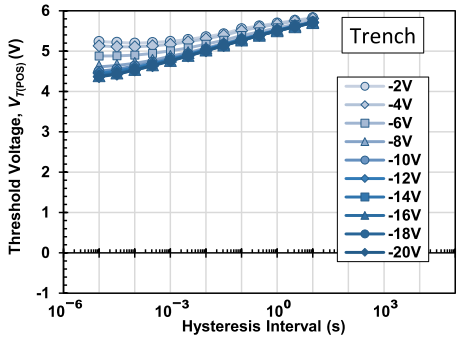

為了更好地理解 VT 偏移和由于 AC 應力引起的退化而引起的 VT 磁滯變化之間的關系,特別是在溝槽幾何器件中,查看 VT 磁滯對施加在低側的柵極偏壓的敏感度 [VGS] 具有指導意義。在沒有交流應力的情況下進行 VT 磁滯應力和測量序列(加工后的器件)。圖 7 顯示了 VT 磁滯幅度如何隨著負柵極偏壓的增加(同時將高側 [VGS(高)] 保持在 +22 V)而增加(相對于 VT 磁滯應力間隔時間繪制)。從 VGS(低)= –6V(以粗體突出顯示)開始,VT 遲滯幅度顯著增加,并且 VGS(低)每增加 2V,VT 遲滯幅度繼續增加約 1V,直到 VGS(低)= –14 V(也以粗體突出顯示),此后效果很快開始最終飽和(毫不奇怪,制造商為該器件指定的最大負柵極偏壓為 –4 V)。相比之下,同一制造商的平面幾何器件在相同的負柵極偏壓范圍內,VT 遲滯幾乎沒有增加。柵極偏置值(見圖 8)。對于平面器件,影響很小,并且在 VGS(低)= –6 V 附近開始飽和。(應該注意的是,如圖 7 所示,溝槽器件中對 NBO 的大靈敏度對于兩者來說是相同的)主要制造商進行了評估,盡管在 NBO 條件下 [見圖 5],交流應力造成的顯著退化僅對兩家制造商之一而言是真實的。

圖 9 和圖 10 提供了對溝槽幾何器件中 VT 磁滯大幅增加的驅動因素的進一步了解(如圖 7 所示)。圖 9 顯示了 VT 磁滯包絡線 [VT(NEG)] 的低側如何隨著 VT 磁滯應力 [VGS(低)] 期間負柵極偏壓的增加而沿負方向顯著向下移動 — 再次繪制與 VT 磁滯應力的關系圖間隔時間(見圖2)。另一方面,圖 10 顯示,隨著 VT 磁滯應力期間負柵極偏壓的增加,同一 VT 磁滯包絡 [VT(POS)] 的高側僅在負方向上稍微向下移動。 (在別處研究了在 VT 磁滯應力 [VGS(高)] 期間改變正柵極偏壓的情況。)因此,圖 7 中所示的 VT 磁滯幅度的大幅增加幾乎完全是由于隨著 NBO 的增加,VT 位于 VT 遲滯包絡線的低側。

? ?

? ?

圖 9. 溝槽 SiC MOSFET 的負偏壓過應力會導致 VT 磁滯包絡線 [VT(NEG)] 的低側出現顯著的負漂移。這種效應在閾值電壓稍為負時飽和。 VGS(高)保持恒定在 +22 V。(未施加交流應力。)

圖 10. 溝槽 SiC MOSFET 的相同負偏壓過應力僅導致 VT 磁滯包絡線 [VT(POS)] 的高側產生較小的負漂移。 VGS(高)保持恒定在 +22 V。(未施加交流應力。)

這意味著,當 VT 由于交流應力退化效應而正向移動時,VGS – VT 將相應減小,從而導致 VT 遲滯測量期間應用的有效柵極偏置值發生變化。例如,在任何正 VT 偏移之前,應用 VGS(低)= ?4 V 不會導致 NBO 條件。但 VT 的 2V 正移將導致 VGS - VT 發生變化,從而使 VGS(低)實際上變為 -6V,從而增加 VT 遲滯。這導致 VT (NEG) 值變得比原本應有的正值小 1 V。這解釋了為什么圖 1 中 VT 磁滯隨著正方向偏移而變寬,以及為什么 VT 偏移首先發生,只有當 VT 首先偏移至少 1 V 時,VT 磁滯才會開始增加。因此,不需要額外的陷阱激活來解釋溝槽器件中交流應力引起的 VT 滯后的增加。

總結和結論

當暴露于具有負偏壓過應力的雙極交流應力(柵極偏壓超過制造商建議的最大負柵極工作電壓,在感興趣的特定情況下為 -4 V)時,來自特定制造商的溝槽器件會經歷較大的在大約 1013 個總周期后,正 VT 偏移接近 10 V,沒有任何飽和跡象,而來自同一制造商的平面器件(以及來自其他制造商的所有器件)顯示出的影響要小得多。觀察到的 VT 磁滯相應大幅增加并不是由于新陷阱的激活,而是由于標準 VT 磁滯測量負偏壓側 VGS-VT 的增加(在平面器件中未觀察到)。一般來說,SiC 溝槽 MOSFET 在 VT 磁滯方面表現出對 NBO 的敏感性,但僅這種現象不足以引起交流應力引起的漂移。退化機制可能是由于深態中的電子俘獲所致,導致 VT 看似永久的正移。然而,這種損壞可以通過在高溫 (300 °C) 下施加負偏壓來消除。

審核編輯:湯梓紅

-

MOSFET

+關注

關注

146文章

7101瀏覽量

212777 -

半導體

+關注

關注

334文章

27063瀏覽量

216502 -

SiC

+關注

關注

29文章

2771瀏覽量

62468

原文標題:SiC MOSFET 中的交流應力退化

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為何使用 SiC MOSFET

SiC-MOSFET的應用實例

SiC-MOSFET與Si-MOSFET的區別

SiC-MOSFET的可靠性

溝槽結構SiC-MOSFET與實際產品

SiC-MOSFET有什么優點

SiC功率器件SiC-MOSFET的特點

淺析SiC-MOSFET

SiC-MOSFET器件結構和特征

SiC MOSFET的器件演變與技術優勢

SiC MOSFET體二極管雙極性退化問題

SIC MOSFET在電路中的作用是什么?

SiC MOSFET短路失效的兩種典型現象

SiC MOSFET中的交流應力退化

SiC MOSFET中的交流應力退化

評論