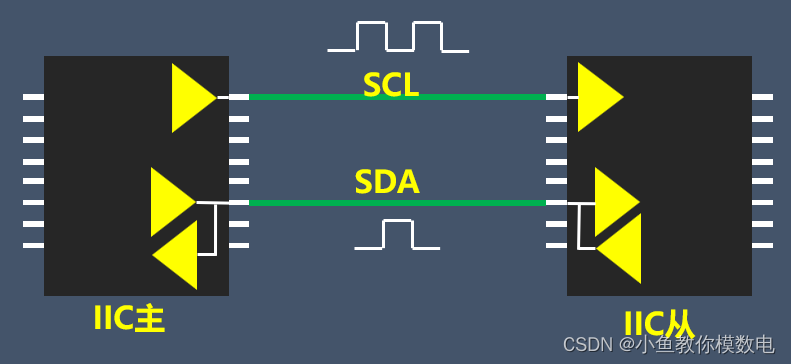

IIC 是一個兩線串行通信總線,包含一個 SCL 信號和 SDA 信號,SCL 是時鐘信號,從主設備發出,SDA 是數據信號,是一個雙向的,設備發送數據和接收數據都是通過 SDA 信號。

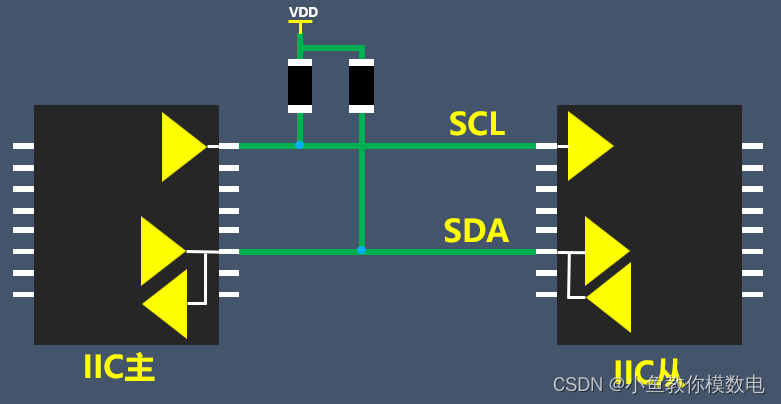

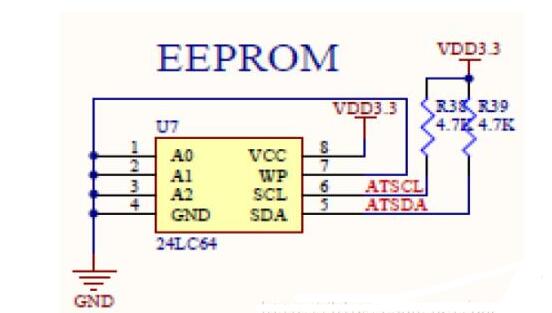

在設計 IIC 信號電路的時候我們會在 SCL 和 SDA 上加一個上拉電阻。

今天就來分享下,為什么要在 IIC 信號線上加上拉電阻。

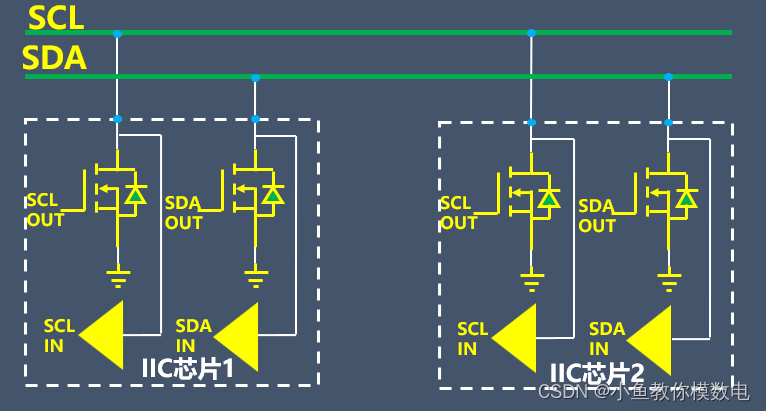

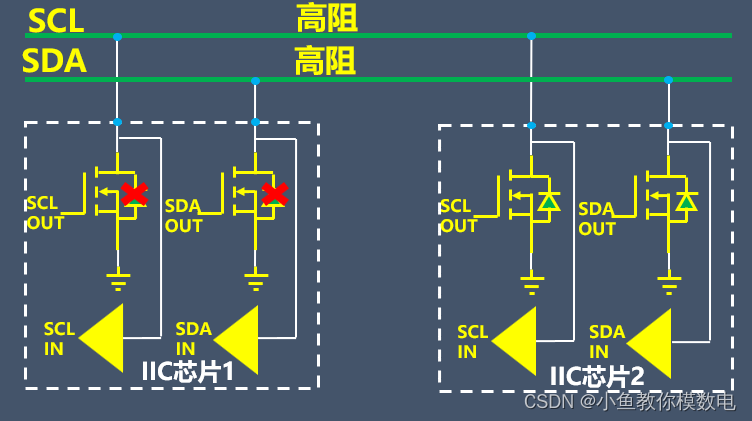

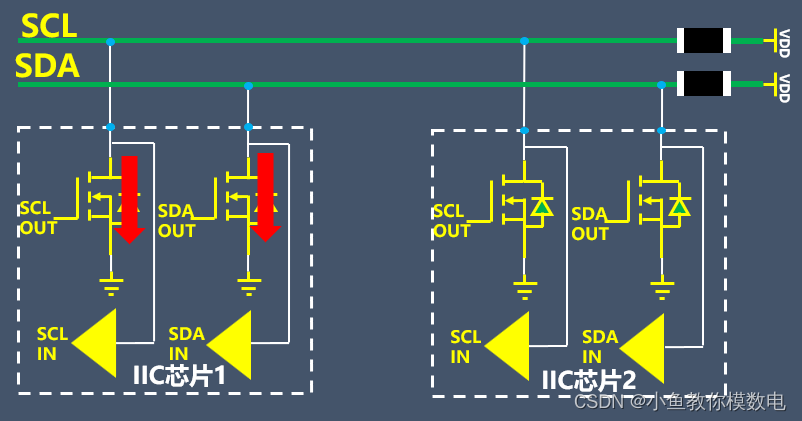

主要原因就是 IIC 芯片的 SDA 和 SCL 的引腳是開漏輸出,就是只有一個 NMOS 管,不像推挽輸出有兩個 MOS 管。

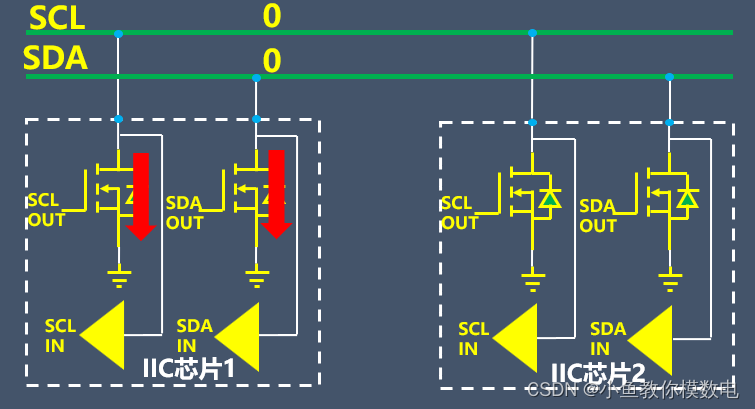

當芯片 SDA 和 SCL 的引腳輸出 MOS 管導通,IIC 信號線電平為低電平。

當芯片 SDA 和 SCL 的引腳輸出 MOS 管關閉,如果沒有上拉電阻,IIC 信號線是處于一個高阻狀態,電平是未知的,開漏輸出是沒有高電平的輸出能力的。

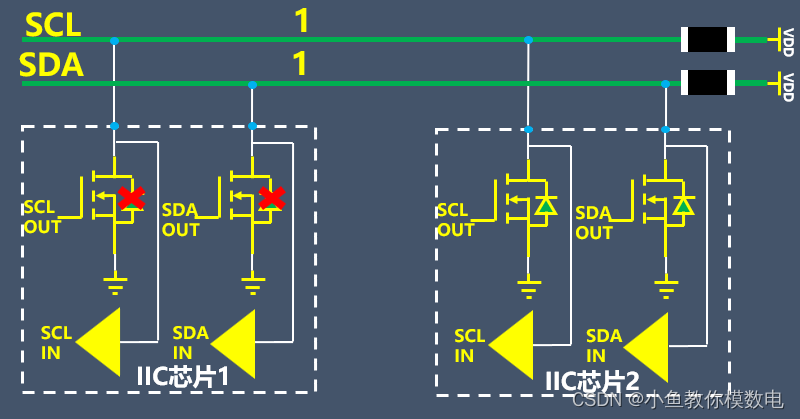

所以加上上拉電阻后,當芯片 SDA 和 SCL 的引腳輸出 MOS 管關閉,IIC 信號線上的電平就是一個確切的高電平。

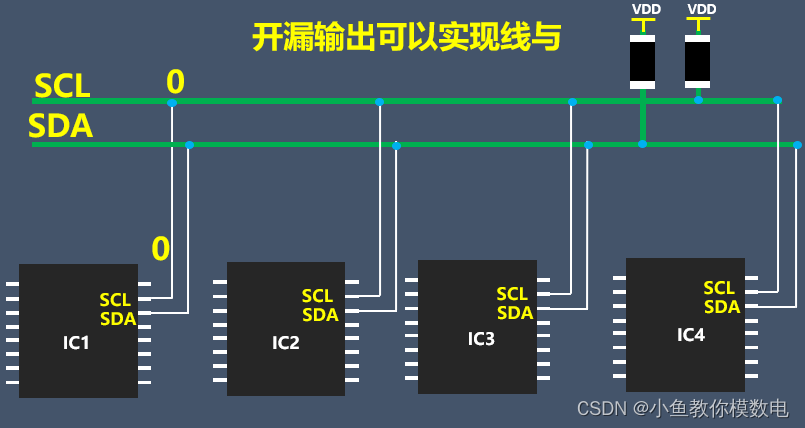

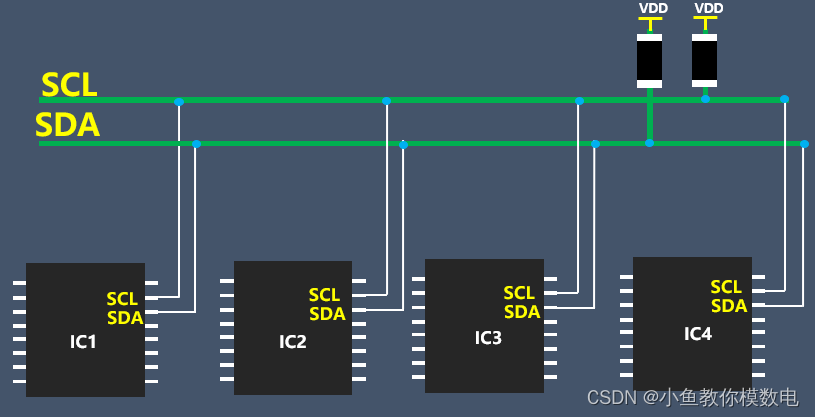

當多個 IIC 設備通過 IIC 總線接在一起,這就要求 IIC 設備間可以實現線與,而芯片的 IIC 引腳是開漏輸出的話就能很好的實現這個線與。只要有一個 IIC 設備的引腳電平是低電平,那么相應的 SCL 或 SDA 總線也會成為一個低電平。如果 IIC 設備引腳為推挽輸出,多個 IIC 設備接在一條總線上很容易燒壞芯片。

IIC 上拉電阻的取值

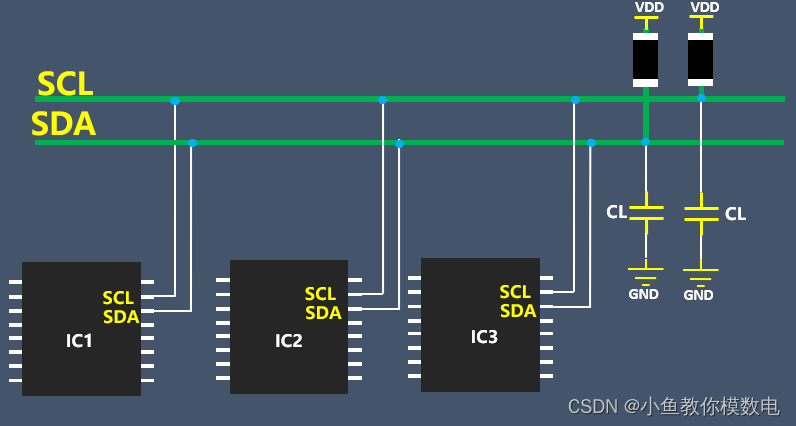

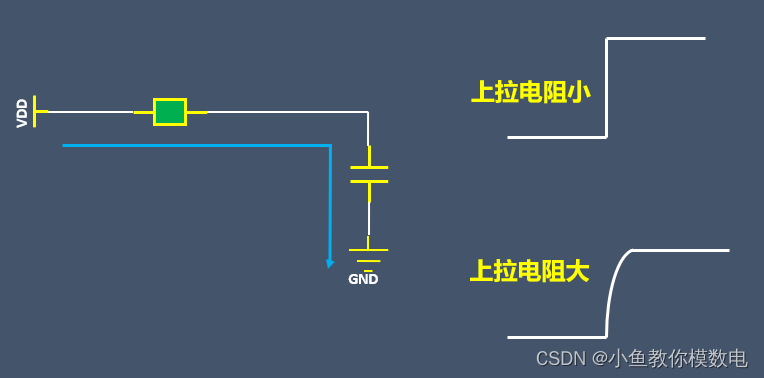

IIC 信號的上拉電阻阻值不能太大,因為 IIC 芯片 SCL 和 SDA 引腳都存在寄生電容,同時 SDA 和 SCL 信號的走線也會有寄生電容,整個 IIC 總線上相當于接了一個負載電容 Cl

上拉電阻過大,IIC 總線高電平的驅動能力差,總線電平從 0 到 1 變化時,等效為這個 RC 的充電電路,上拉電阻越大,波形上升沿會變緩,一定程度會影響 IIC 的時序,可能會出現誤碼。所以這個上拉電阻不能太大。

IIC SDA 和 SCL 信號的上升時間和總線電容在不同的模式下有不同的要求,大家可以看下這個表。

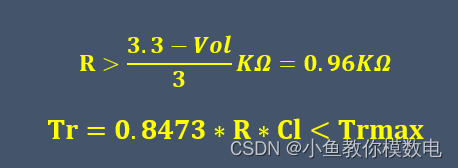

IIC 總線信號上升時間可以根據公式 Tr=0.8473*R*Cl Cl 就是 IIC 總線的等效負載電容

IIC 信號上拉電阻也不能太小,如果太小了,當 IIC 引腳輸出低電平時,灌進芯片 IIC 引腳的電流會變大,可能會使 IIC 信號線的低電平變大,同時 IO 口電流過大還可能燒壞芯片。

我們一般要求,IIC 引腳低電平時,流過芯片 IIC 引腳的電流小于 3mA,所以如果是 3.3V 上拉的話,這個電阻就要 R>(3.3-VoL)l3KΩ=0.96KΩ ,其中 VoL 是 IIC 引腳為低電平時的最大電壓,一般是 0.4V。再加上前面的這個公式我們就可以確定這個上拉電阻的取值范圍。

電源電壓決定上拉電阻的最小值,總線負載電容決定上拉電阻的最大值。

IIC 信號上拉電阻取值常用的值就是 4.7K,一般小于 10K,大于 1K,如果 IIC 總線比較長,從設備比較多,可以適當降低電阻。

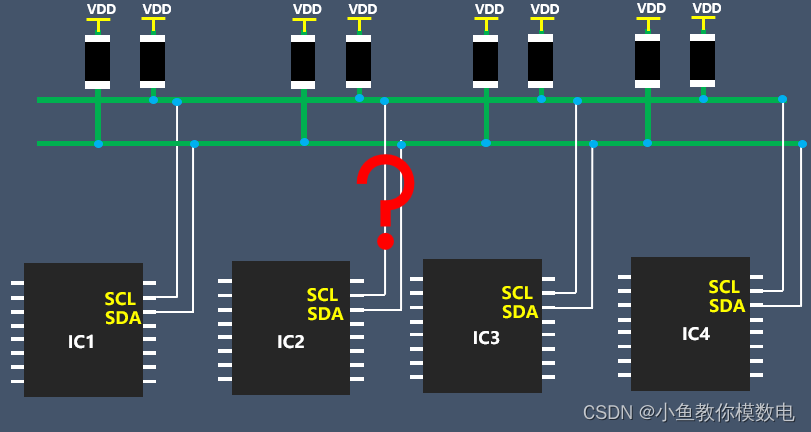

如果 IIC 總線接了很多 IIC 設備,是不是每個 IIC 設備都要加上拉電阻?

答案是否定的,我們只要在 SDA 和 SCL 總線上合適的位置各加一個上拉電阻即可,如果每個設備都加上拉,相當于這些電阻是并聯在一起了,減小了電阻值。至于上拉電阻的位置一般沒有特別的要求。一般加在 IIC 的末端。

審核編輯:湯梓紅

-

上拉電阻

+關注

關注

5文章

359瀏覽量

30574 -

總線

+關注

關注

10文章

2869瀏覽量

87995 -

IIC

+關注

關注

11文章

300瀏覽量

38277 -

信號線

+關注

關注

2文章

168瀏覽量

21424 -

SCL

+關注

關注

1文章

239瀏覽量

17040

原文標題:講解 I2C 信號線為何加上拉電阻(圖文并茂)

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SD卡的時鐘線為什么可以不加上拉電阻呢?是因為時鐘永遠是輸出信號嗎?為什么輸出信號就可以不加上拉電阻

為什么要在51單片機外部接上拉電阻呢

集電極加上拉電阻的作用

什么是上拉電阻?如何計算I2C上拉電阻的大小值

為什么要在IIC信號線上加上拉電阻

為什么要在IIC信號線上加上拉電阻

評論