點(diǎn)擊藍(lán)字關(guān)注我們

過去,仿真的基礎(chǔ)是行為和具有基本結(jié)構(gòu)的模型。這些模型使用的公式我們在學(xué)校都學(xué)過,它們主要適用于簡單集成電路技術(shù)中使用的器件。但是,當(dāng)涉及到功率器件時,這些簡單的模型通常無法預(yù)測與為優(yōu)化器件所做的改變相關(guān)的現(xiàn)象。當(dāng)今大多數(shù)功率器件不是橫向結(jié)構(gòu),而是垂直結(jié)構(gòu),它們使用多個摻雜層來處理大電場。柵極從平面型變?yōu)闇喜坌停肓烁鼜?fù)雜的結(jié)構(gòu),如超級結(jié),并極大地改變了MOSFET的行為。基本Spice模型中提供的簡單器件結(jié)構(gòu)沒有考慮所有這些非線性因素。

現(xiàn)在,通過引入物理和可擴(kuò)展建模技術(shù),安森美(onsemi)使仿真精度進(jìn)一步提升到更高的水平,本文將主要介紹物理和可擴(kuò)展仿真模型功能的相關(guān)內(nèi)容。

原版文檔獲取點(diǎn)擊文末的“贊”和“在看”,并發(fā)送截圖和您的郵箱地址到后臺,即可領(lǐng)取英文原版文檔哦~

這種基于物理公式、工藝參數(shù)和布局參數(shù)的建模技術(shù)考慮了我們的產(chǎn)品為現(xiàn)代功率開關(guān)器件所引入的所有非線性。物理公式可以捕獲現(xiàn)代功率器件在所有不同區(qū)域中的溫度依賴性和傳播效應(yīng)。針對專用技術(shù)(SiC MOSFET M3和IGBT FS4等)創(chuàng)建了一個核心模型——通過布局參數(shù)設(shè)置芯片尺寸,以獲取特定的器件。

物理和可擴(kuò)展仿真模型所包含的值遠(yuǎn)不止通過數(shù)據(jù)手冊參數(shù)或在幾乎理想的測量環(huán)境中獲得的數(shù)據(jù)手冊值。該模型可在規(guī)格限值內(nèi)仿真所有條件下的所有值。在物理和可擴(kuò)展仿真模型中還可以捕獲數(shù)據(jù)手冊中未提供的參數(shù)或曲線——可通過仿真獲取。大多數(shù)時候,只需運(yùn)行一個簡單的仿真原理圖。

為舉例說明物理和可擴(kuò)展模型的強(qiáng)大功能,我們將比較通過仿真兩個超級結(jié) MOSFET 模型(一個行為模型和一個物理和可擴(kuò)展模型)獲得的輸出電容結(jié)果。這兩個超級結(jié)MOSFET性能相近(650V,導(dǎo)通電阻約為18mΩ)。首先,我們將仿真結(jié)果與測量數(shù)據(jù)疊加。

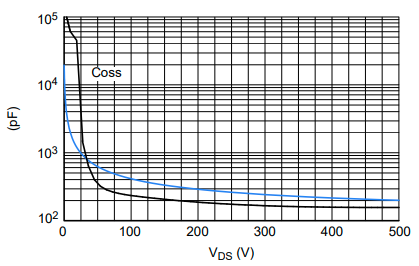

圖1. 行為模型輸出電容仿真結(jié)果

在上圖和下圖(分別為圖1和圖2)中,彩色曲線是通過仿真獲得的,而疊加的黑色曲線是基于器件規(guī)格的曲線。圖1來自競爭對手的模型,因?yàn)樗邪采莱壗Y(jié)MOSFET模型都不是行為模型,而是物理和可擴(kuò)展模型。行為模型無法捕捉到輸出電容近103的下降,這是所有超級結(jié)MOSFET固有的特性。

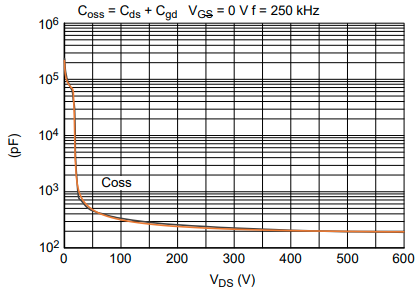

圖2. 物理和可擴(kuò)展模型輸出電容仿真結(jié)果

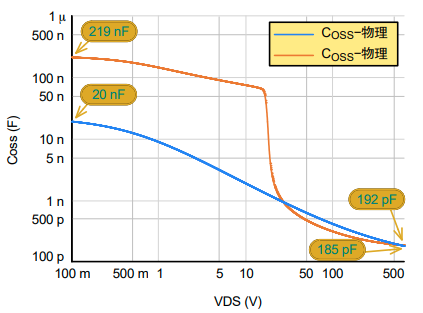

接下來,為了比較用于獲得圖 1 和圖 2 的相同硅超級結(jié) MOSFET 模型,我們這次使用相同的對數(shù)刻度繪制了輸出電容(或COSS)。該刻度放大了差異,但有助于我們讀取兩種器件在最小阻斷電壓下的最大電容值和最大阻斷電壓下的最小電容值的仿真結(jié)果,如圖 3 所示。

圖3. 行為模型與物理和可擴(kuò)展性模型的輸出電容仿真結(jié)果比較

假設(shè)我們想要使用半橋或全橋結(jié)構(gòu)來仿真軟轉(zhuǎn)換或零電壓開關(guān)應(yīng)用。在轉(zhuǎn)換期間,我們認(rèn)為電感電流恒定,這意味著電感足夠大。

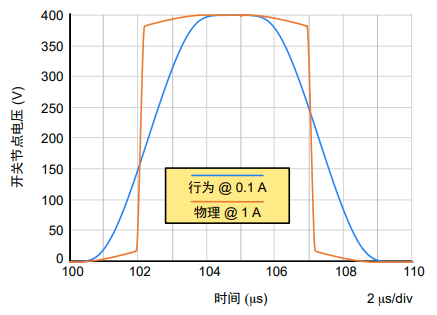

圖4. 行為模型與物理和可擴(kuò)展性模型的輸出電容仿真結(jié)果比較

我們試圖獲得幾乎相同的轉(zhuǎn)換時間(圖4)。由于低電壓下電容值具有十倍數(shù)差異(參見圖3),因此為輸出電容充電和獲得軟轉(zhuǎn)換所需的電流值也有十倍數(shù)差異。

如圖2所示,安森美物理和可擴(kuò)展仿真模型給出的輸出電容值(或COSS)是準(zhǔn)確且真實(shí)的。這意味著使用圖4中的安森美物理和可擴(kuò)展仿真模型仿真得到軟轉(zhuǎn)換所需的電流也是有效的。

使用行為仿真模型,您會將諧振轉(zhuǎn)換所需的能量低估 10 倍——該誤差或錯誤可能導(dǎo)致需要全部重新設(shè)計(jì)應(yīng)用的諧振回路和系統(tǒng)。

現(xiàn)在,您可以使用安森美物理和可擴(kuò)展仿真模型,以出色的精度仿真零電壓開關(guān)轉(zhuǎn)換。您將獲得轉(zhuǎn)換所需的實(shí)際能量,因?yàn)榉抡婺P筒东@了COSS在超過103倍變化率范圍的所有電容非線性。

物理和可擴(kuò)展仿真模型功能

使用SIMetrix獲取內(nèi)部節(jié)點(diǎn)電壓

鍵合和封裝位于芯片和電、熱接觸點(diǎn)之間。組裝通過寄生串聯(lián)電感和電阻或電阻抗和熱阻抗影響芯片性能。封裝引腳加上鍵合和金屬掩模可增加高達(dá)10mΩ的串聯(lián)電阻。

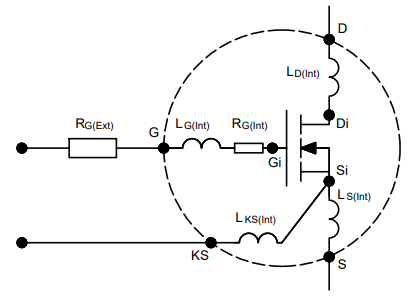

為了量化這些影響,可以訪問三引腳MOSFET的內(nèi)部節(jié)點(diǎn),如柵極、漏極和源極(參見圖5)。

圖5. 內(nèi)部節(jié)點(diǎn)與外部節(jié)點(diǎn)

在極高速開關(guān)中,柵極是硬開關(guān)和軟開關(guān)中最關(guān)鍵的信號。掌握MOSFET何時真正導(dǎo)通和關(guān)斷非常有必要。例如,它可以幫助設(shè)計(jì)人員在半橋結(jié)構(gòu)中設(shè)置高壓側(cè)和低壓側(cè)開關(guān)之間的延遲。

要訪問內(nèi)部節(jié)點(diǎn),請查找器件和可用引腳名稱。引腳標(biāo)記末尾帶有“i”,表示“內(nèi)部”。

在SIMetrix中,只需在仿真選項(xiàng)控制面板中選擇此功能,即可獲得內(nèi)部節(jié)點(diǎn)電壓。然后,名稱看上去類似“Qndi”(例如)為內(nèi)部漏極節(jié)點(diǎn)電壓。它直接是芯片級的電壓。我們現(xiàn)在可以測量施加到芯片上的實(shí)際漏極-源極電壓,不存在任何可能增加或減少振鈴的寄生效應(yīng)。

我們采用由SiC MOSFET NTHL015N065SC1構(gòu)成的一個半橋架構(gòu),改變外部柵極電阻,并比較芯片級和封裝級之間的漏極-源極電壓差。該器件采用TO247三引腳封裝。

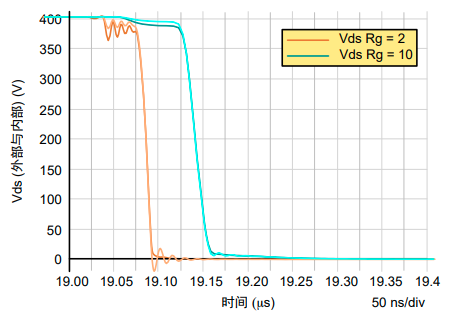

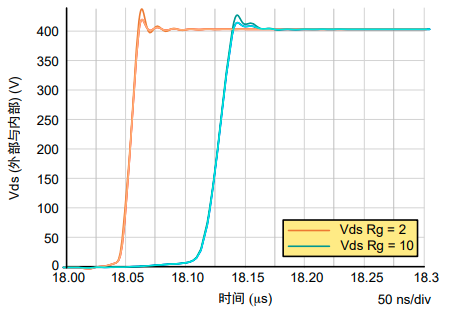

在下圖中,我們可以比較導(dǎo)通和關(guān)斷時的漏極-源極波形。導(dǎo)通時,振鈴較低,而關(guān)斷時則相反(見圖6和圖7)。

淺色曲線是芯片漏極-芯片源極電壓,深色曲線是封裝漏極-封裝源極引腳電壓。

圖6. 導(dǎo)通時內(nèi)部和外部漏極-源極電壓的差異

圖7. 關(guān)斷時內(nèi)部和外部漏極-源極電壓的差異

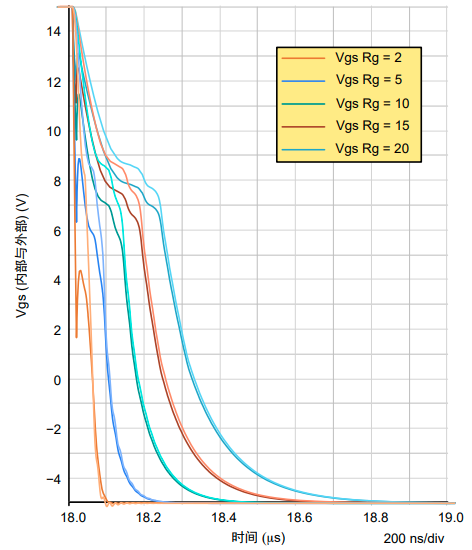

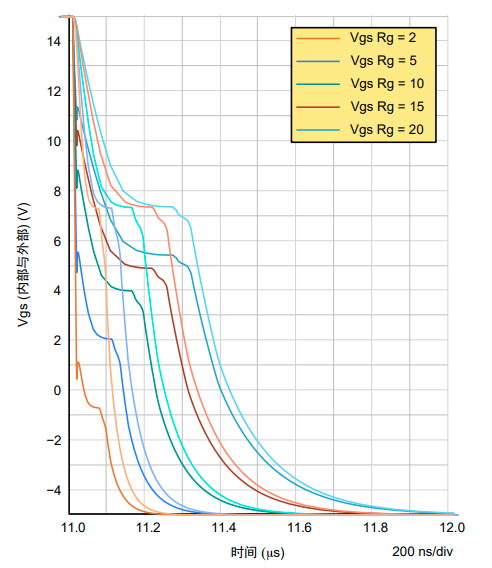

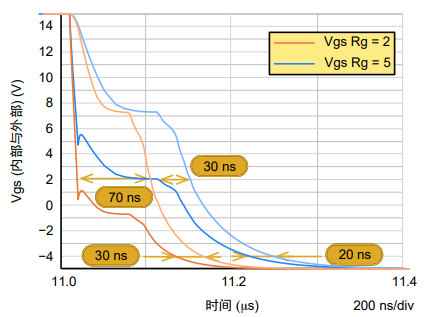

如前所述,獲取實(shí)際的芯片柵極信號有助于提供相關(guān)信息。我們采用一個由 SiC MOSFET NTH4L015N065SC1 構(gòu)成的半橋架構(gòu),改變外部柵極電阻,并比較芯片級和封裝級之間的柵極-源極電壓差(參見圖8和9)。

圖8. 內(nèi)部和外部柵極-源極電壓的差異及其與外部柵極電阻的函數(shù)關(guān)系

淺色曲線是芯片柵極電壓,而深色曲線是封裝柵極引腳電壓。

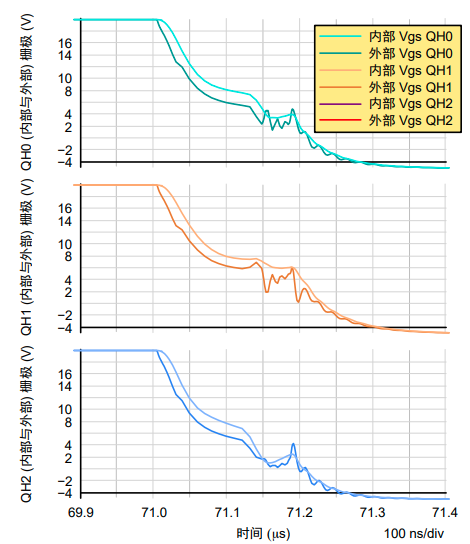

我們來逐步查看當(dāng)柵極電阻改變時會發(fā)生什么。當(dāng)電阻大于10Ω時,外部和內(nèi)部柵極電壓幾乎同時超出閾值(即,對于安森美SiC MOSFET為2V)。存在一個10ns以內(nèi)的延遲。

當(dāng)電阻小于等于5Ω時,我們可以看到,在關(guān)斷期間,只有外部柵極電壓會出現(xiàn)電壓尖峰和越來越多的振蕩,而內(nèi)部柵極電壓相對平滑。

當(dāng)電阻為5Ω或2Ω時,在閾值交叉處可以明顯看到兩個電壓(外部和內(nèi)部)之間存在相當(dāng)大的延遲(約為40ns)。

對于5Ω,外部電壓給出的關(guān)斷時間約為80ns,而內(nèi)部關(guān)斷時間約為120ns,因此延長了50%。對于2Ω,情況則更糟。外部電壓給出的關(guān)斷時間約為40ns,而內(nèi)部關(guān)斷時間為80ns,因此關(guān)斷時間延長了100%。

具體取決于外部和內(nèi)部柵極阻抗之比。在上述圖8示例中,內(nèi)部柵極阻抗略低于1Ω。

在圖9中,我們通過改變芯片設(shè)計(jì)和柵極流道,將內(nèi)部柵極阻抗提高到接近5Ω,但是對于相同的封裝,我們通常會看到一個更長的關(guān)斷時間,與預(yù)期相同。同時,柵極網(wǎng)絡(luò)的阻尼更大,外部柵極節(jié)點(diǎn)電壓上的振鈴更少。

圖9. 提高內(nèi)部柵極阻抗時,內(nèi)部和外部柵極-源極電壓的差異

圖9顯示當(dāng)外部柵極電阻低于10Ω時,內(nèi)部和外部柵極電壓之間的延遲較長。一些制造商使用高內(nèi)部柵極阻抗來降低最大漏極-源極dV/dt和EMI成分,并限制由柵極氧化物應(yīng)力導(dǎo)致的故障。

然而,依賴外部柵極電壓波形來設(shè)置半橋或全橋架構(gòu)中的開關(guān)之間的延遲時,也會增加擊穿的風(fēng)險(xiǎn)。

圖10. 柵極-源極電壓延遲

當(dāng)外部電阻低于10Ω時,閾值交叉時間存在很大差異,如圖10所示。甚至內(nèi)部柵極和外部柵極信號的過零和關(guān)斷閾值交叉也會發(fā)生在不同的時間。在半橋架構(gòu)的情況下,MOSFET開關(guān)相位不同或采用 架構(gòu),我們可以測量到外部柵極上得關(guān)斷延遲要比實(shí)際關(guān)斷時間低得多。因此,會導(dǎo)致另一側(cè)的MOSFET過早打開,并造成嚴(yán)重?fù)舸?/span>

架構(gòu),我們可以測量到外部柵極上得關(guān)斷延遲要比實(shí)際關(guān)斷時間低得多。因此,會導(dǎo)致另一側(cè)的MOSFET過早打開,并造成嚴(yán)重?fù)舸?/span>

同樣,獲取內(nèi)部芯片電壓對于設(shè)置適當(dāng)?shù)难舆t以避免高壓側(cè)和低壓側(cè)之間的交叉導(dǎo)通非常有幫助。

使用邊界模型

在線提供的模型使用工廠標(biāo)稱值生成和校準(zhǔn)。它們給出了典型的數(shù)據(jù)手冊值。

但是,在現(xiàn)實(shí)中,由于制造中的工藝差異,參數(shù)值遵循高斯分布。

對于特定技術(shù),可以創(chuàng)建具有最小值和最大值的模型。然后,我們可以研究不同器件的并聯(lián),或者查看器件隨極端情況數(shù)值變化的反應(yīng)。

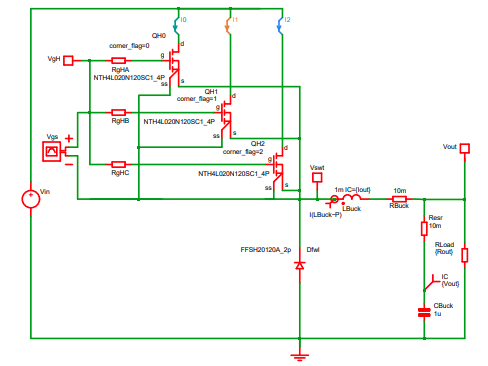

為了說明該性能,我們采用一個由三個并聯(lián)工作的 SiC MOSFET 組成的高壓降壓級電路(參見圖 11)。

圖11. 邊界模型降壓級

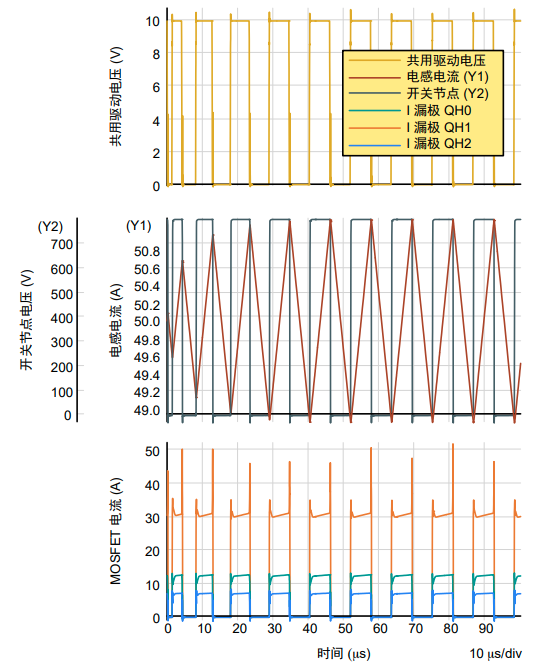

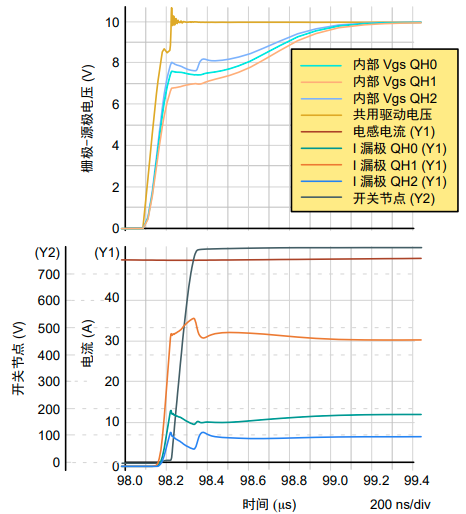

圖12. SiC MOSFET 邊界模型的降壓級波形

圖12中的結(jié)果顯示SiC MOSFET中的電流非常不均衡。在導(dǎo)通時間內(nèi),開關(guān)或SiC MOSFET中的電流分為30A、12A和7A,電感中的平均穩(wěn)態(tài)電流為50A。流過每個MOSFET的理論電流值約為17A,存在+13/-10A的誤差。因此,就電流均衡而言,QH1(最低閾值MOSFET)的誤差為+76%,QH0(平均閾值 MOSFET)的誤差為-29%,QH2(最高閾值 MOSFET)的誤差為-59%。

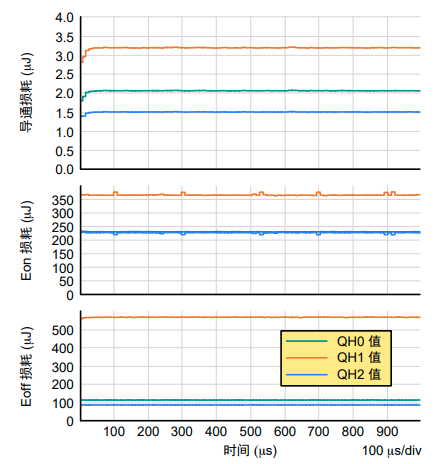

我們現(xiàn)在還可以使用圖13和圖14分析導(dǎo)通和關(guān)斷細(xì)節(jié)。

圖13. 導(dǎo)通序列局部放大

導(dǎo)通時,如圖13所示,在閾值電壓最低的SiC MOSFET中流動的電流要高得多。這個MOSFET承受大部分電感電流以及反向容性SiC肖特基二極管電流。此外,并非所有SiC MOSFET的導(dǎo)通損耗都相同。

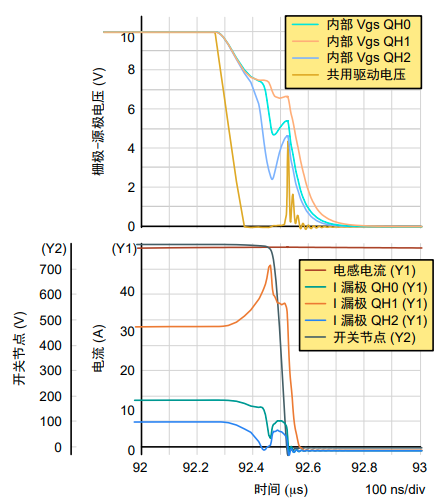

同樣,在關(guān)斷期間,幾乎所有電流都流入閾值電壓最低的SiC MOSFET(參見圖14)。

我們還可以看到,閾值電壓最高的SiC MOSFET的電流首先開始下降,然后閾值電壓居中的SiC MOSFET的電流也開始下降。但是,在兩個SiC MOSFET完全關(guān)斷之前,三柵極網(wǎng)絡(luò)中的諧振會使這兩個SiC MOSFET的導(dǎo)通變差,因?yàn)樗鼈兊恼w柵極-源極電壓會略有增加。它們在開關(guān)節(jié)點(diǎn)電壓負(fù)斜率期間再次導(dǎo)通,但僅占總電流的一小部分。

圖14. 關(guān)斷序列放大

圖15. 內(nèi)部與外部柵極-源極電壓關(guān)斷序列局部放大

同樣,如果我們對內(nèi)部和外部柵極-源極電壓之間的差異進(jìn)行分析,將獲得圖15中的結(jié)果。可以看到在外部柵極-源極電壓中存在柵極網(wǎng)絡(luò)振蕩。當(dāng)開關(guān)節(jié)點(diǎn)電壓為負(fù)斜率時,外部柵極-源極電壓也會出現(xiàn)明顯的尖峰。在圖14中,在71.2 μs處的共用驅(qū)動電壓上也可以看到這個尖峰。

我們可以對漏極-源極電壓與漏極電流的乘積進(jìn)行積分,根據(jù)積分周期(導(dǎo)通、關(guān)斷和導(dǎo)通時間)獲得開關(guān)損耗能量或?qū)〒p耗功率。我們還可以計(jì)算同一乘積在一個開關(guān)周期內(nèi)的平均值,以獲得每個SiC MOSFET的總損耗。

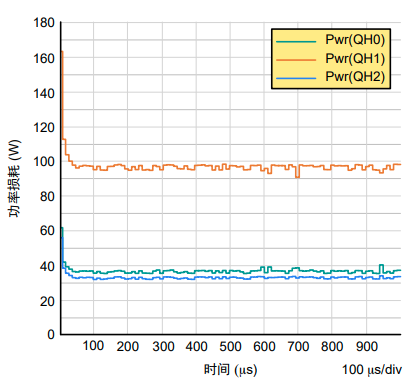

圖16. 每個SiC MOSFET的總功率損耗

正如預(yù)期和圖16所示,閾值電壓最低的Si CMOSFET的總損耗最大。

進(jìn)一步觀察可知,最低閾值SiC MOSFET的損耗略低于100W。閾值電壓居中的器件損耗介于38W和39W之間,而最高閾值SiC MOSFET損耗則為36W至37W。

當(dāng)我們使用遲滯控制或自振蕩反饋時,開關(guān)頻率不是很穩(wěn)定。這會導(dǎo)致每個周期的一些仿真和計(jì)算誤差。仿真精度和隨機(jī)變化的仿真時間步長也會引起誤差——轉(zhuǎn)化為曲線上的某些噪聲。

圖17. 每個SiC MOSFET的導(dǎo)通、關(guān)斷和導(dǎo)通損耗能量

每個開關(guān)周期內(nèi)的導(dǎo)通損耗(參見圖17)與每個SiC MOSFET中的導(dǎo)通電流保持一致。這并不令人意外。

對于導(dǎo)通能量,最低閾值SiC MOSFET的平均導(dǎo)通能量為400μJ,與其他兩個的250μJ相比,幾乎翻倍。

在閾值電壓最低的SiC MOSFET中,關(guān)斷能量要高出很多,超過550μJ。閾值電壓居中的SiC MOSFET具有120μJ的關(guān)斷能量,而閾值電壓最高的SiC MOSFET的關(guān)斷能量僅為90μJ。其中一個MOSFET與其他MOSFET的差異達(dá)到五倍。

原版文檔獲取點(diǎn)擊文末的“贊”和“在看”,并發(fā)送截圖和您的郵箱地址到后臺,即可領(lǐng)取英文原版文檔哦~

點(diǎn)個星標(biāo),茫茫人海也能一眼看到我

原文標(biāo)題:SiC仿真攻略手冊——詳解物理和可擴(kuò)展仿真模型功能!

文章出處:【微信公眾號:安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

安森美

+關(guān)注

關(guān)注

32文章

1588瀏覽量

91741

原文標(biāo)題:SiC仿真攻略手冊——詳解物理和可擴(kuò)展仿真模型功能!

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

用TINA如何搭建仿真模型?

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(四)

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(三)

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(二)

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(一)

工業(yè)元宇宙的仿真可以使用哪些模型

實(shí)時仿真板卡SimuCard*

fpga時序仿真和功能仿真的區(qū)別

使用仿真模型進(jìn)行拓?fù)浞治?/a>

使用Cauer網(wǎng)絡(luò)仿真熱行為與對開關(guān)損耗影響的評估

SiC仿真攻略手冊——詳解物理和可擴(kuò)展仿真模型功能!

SiC仿真攻略手冊——詳解物理和可擴(kuò)展仿真模型功能!

評論