文章來源:EETOP

原文作者:righto

一顆來自40年前的透明芯片究竟暗藏了哪些奧秘呢?

通過拆開老式計算機中損壞的接口芯片時發現一顆透明的芯片。雖然看上去十分魔幻,但該芯片并不是該公司的一些未來光子超級計算芯片,而是一顆來自1977年的老式芯片。

調查得出的結論是,該芯片不是硅基板,而是形成在藍寶石基底上,頂部有硅和金屬布線。因此,芯片是透明的,正如您可以從下圖中通過芯片看到的金色“X”看到的那樣。

它的功能比您想象的要平凡得多:它是軟盤控制器上的支持組件。

它位于接口總線 (HP-IB) 和Z80 處理器之間的一個不起眼的軟盤驅動器控制器 PCB 中。

藍寶石襯底硅芯片

藍寶石硅芯片(Silicon-on-sapphire,SOS)可能聽起來有些未來主義,這種方式制造的 IC 自 1963 年或更早以來就已存在。藍寶石硅 IC 的一個著名示例是研究木星及其衛星的伽利略太空探測器上使用的 RCA 1802 處理器。

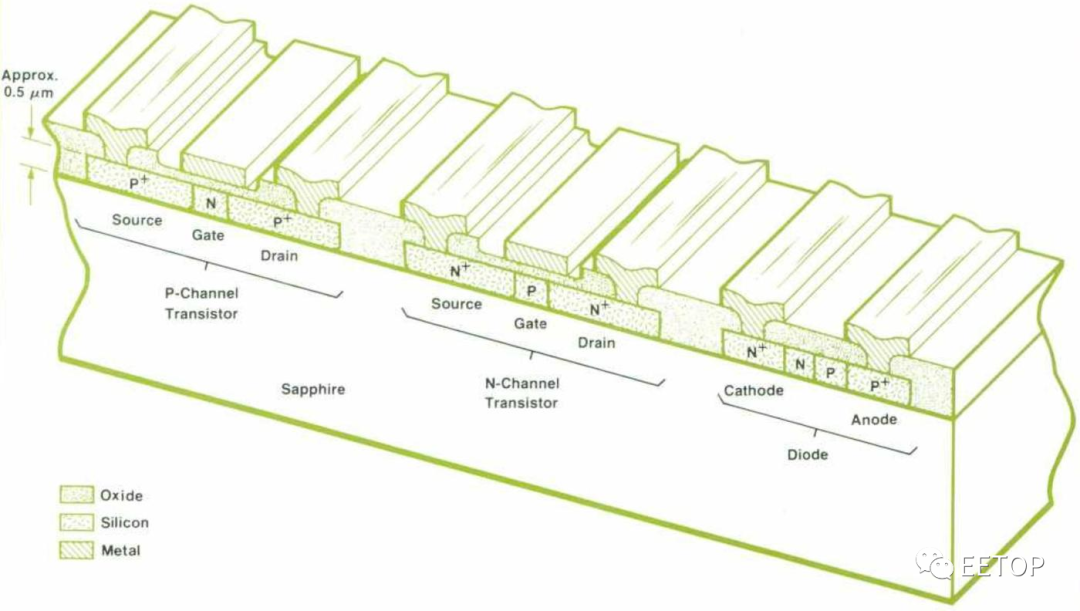

大多數集成電路形成在硅晶片上。另一方面,藍寶石基底的硅芯片則從藍寶石襯底開始。在藍寶石基板上構建一層薄薄的硅以形成電路。硅是N型的,并且在需要時通過離子注入將其轉化為P型。在頂部創建金屬布線層,形成布線以及金屬柵極晶體管。下圖顯示了電路的橫截面。

HP Journal的橫截面,1977 年 4 月

藍寶石襯底硅芯片的重要一點是硅區域彼此分離。由于藍寶石基板是絕緣體,因此與常規集成電路不同,晶體管是完全隔離的。這減少了晶體管之間的電容,從而提高了性能。絕緣還可以防止雜散電流,防止閂鎖和輻射。

PHI芯片內部

PHI 芯片使用了一種不尋常的封裝。該芯片安裝在陶瓷基板上,并由陶瓷蓋保護。該封裝有 48 個壓入插座的金手指。芯片通過兩個金屬彈簧夾固定在插座中。

PHI芯片的封裝

拆開芯片很簡單,但比預期的更戲劇化。芯片的蓋子上貼有粘合劑,可以通過加熱軟化。熱空氣不夠,所以使用了電熱板。拆解過程中,使用一把X-Acto 刀戳它來測試粘合劑,導致蓋子突然飛離,發出一聲響亮的“砰”的一聲,刀片飛到空中。很高興戴著安全眼鏡。

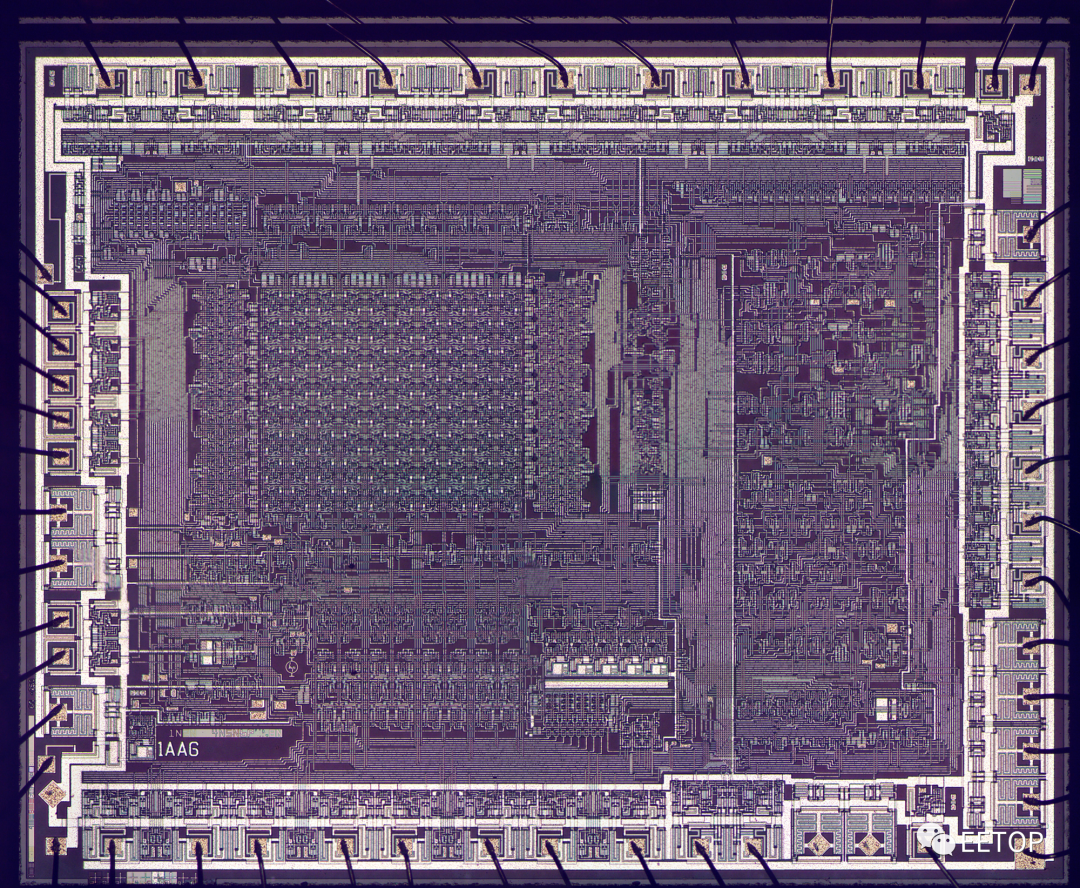

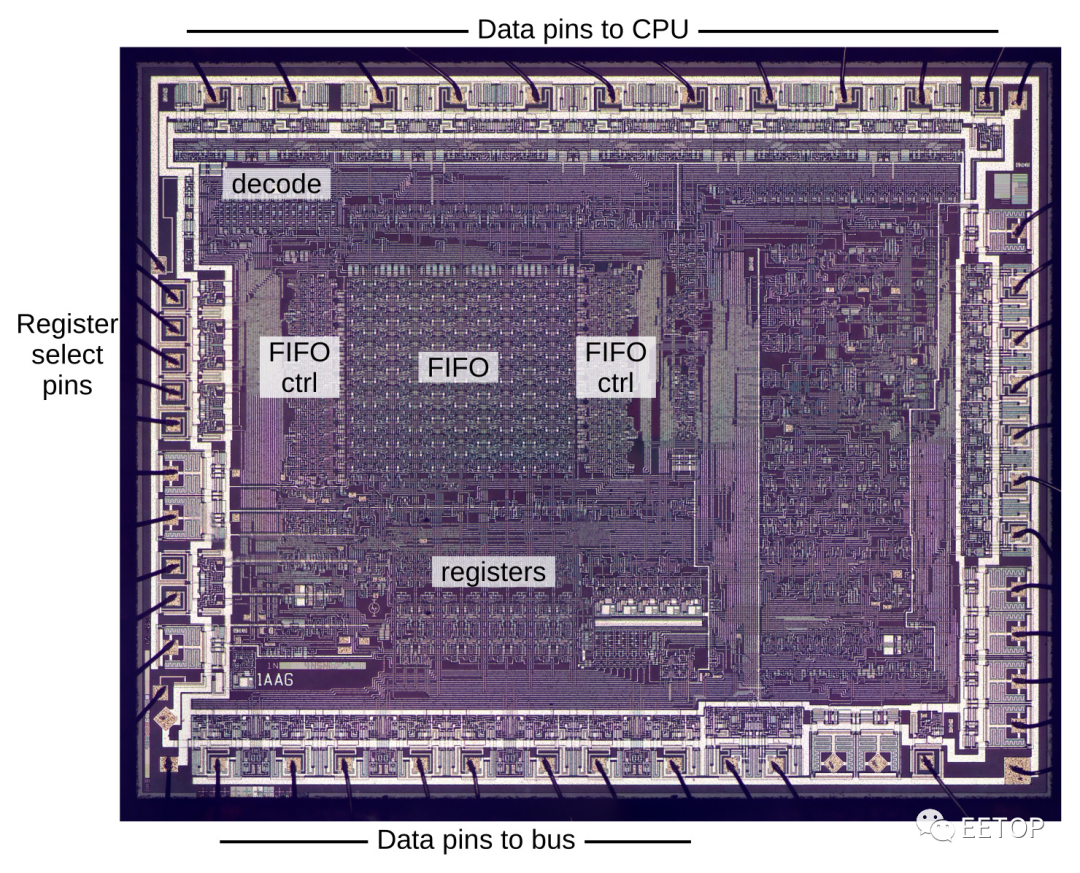

打開芯片后,創建了下面的高分辨率芯片照片。金屬層清晰可見,呈白色線條,而硅呈灰色,藍寶石呈紫色。在芯片邊緣周圍,鍵合線將芯片的 48 個外部連接連接到芯片。在中心偏左上方,一個大的規則矩形電路塊提供 160 位存儲:這是兩個 8 字 FIFO 緩沖區,在接口總線和連接的微處理器之間傳遞 10 位字。邊緣周圍的厚金屬跡線為芯片提供+12伏、+5伏和接地電壓。

PHI 芯片的裸片顯微照片

邏輯門

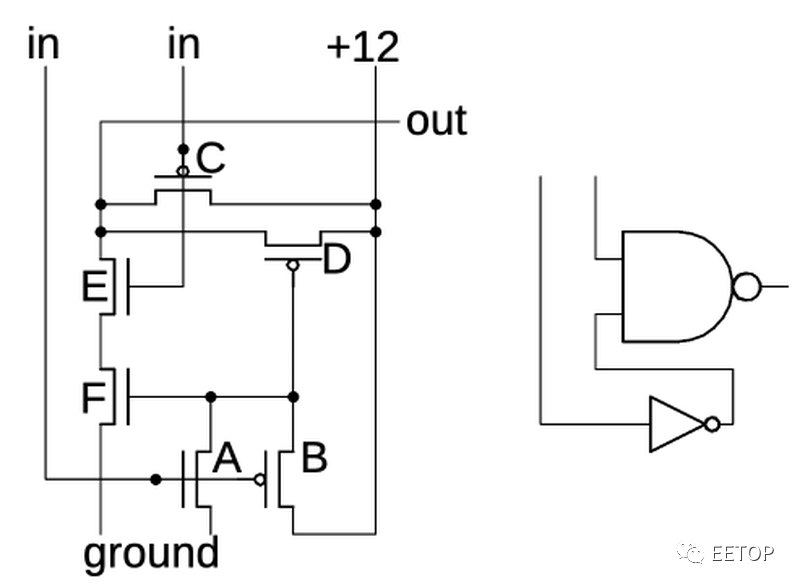

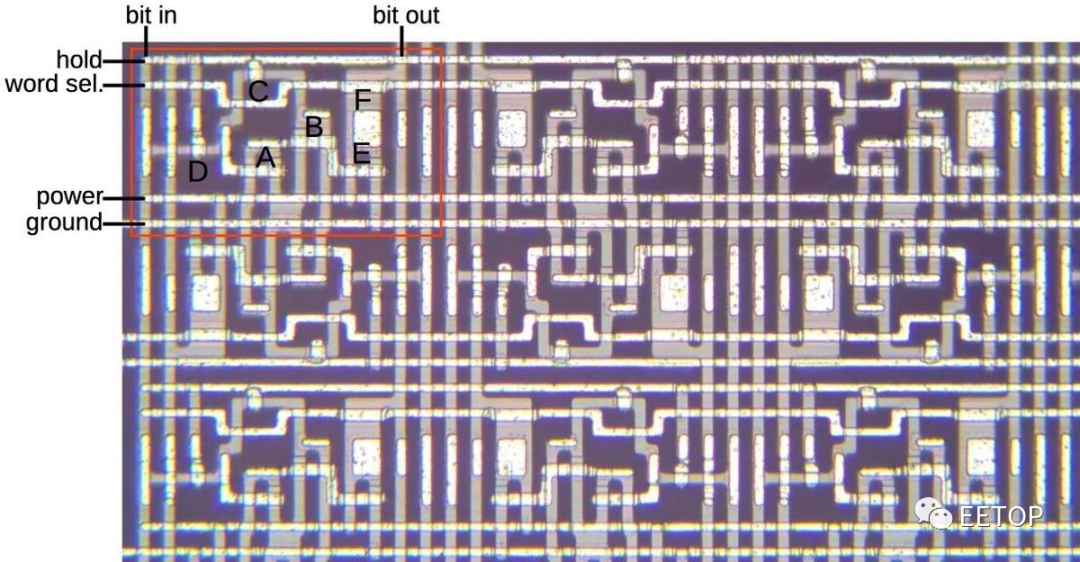

由于藍寶石硅實現以及金屬柵極晶體管的使用,該芯片上的電路具有不尋常的外觀,但基本上電路是標準 CMOS。下圖顯示了一個實現反相器和 NAND 門的塊。藍寶石基板呈深紫色。最重要的是,粗灰色線是硅。頂部的白色金屬連接晶體管。當金屬穿過硅時(用字母表示),也可以形成晶體管的柵極。不方便的是,接觸硅的金屬、跨越硅的金屬以及形成晶體管的金屬在該芯片中都顯得非常相似。這使得確定接線更加困難。

該圖顯示了芯片上的反相器和 NAND 門。

下面的示意圖顯示了門的實現方式,與上面的照片相匹配。頂部和底部的金屬線分別提供電源軌和接地軌。反相器由NMOS晶體管A和PMOS晶體管B組成;輸出進入晶體管 D 和 F。NAND 門由 NMOS 晶體管 E 和 F 以及 PMOS 晶體管 C 和 D 組成。NAND 門的組件在金屬方塊處連接,然后輸出通過硅離開在右側。請注意,只有當一個信號位于硅層中且一個信號位于金屬層中時,信號才能交叉。由于只有兩層布線,PHI 芯片中的信號必須經常蜿蜒以避免交叉,浪費了大量空間。(這種布線比 20 世紀 70 年代也具有多晶硅層的典型芯片受到更多限制,總共提供了三個布線層。)

該示意圖顯示了反相器和 NAND 門的實現方式

FIFO

PHI 芯片有兩個先進先出緩沖器 (FIFO),占芯片的很大一部分。每個 FIFO 保存 8 個字,每字 10 位,其中一個 FIFO 保存從總線讀取的數據,另一個 FIFO 保存向總線寫入的數據。這些緩沖器有助于使總線速度與微處理器速度相匹配,確保數據傳輸盡可能快。

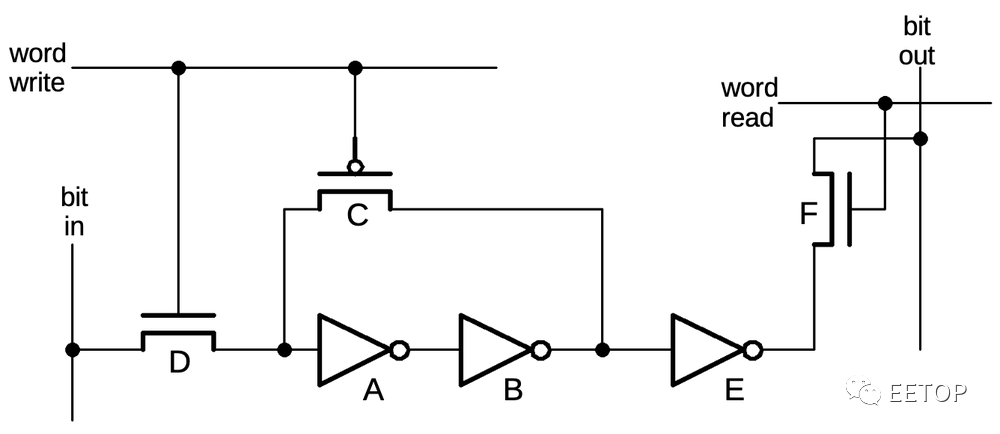

FIFO 的每一位基本上都是一個靜態 RAM 單元,如下圖所示。反相器 A 和 B 形成一個環路,用于保持一個比特。通過晶體管 C 提供反饋,使反相器環路保持穩定。要寫入一個字,需要通過垂直位輸入線輸入 10 位。水平字寫入信號被激活,以選擇要更新的字。這將禁用晶體管 C 并開啟晶體管 D,使新比特流入反相器環路。要讀取一個字,水平字讀取線會被激活,并打開傳遞晶體管 F。這樣,單元中的位就會流入垂直位輸出線,并由反相器 E 緩沖。兩個FIFO具有單獨的行,因此可以獨立讀取和寫入。

FIFO 的一個單元

下圖顯示了裸片上出現的 9 個 FIFO 單元。紅色框表示一個單元,其組件已標記為與原理圖相匹配。單元在垂直和水平方向上鏡像以增加布局密度。

裸片上的九個 FIFO 單元

FIFO 左側和右側的控制邏輯(未示出)管理 FIFO。該邏輯生成適當的讀取和寫入信號,以便將數據寫入 FIFO 的一端并從另一端讀取。

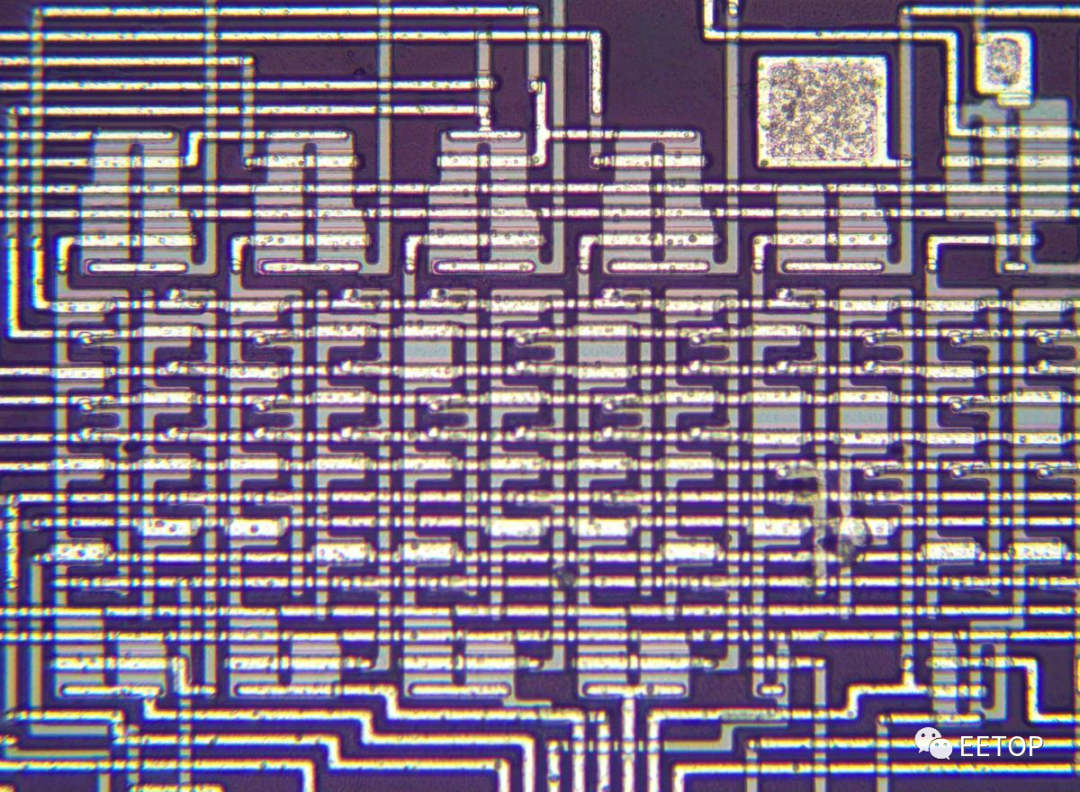

地址譯碼器

另一個有趣的電路是根據地址線選擇特定寄存器的譯碼器。PHI 芯片有八個寄存器,由三個地址線選擇。譯碼器獲取地址線并生成 16 條控制線(或多或少),一根用于從每個寄存器讀取,一根用于寫入每個寄存器。

地址譯碼器的照片

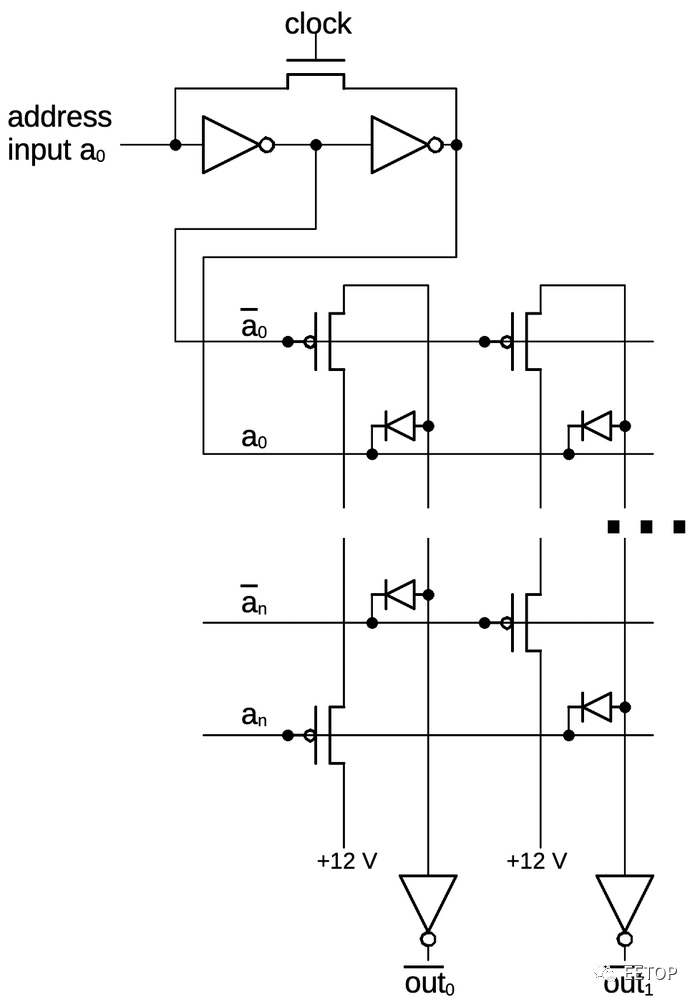

譯碼器具有規則的矩陣結構,可有效實現。行線是成對的,每個地址位輸入及其補碼都有一行。每一列對應一個輸出,晶體管的排列使得當給定適當的輸入時該列將被激活。頂部和底部是逆變器。它們鎖存傳入的地址位、生成補碼并緩沖輸出。

解碼器示意圖

上圖顯示了譯碼器的工作原理。(我將其簡化為兩個輸入和兩個輸出。)在頂部,地址線穿過由兩個反相器和一個傳輸晶體管組成的鎖存器。地址線及其補碼構成兩條行線;其他行線類似。每列的一條行線上有一個晶體管,另一條行線上有一個二極管,用于選擇該列的地址。例如,假設0為 1,n為 0。這與第一列匹配,因為晶體管線為低電平,二極管線為高電平。該列中的 PMOS 晶體管將全部導通,從而將反相器的輸入拉高。然而,如果任何輸入“錯誤”,相應的晶體管將關閉,從而阻斷 +12 伏電壓。此外,輸出將通過相應的二極管拉低。因此,只有當所有輸入匹配時,每列才會被拉高,否則將被拉低。每列輸出控制芯片的一個寄存器,允許訪問該寄存器。

HP-IB總線和PHI芯片

接口總線 (HP-IB) 于 20 世紀 70 年代初設計,作為一種低成本總線,用于連接各種設備,包括儀器系統(例如數字電壓表或頻率計數器)、存儲器和計算機。該總線于 1975 年成為 IEEE 標準,稱為IEEE-488 總線。2 總線是 8 位并行,設備之間通過握手,因此慢速設備可以控制速度。

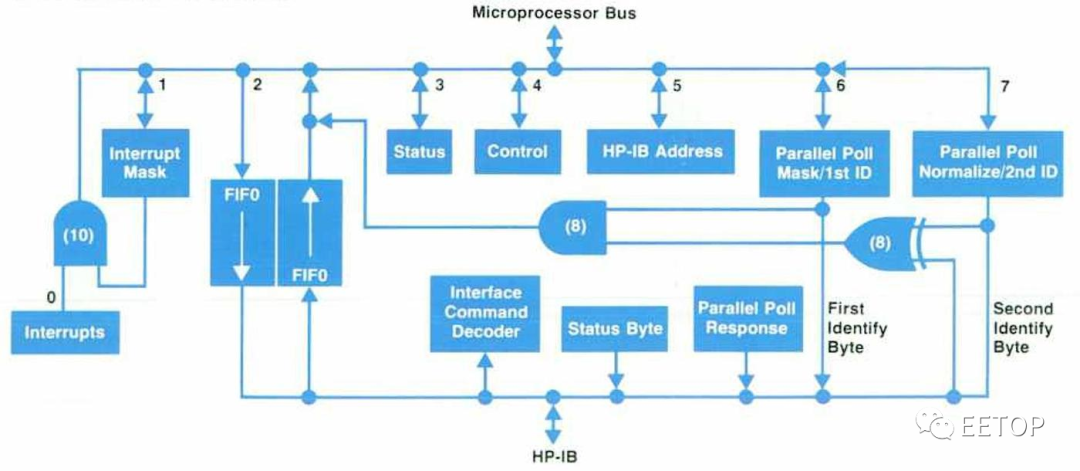

1977年,開發了一款芯片,稱為PHI(Processorto HP-IB Interface),用于實現總線協議并提供微處理器接口。該芯片不僅簡化了總線控制器的構造,而且確保設備一致地執行協議。下面的框圖顯示了 PHI 芯片的組件。它不是一個特別復雜的芯片,但也不是微不足道的。我估計它有幾千個晶體管。

框圖來自HP Journal,1989 年 7 月

下面的芯片照片顯示了 PHI 芯片的一些功能塊。微處理器連接到頂部引腳,而接口總線連接到下部引腳。

PHI 芯片帶有一些標記的功能塊

結論

PHI 芯片作為“未來技術”的一個例子很有趣,但并沒有完全成功。在藍寶石硅芯片上投入了大量精力,期望這將成為一項重要的技術:密集、快速和低功耗。然而,事實證明,普通硅芯片是獲勝的技術,而藍寶石硅芯片則被降級到利基市場。

PHI 芯片的時期也很有趣,因為接口總線正在從簡單的總線過渡到具有復雜協議的高性能總線。早期的總線可以用簡單的集成電路來實現,但隨著協議變得更加復雜,定制接口芯片變得必要。(MOS 6522 多功能接口適配器芯片(1977 年)是另一個例子,在 20 世紀 80 年代的許多家用計算機中使用。)但這些接口仍然足夠簡單,接口芯片不需要微控制器,而是使用簡單的狀態機。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19160瀏覽量

229117 -

芯片

+關注

關注

453文章

50396瀏覽量

421793 -

pcb

+關注

關注

4317文章

23004瀏覽量

396251 -

控制器

+關注

關注

112文章

16198瀏覽量

177399 -

計算機

+關注

關注

19文章

7419瀏覽量

87714

原文標題:顯微拆解:揭示47年前神秘藍寶石透明芯片的奧秘

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

分享一顆電機控制芯片—LV8548MC

一顆改變了世界的芯片

一顆來自40年前的透明芯片究竟暗藏了哪些奧秘

一顆來自40年前的透明芯片究竟暗藏了哪些奧秘

評論