對(duì)FPGA設(shè)計(jì)而言如果想速度更快則應(yīng)當(dāng)努力減少路徑上LUT的個(gè)數(shù),而不是邏輯級(jí)數(shù)。如果想面積更小則應(yīng)當(dāng)努力減少LUT的個(gè)數(shù)而不是邏輯門(mén)數(shù)。

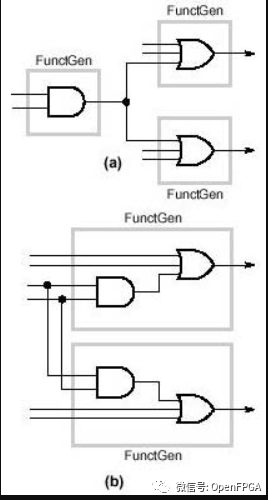

如下圖:

采用圖a結(jié)構(gòu),我們知道一個(gè)LUT只有一個(gè)輸出,因此前面的2輸入與門(mén)要占用一個(gè)LUT 后面的2個(gè)三輸入或門(mén)要各占用一個(gè)LUT 總共占用3個(gè)LUT LUT級(jí)數(shù)是2級(jí)。

采用圖b結(jié)構(gòu),其實(shí)現(xiàn)結(jié)果等效于圖a結(jié)構(gòu),雖然增加了一個(gè)2輸入與門(mén)并且邏輯級(jí)數(shù)與圖a一樣也是2級(jí)但我們根據(jù)LUT特點(diǎn)它只占用2個(gè)LUT:

2輸入與門(mén)和3輸入或門(mén)由一個(gè)LUT實(shí)現(xiàn)LUT級(jí)數(shù)只有1級(jí),這就是一個(gè)門(mén)數(shù)增加邏輯級(jí)數(shù)未變但資源占用減少速度更快典型案例

審核編輯:劉清

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489 -

LUT

+關(guān)注

關(guān)注

0文章

49瀏覽量

12487

原文標(biāo)題:【FPGA】減少路徑上的LUT個(gè)數(shù)使速度更快

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CyU3PDmaMultiChannelCommitBuffer失敗后,如何使重置速度更快?

LUT實(shí)現(xiàn)的逆變器真的是FPGA上的逆變器嗎?

Spartan 3器件上的專(zhuān)用乘法器路徑時(shí)間隨著階段數(shù)量的增加而減少

如何讓這個(gè)設(shè)計(jì)通過(guò)減少顏色量可能更快

Kintex 7輸入IO焊盤(pán)和FF(片寄存器)之間的額外LUT是什么

怎樣去解決NVIC_EnableIRQ使能無(wú)法進(jìn)行的問(wèn)題呢

如何更快的使硬件數(shù)據(jù)傳到webservice服務(wù)接口呢

求助前輩們Verilog lut個(gè)數(shù)的問(wèn)題

如何使FRAM MCU速度更快所需功耗最低

怎樣減少路徑上的LUT個(gè)數(shù)使速度更快呢?

怎樣減少路徑上的LUT個(gè)數(shù)使速度更快呢?

評(píng)論