攸關(guān)臺積電2納米以下先進(jìn)制程布局的中科臺中園區(qū)擴(kuò)建二期都市計(jì)劃變更案,內(nèi)政部都市計(jì)劃委員會昨天決議通過。臺積電目前尚未對這塊地是否由原規(guī)劃的2納米用地,變更為更先進(jìn)的1.4納米使用,臺積電供應(yīng)鏈推測,以目前臺積電將寶山及高雄展開2納米建廠作業(yè),預(yù)料中科二期擴(kuò)建將會把1.4納米制程列入未來建廠優(yōu)先計(jì)劃。

不過,據(jù)了解,臺積電仍未放棄在北部建立1.4納米生產(chǎn)基地的念頭。中科管理局表示,后續(xù)將請臺中市政府協(xié)助盡速辦理公告實(shí)施,以利接續(xù)啟動(dòng)用地取得作業(yè),預(yù)計(jì)明年六月底提供土地給廠商建廠,以應(yīng)產(chǎn)業(yè)發(fā)展需求。

由于中科二期擴(kuò)建先前已獲臺中市都市計(jì)劃委員會通過變更案,內(nèi)政部昨天審議通過,符合臺積電內(nèi)部預(yù)期,因此公司除了感謝相關(guān)單位協(xié)助外,不對此案后續(xù)規(guī)劃做任何回應(yīng)。

中科臺中園區(qū)擴(kuò)建二期緊鄰臺中園區(qū)西側(cè),面積八十九點(diǎn)七五公頃。根據(jù)臺積電最初向中科管理局提出的中科擴(kuò)大計(jì)劃用地申請,臺積電希望中科二期擴(kuò)大計(jì)劃作為2納米的備援用地,后來臺中市政府審定將面積縮小,頂多只有興建兩座2納米旗艦廠。

相較臺積電以內(nèi)部編定為Fab20的寶山廠為2納米生產(chǎn)重鎮(zhèn),后來也將高雄廠變更切入2納米,形成南北都有2納米生產(chǎn)據(jù)點(diǎn),一般預(yù)料在臺積電宣布放棄原打算作為1.4納米生產(chǎn)據(jù)點(diǎn)的桃園龍?zhí)犊茖W(xué)園區(qū)三期擴(kuò)大計(jì)劃后,可能先將中科二期擴(kuò)大用地,作為1.4納米的優(yōu)先用地規(guī)劃,但臺積電仍會視各縣市爭取的態(tài)度以及提出方配套計(jì)劃,再挑一處1.4納米,甚至是更先進(jìn)的一納米用地。

目前包括高雄、臺南、嘉義、云林和臺中等縣市,都表態(tài)歡迎臺積電前去設(shè)立先進(jìn)制程晶圓廠,預(yù)料臺積電應(yīng)會評選其他用地規(guī)劃后,再做最后定奪。中科管理局局長王永壯稍早釋出臺積電寶山廠將于明年四月開始裝機(jī),第二廠也同步加緊建廠作業(yè),以利2納米能如期在2025年量產(chǎn)。

可靠消息人士透露,臺積電高雄廠則規(guī)劃切入2納米強(qiáng)化版(N2P)制程,預(yù)定2026年量產(chǎn);以此時(shí)程推估,臺積電的1.4納米推出時(shí)間將落在2027到2028年,中科二期擴(kuò)大計(jì)劃,可讓臺積電在決定未來先導(dǎo)入2納米或直接切入1.4納米,有了更大的彈性及和各縣市談條件的空間。

臺積電首次提及1.4nm工藝

據(jù)tomshardware報(bào)道,臺積電在 IEEE 國際電子器件會議 (IEDM) 的未來邏輯小組上透露,臺積電 1.4 納米級制造技術(shù)的開發(fā)正在順利進(jìn)行 。臺積電還再次強(qiáng)調(diào),使用其 2 納米級制造工藝的量產(chǎn)有望在 2025 年實(shí)現(xiàn)。

根據(jù) SemiAnalysis 的Dylan Patel發(fā)布的幻燈片,臺積電的 1.4 納米生產(chǎn)節(jié)點(diǎn)正式稱為 A14 。目前,臺積電尚未透露計(jì)劃何時(shí)開始 A14 及其規(guī)格的量產(chǎn)(HVM),但鑒于 N2 計(jì)劃于 2025 年末、N2P 計(jì)劃于 2026 年末,因此有理由猜測 A14 會在此之后推出。也就是介乎2027到2028年之間。

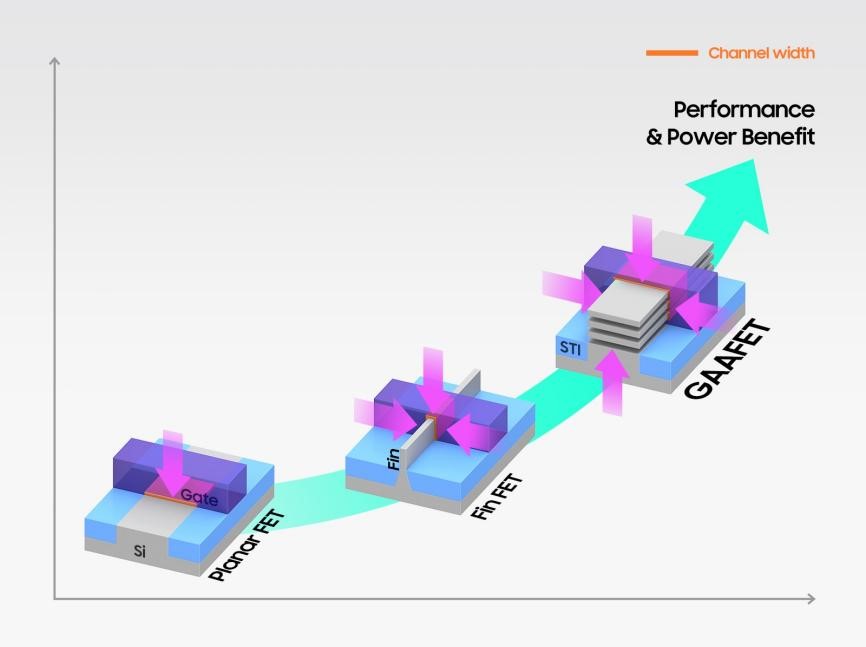

在功能方面,A14不太可能采用垂直堆疊互補(bǔ)場效應(yīng)晶體管(CFET),盡管臺積電正在探索該技術(shù)。因此,A14 可能會依賴該公司的第二代或第三代環(huán)柵 FET (GAAFET)——就像 N2 節(jié)點(diǎn)一樣。

N2 和 A14 等節(jié)點(diǎn)將需要系統(tǒng)級協(xié)同優(yōu)化才能真正發(fā)揮作用,并實(shí)現(xiàn)新水平的性能、功耗和功能。

仍有待觀察的是臺積電是否計(jì)劃在 2027 年至 2028 年期間為其 A14 工藝技術(shù)采用高數(shù)值孔徑 EUV 光刻工具。鑒于到那時(shí)英特爾(可能還有其他芯片制造商)將采用并完善數(shù)值孔徑為 0.55 的下一代 EUV 光刻機(jī),芯片合同制造商應(yīng)該相當(dāng)容易使用它們。然而,由于高數(shù)值孔徑 EUV 光刻工具將掩模版尺寸減半,其使用將為芯片設(shè)計(jì)者和芯片制造商帶來一些額外的挑戰(zhàn)。

當(dāng)然,從現(xiàn)在到 2027 - 2028 年,情況可能會發(fā)生變化,因此我們不能做出太多假設(shè)。但很明顯,臺積電的科學(xué)家和開發(fā)人員正在研究下一代生產(chǎn)節(jié)點(diǎn)。

隨著半導(dǎo)體工藝深入到5nm以下,制造的難度和成本日益增加。摩爾定律的物理極限大約在1nm左右,再往下就會面臨嚴(yán)重的量子隧穿難題,這將導(dǎo)致晶體管失效。各大廠商在實(shí)際尺寸上采用的先進(jìn)工藝仍有一定的余地,紙面上的1nm工藝仍可能存在。

臺積電去年成立了一個(gè)團(tuán)隊(duì)來研發(fā)1.4nm工藝,CEO劉德音表示公司正在探索比1.4nm更先進(jìn)的工藝。1.4nm工藝是半導(dǎo)體行業(yè)追求的目標(biāo)之一,但將會面臨很大的挑戰(zhàn)。

根據(jù)IMEC歐洲微電子中心的路線圖,2nm工藝之后是14A,也就是1.4nm工藝,預(yù)計(jì)在2026年問世,再往后就是A10工藝,也就是1nm,預(yù)計(jì)在2028年問世。

然而,實(shí)際量產(chǎn)時(shí)間可能會延后。在2nm節(jié)點(diǎn)之后,EUV光刻機(jī)需要進(jìn)行大規(guī)模升級,ASML預(yù)計(jì)在2026年推出下一代EXE:5000系列,采用High NA技術(shù)提高光刻分辨率。但下一代EUV光刻機(jī)的售價(jià)將從1.5億美元上漲到4億美元以上,甚至可能會進(jìn)一步增加,這對制造商的成本控制能力提出了很大的考驗(yàn)。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27063瀏覽量

216488 -

臺積電

+關(guān)注

關(guān)注

44文章

5611瀏覽量

166161 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876

原文標(biāo)題:臺積電1.4nm,有新進(jìn)展

文章出處:【微信號:TenOne_TSMC,微信公眾號:芯片半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電1nm進(jìn)展曝光!預(yù)計(jì)投資超萬億新臺幣,真有必要嗎?

臺積電1.4nm,有新進(jìn)展

臺積電1.4nm,有新進(jìn)展

評論