據報道,臺積電在近期舉行的IEDM 2023會議上制定了芯片封裝計劃,其中包括提供擁有萬億晶體管能力的封裝產品,該計劃與早前英特爾所披露的規劃相似。然而,需要注意的是,這個萬億晶體管并非指單個芯片封裝的總量,而是源于多個3D封裝小芯片。盡管如此,臺積電仍在全力以赴提高單片芯片的制造潛能,爭取開發出含有兩千億晶體管的封裝芯片。

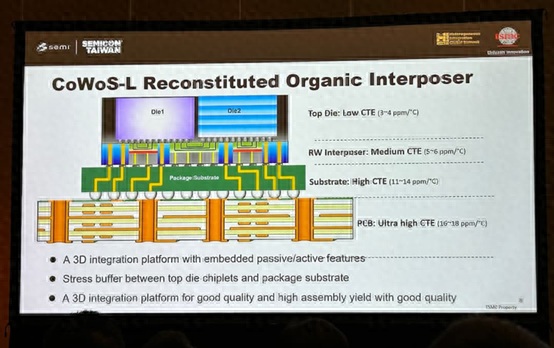

為達成此目標,公司正加緊推進N2和N2P級別的2nm制造節點研究,并同步發展A14和A10級別的1.4nm加工工藝,預計到2030年可以實現。此外,臺積電預計封裝技術,如CoWoS、InFO、SoIC等會不斷優化升級,使他們有望在2030年前后打造出超萬億晶體管的大規模封裝解決方案。

值得一提的是,臺積電在本次會議中還透露他們已全面啟動1.4nm級制作流程研發工作。同樣,該公司再次確認,按照原定計劃,2nm級制造流程將從2025年起進入大規模商業化。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

臺積電

+關注

關注

44文章

5609瀏覽量

166112 -

封裝技術

+關注

關注

12文章

545瀏覽量

67961 -

晶體管

+關注

關注

77文章

9633瀏覽量

137841

發布評論請先 登錄

相關推薦

新思科技發布1.6納米背面布線技術,助力萬億晶體管芯片發展

近日,新思科技(Synopsys)宣布了一項重大的技術突破,成功推出了1.6納米背面電源布線項目。這一技術將成為未來萬億晶體管芯片制造過程中的關鍵所在。

臺積電封裝,新規劃

來源:半導體芯聞綜合 臺積電高效能封裝整合處處長侯上勇3 日在Semicon Taiwan 2024 中舉行專題演講,表示被視為是三種CoWoS 產品中,能滿足所有條件的最佳解決方案,

臺積電布局FOPLP技術,推動芯片封裝新變革

近日,業界傳來重要消息,臺積電已正式組建專注于扇出型面板級封裝(FOPLP)的團隊,并規劃建立小型試產線(mini line),標志著這家全

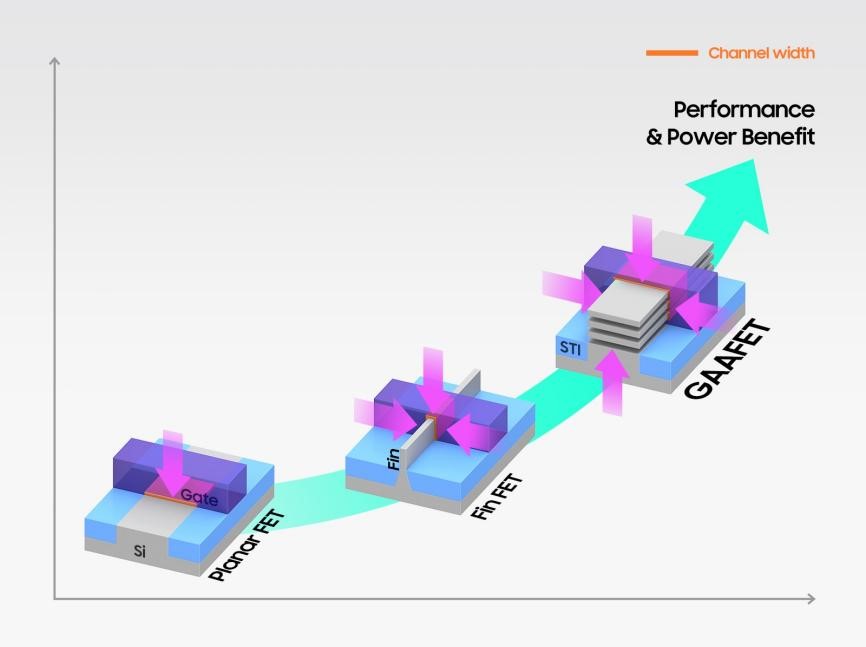

臺積電跨制程整合晶體管架構并引入CFET,發布新一代芯片技術

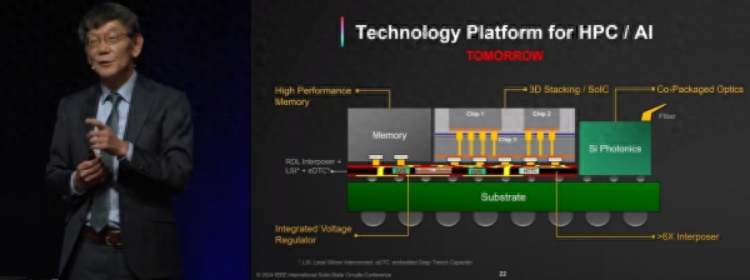

張曉強強調,半導體產業的黃金時代已然來臨,未來AI芯片的發展幾乎99%都依賴于臺積電的先進邏輯技術和先進封裝技術。

臺積電創新推出萬億晶體管封裝平臺,專注于高性能計算和AI芯片應用

臺積電高級研發副總裁張曉強指出,本項新技術主要針對AI芯片性能增強。新型HBM高帶寬存儲器與Chiplet架構小芯片的引入需求大量組件及IC

臺積電的1納米技術挑戰與成本壓力的博弈

1納米尺寸的芯片制造面臨著物理極限的挑戰,可能導致晶體管的性能下降甚至失效。作為半導體行業的重要參與者之一,臺積

英特爾:2030年前實現單個封裝內集成1萬億個晶體管

12月9日,英特爾在IEDM 2023(2023 IEEE 國際電子器件會議)上展示了使用背面電源觸點將晶體管縮小到1納米及以上范圍的關鍵技術。英特爾表示將在2030年前實現在單個封裝內集成1

臺積電:規劃1萬億晶體管芯片封裝策略

臺積電:規劃1萬億晶體管芯片封裝策略

評論