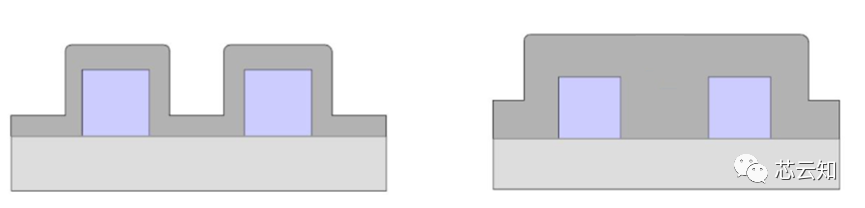

薄膜的保角性,又稱保形性,指的是薄膜淀積臺階覆蓋能力和空隙填充能力,以及保留原始形狀的能力。保角性不能簡單地和臺階覆蓋性劃等號,保角性的概念包含了臺階覆蓋的概念。

薄膜保角性,要求所有圖形上(表面、底面和側壁)淀積的薄膜厚度相同,也稱共性覆蓋。而臺階覆蓋性,不要求沿著臺階所有界面的膜層厚度是均勻的,只要能覆蓋下層。因此,薄膜保角性比臺階覆蓋性要求更高。那么如何做到好的保角性呢?要求淀積物在臺階表面吸附后迅速遷移,才能使薄膜厚度均勻。這樣就有必要介紹薄膜的沉積方式。

圖1 保角性和臺階覆蓋性的比較

物理氣相沉積(PVD,Physical Vapor Deposition),一般針對淀積金屬薄膜。是在真空條件下,金屬源通過物理驅動傳輸到襯底上,主要的方法包括蒸發和濺射。PVD淀積薄膜在不平整的表面時,在表面淀積的速率明顯高于側壁,且側壁越靠下,淀積速率越低,造成臺階頂部的突懸。高深寬比的臺階,基本不提保角性,甚至無法做到良好的臺階覆蓋,側壁靠下部分無法淀積薄膜。這也是TGV(玻璃通孔)、TSV(硅通孔)技術和通孔填銅的技術難點。那么對比蒸發和濺射,哪種臺階覆蓋更好呢?一般而言,認為濺射更好,尤其是射頻磁控濺射,通過襯底加熱和對襯底施加射頻都可以提高臺階覆蓋性。

圖2 臺階懸突和臺階保角

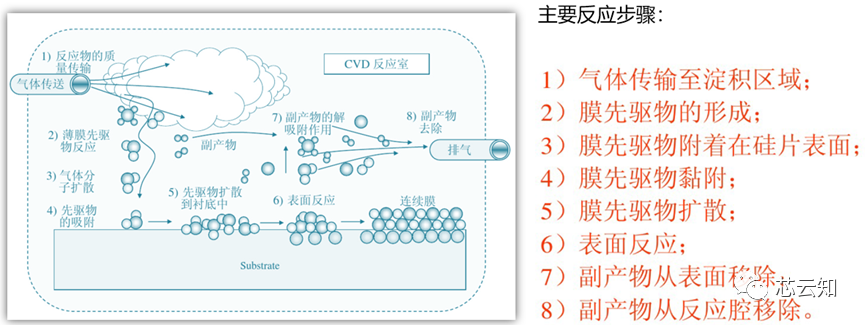

化學氣相沉積(CVD,Chemical Vapor Deposition)是半導體工業中應用最為廣泛的材料淀積技術,包括大部分的的介質薄膜和少量的金屬薄膜。從原理上說,兩種或兩種以上的氣態或液態原材料導入到一個反應室內,通過吸附、化學反應和排出副產物,形成目標膜層在襯底淀積。由于CVD是直接在圖形上生成目標物,因此它的保角性是值得探索和研究的。CVD參數的可調范圍是很寬:反應室內的壓力、晶片的溫度、氣體的流動速率、氣體通過晶片的路程、氣體的化學成份、一種氣體相對于另一種氣體的比率等,合適的淀積參數確定,是形成保角性的必要條件。

圖3 CVD沉積原理圖示和反應步驟

CVD技術常常通過反應類型或者壓力來分類,包括低壓CVD(LPCVD),常壓CVD(APCVD),亞常壓CVD(SACVD),超高真空CVD(UHCVD),等離子體增強CVD(PECVD),高密度等離子體CVD(HDPCVD)和快熱CVD(RTCVD)。

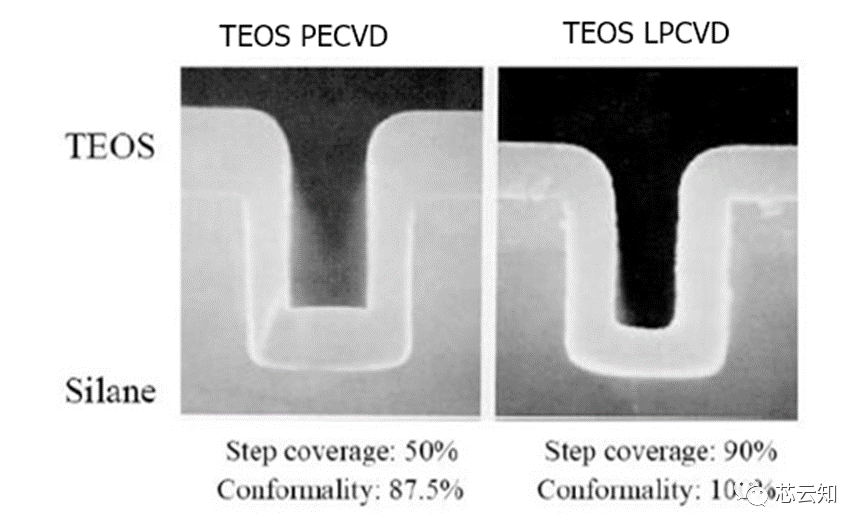

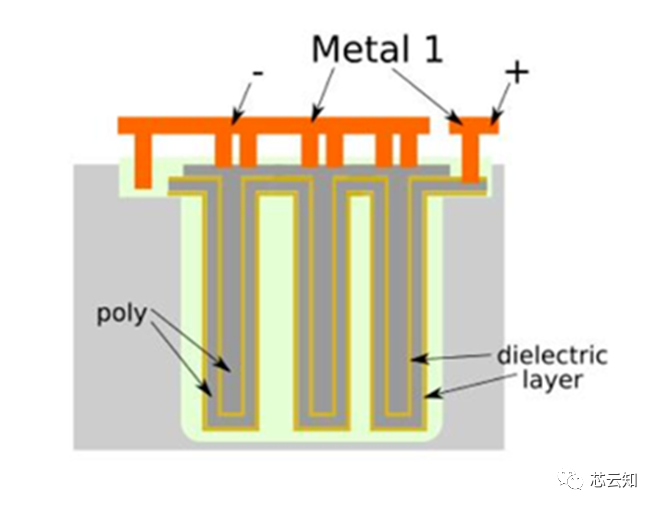

一般情況,搭配液態源的LPCVD和PECVD有可能實現較好的薄膜保角性。正硅酸乙脂(TEOS)為無色透明液體,在700 ℃以上,低壓摻氧條件下分解可產生二氧化硅和有機物,其中氧對TEOS熱分解起到催化作用,其介質層膜厚均勻、保角性好且具有良好的介電性能。在硅電容中,即采用LPCVD在深溝槽內沉積多晶硅淀積極板層。

圖4 TEOS的兩種CVD臺階覆蓋性和保角性的比較

另外介紹一種保角性近乎100%的技術,原子層沉積ALD,這也是CVD的一種。ALD是一層一層的生長工藝,每一周期有自約束,因此對于超薄層生長的控制要好得多。在襯底絕緣層氧化物上,對保角性要求高且薄膜厚度低的場景非常適用。在硅電容中,深溝槽中的絕緣層即可采用ALD保證其厚度均勻性好。

圖5 深溝槽硅電容示意圖

盡管CVD比PVD有更好的臺階覆蓋特性,但目前通孔填銅的種子層和鉭氮擴散層薄膜都是通過PVD來淀積的,CVD實際應用大部分在介質膜和絕緣膜,實際的工藝選擇還是需要根據芯片的設計要求,并不是說所有的膜層都要求100%保角性。

審核編輯:劉清

-

PVD

+關注

關注

4文章

48瀏覽量

16891 -

TSV

+關注

關注

4文章

105瀏覽量

81372

原文標題:薄膜淀積工藝的保角性=臺階覆蓋性嗎?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

表面硅MEMS加工技術的關鍵工藝

電鍍對印制PCB電路板的重要性

化學機械拋光(CMP) 技術的發展應用及存在問題

基于單應性矩陣的棋盤格角點檢測研究

薄膜淀積工藝的保角性=臺階覆蓋性嗎?如何做到好的保角性呢?

薄膜淀積工藝的保角性=臺階覆蓋性嗎?如何做到好的保角性呢?

評論