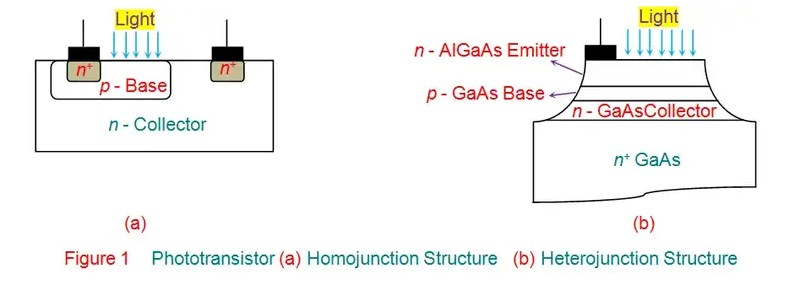

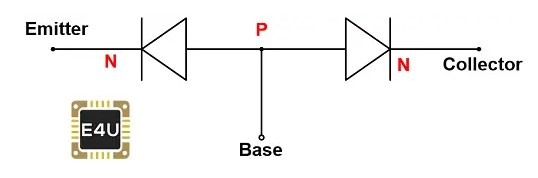

互補場效應晶體管(CFET)晶體管結構采用晶體管垂直堆疊結構,能夠緩解關斷狀態下的漏電和晶體管閾值隨柵長變化帶來的問題,也使得晶體管能夠在更小的空間內實現更佳的性能。下面來介紹CFET的技術進展以及未來的機遇與挑戰。 在剛剛落下帷幕的2023年IEEE國際電子器件會議(IEDM2023)上,臺積電、三星和英特爾各自秀出了在下一代晶體管結構領域的尖端技術。圖中這款被稱為“互補場效應晶體管(CFET)”的晶體管結構,被視為1nm以下制程的關鍵要素,是繼FinFET和GAA之后的新一代的晶體管技術。它的出現,將為半導體行業帶來哪些不一樣的圖景?

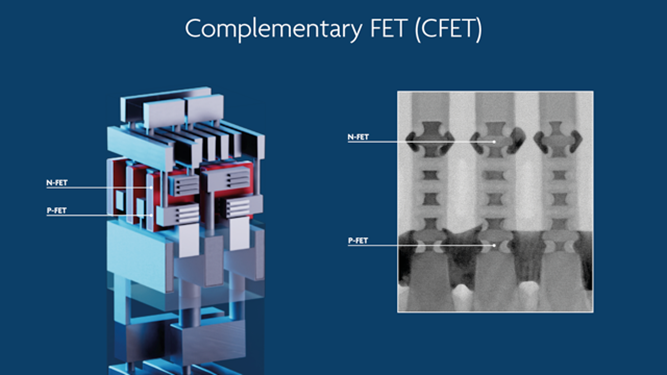

CFET示意圖(圖片來源:imec)

CFET將開啟三維晶體管結構新紀元?

據了解,CFET與此前晶體管結構的最大不同之處,在于采用晶體管垂直堆疊結構,這或將開啟三維晶體管結構新紀元。

在FinFET和GAA架構出現以前,芯片晶體管結構采用的是平面MOSFET,這種結構可以通過等比例縮小器件尺寸來提高器件性能,增大芯片上器件數量。但是,當溝道長度小于一定值時,柵極對于溝道的控制能力會下降,出現短溝道效應。為了解決這個問題,業界提出了FinFET和GAA兩種新型晶體管結構。前者通過將溝道向上延展形成立體結構,后者采用柵極環繞溝道的結構,來緩解關斷狀態下的漏電和晶體管閾值隨柵長變化帶來的問題,也使得晶體管能夠在更小的空間內實現更佳的性能。

然而,由于晶體管結構從平面轉換到了立體結構,難以繼續通過等比例縮小晶體管尺寸來增加芯片上器件密度。隨著摩爾定律的不斷發展,芯片制程也愈發接近物理極限,為了能夠進一步增加單位面積上的器件數量,業內開始嘗試將原本的立體結構晶體管再進行堆疊,提出了采用垂直堆疊結構的CFET。

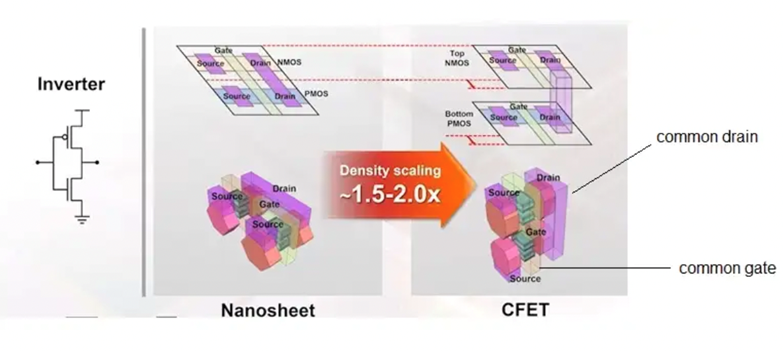

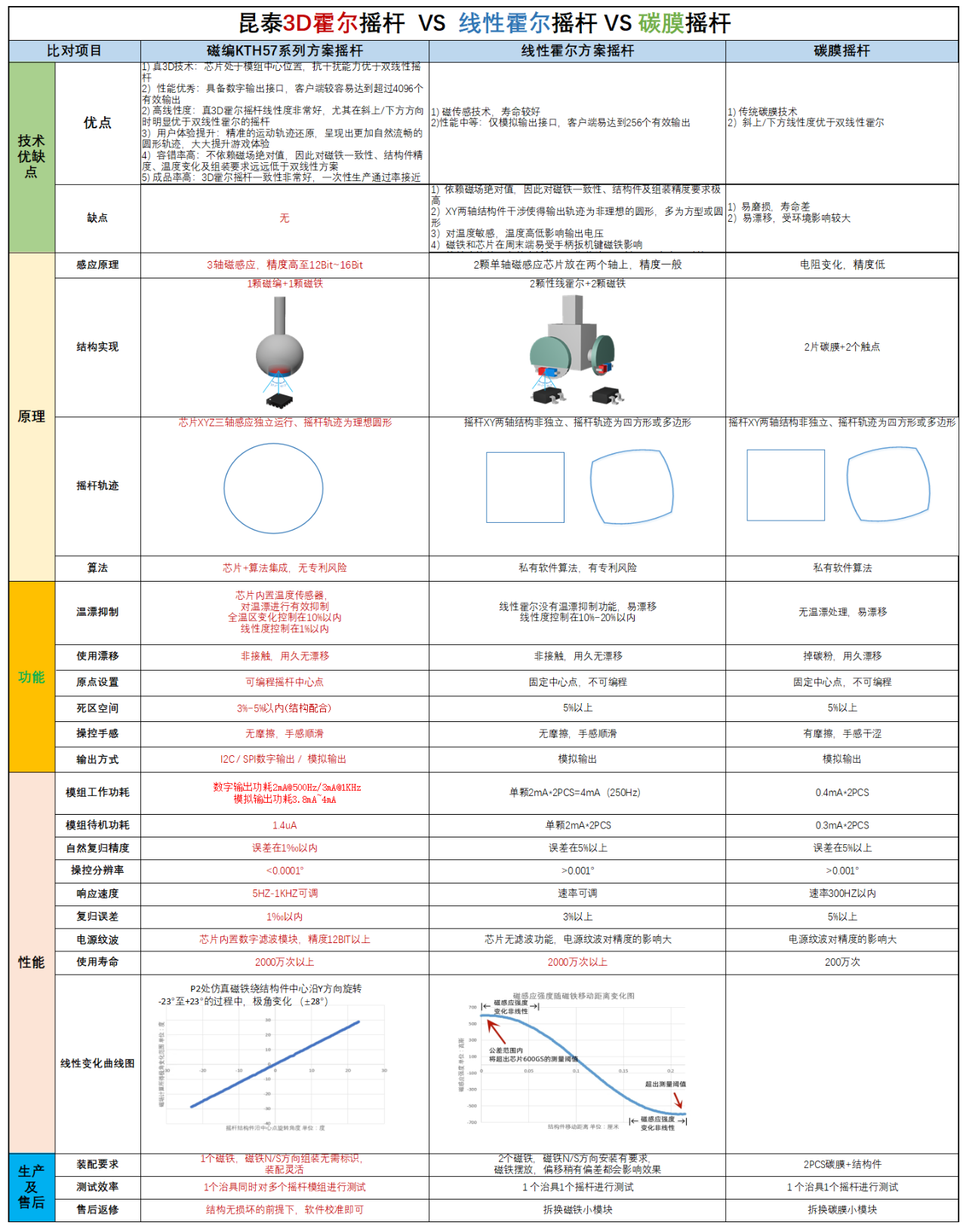

臺積電最新資料顯示,采用CFET垂直堆疊架構的芯片,相較采用Nanosheet(GAA)架構的器件,面積最多能縮小50%。

采用CFET架構的器件面積最多能夠縮小50%(圖片來源:臺積電)

三大家集體公布CFET相關技術進展

基于此,先進制程的三大頭部玩家臺積電、三星、英特爾都在密切關注CFET相關技術。

臺積電指出,CFET晶體管現已在臺積電實驗室中進行性能、效率和密度測試,并已經實現了48nm的柵極間距。此外,臺積電還介紹了在CFET晶體管方面獨特的設計和制造方法:在頂部和底部器件之間形成介電層以保持它們的隔離,這種設計可以減少漏電和功耗。為了進一步實現更好的性能和更高的集成度,臺積電在其CFET晶體管工藝中,嘗試將納米片中硅和硅鍺的交替層進一步隔離。例如,臺積電通過特定的蝕刻方法去除納米片中的硅鍺材料,從而釋放硅納米線。為了能將納米片中硅和硅鍺的交替層進一步隔離,臺積電使用了鍺含量異常高的硅鍺。這種材料比其他SiGe層蝕刻得更快,因此可以在釋放硅納米線之前構建隔離層。

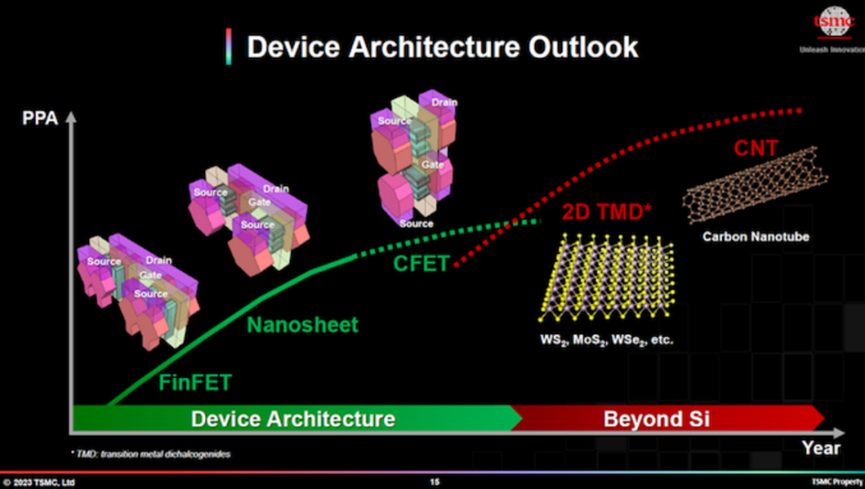

臺積電在最新的架構迭代介紹中加上了CFET結構(圖片來源:臺積電)

三星將CFET晶體管結構稱為3DSFET,目前的柵極間距為45/48nm。在技術創新方面,三星實現了對堆疊式pFET(P溝道場效應管)和nFET(n溝道場效應管)器件的源極和漏極進行有效的電氣隔離。這種隔離可以有效地減少漏電流,提高器件性能和可靠性。此外,三星還通過將濕化學物質的刻蝕步驟替換為新型干法刻蝕,以此讓芯片中CFET器件的良率顯著提升。

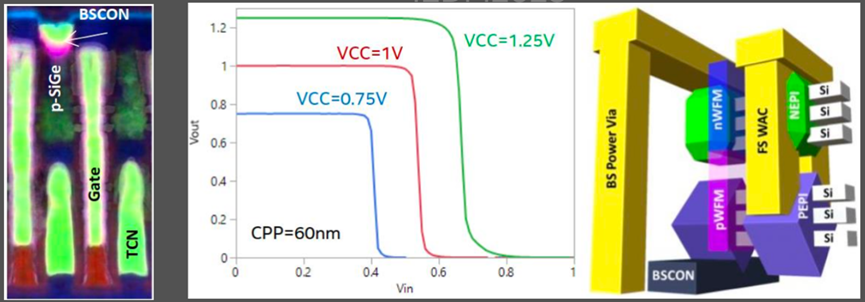

英特爾展示了將CFET晶體管結構與背面供電技術相結合的新技術,并利用該技術實現了60nm的柵極間距。英特爾表示,此次在CFET方面的創新之處,在于將PMOS(P型金屬氧化物半導體)和NMOS(N型金屬氧化物半導體)結合在了一起,使得開關速度和驅動能力具有互補性,從而提升了晶體管的整體性能。將PMOS和NMOS與其PowerVia背面供電器件觸點相結合,以此更好地控制電流的流動,提高電源效率。

英特爾CFET示意圖(圖片來源:英特爾)

雖然,三家均未透露將在具體哪個制程節點中采用該晶體管結構,但公開資料顯示,臺積電或將在其2032年量產的A5工藝中,采用CFET架構。

臺積電或將在其2032年量產的A5工藝中采用CFET架構(圖片來源:imec)

平衡成本和性能問題是關鍵

CFET結構“初露端倪”,讓業界看到了晶體管結構新的發展前景。然而,業內專家預估,CFET結構需要7~10年才能投入商用。

為何不能短時間內在現有的芯片制程中采用三維晶體管結構?目前CFET制程需要解決多層堆疊帶來的大量的技術挑戰。

目前,CFET擬采用的工藝路徑是一次外延生長PFET和NFET兩種器件的多層結構,再分別在兩種外延層上制造FET。這大幅增加了器件制造的工藝復雜度,過去在FinFET和GAA中行之有效的工藝方法大部分不再適用。以FET源漏模塊為例,不能再采用離子注入工藝對源漏進行摻雜,需要用雜質在線外延的辦法把摻雜元素帶到源漏區附近,再擴散達成摻雜。這些改變,需要從頭開發新工藝,并逐漸使之成熟。類似的改變還有很多,需要大量和長周期的工藝研發,才能解決存在的全部技術挑戰。

在CFET所需要的新工藝中,多層堆疊熱退火問題是CFET面臨的最大挑戰之一。據了解,半導體材料在晶體生長和制造過程中,由于各種原因會出現缺陷、雜質、位錯等結構性缺陷,導致晶格不完整,施加電場后的電導率較低。通過熱退火處理,可以使材料得到修復,結晶體內部重新排列,去除大部分缺陷和雜質,恢復晶格完整,提高電導率和電學性能。

半導體熱退火需要在1050℃的高溫下進行,在進行熱退火操作后,還需要在芯片內部用銅和鋁等金屬進行互聯。在以往的非堆疊晶體管結構中,僅進行一次熱退火即可,而在堆疊結構中,每堆疊一層就要再多進行一次熱退火。此外,芯片內部的很多金屬互聯材料難以在1050℃的高溫中保持穩定。這也導致在第二層晶體管結構中,無法采用傳統方式來進行整體的熱退火,需要采用激光進行局部退火從而效避開金屬連接處。而采用激光退火不僅會增加工藝難度,還會因設備成本高而提升整體芯片制造成本。

“這就好比,原本用毛筆寫的字,現在要用簽字筆來寫。字的大小沒變,但需要用簽字筆一點點地描繪。因此,采用CFET結構的芯片,需要先解決用激光進行熱退火帶來的成本問題,才能加快商用的步伐。” END 轉載內容僅代表作者觀點 不代表中國科學院半導體所立場

審核編輯:黃飛

-

英特爾

+關注

關注

60文章

9900瀏覽量

171550 -

場效應管

+關注

關注

46文章

1147瀏覽量

63829 -

臺積電

+關注

關注

44文章

5611瀏覽量

166163 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876

原文標題:下一代晶體管結構:小荷已露尖尖角

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

NMOS晶體管和PMOS晶體管的區別

什么是光電晶體管?光電晶體管的工作原理和結構

PNP晶體管的工作原理和結構特性

探索管材加工的未來-高速三維激光切管機

泰來三維|文物三維掃描,文物三維模型怎樣制作

什么是達林頓晶體管?達林頓晶體管的基本電路

CFET將開啟三維晶體管結構新紀元?

CFET將開啟三維晶體管結構新紀元?

評論