摘要

人工智能芯片通常使用 SRAM 存儲器作為緩沖器(buffers),其可靠性和速度有助于實現高性能。然而,SRAM 價格昂貴,需要大量的面積和能耗。以前的研究曾探討過用非易失性存儲器等新興技術取代 SRAM,因為非易失性存儲器具有快速讀取內存和單元面積小的特點。盡管有這些優勢,但非易失性存儲器的寫入內存訪問速度慢、寫入能耗高,因此在需要大量內存訪問的人工智能應用中,非易失性存儲器的性能無法超越 SRAM。一些研究還將 eDRAM 作為一種面積效率高的片上存儲器進行了研究,其存取時間與 SRAM 相似。但是,刷新功耗仍然是一個令人擔憂的問題,性能、面積和功耗之間的權衡尚未解決。

為了解決這個問題,在本文中我們提出了一種新型混合 CMOS 單元存儲器設計,通過結合 SRAM 和 eDRAM 單元,平衡了人工智能存儲器的性能、面積和能效。我們考慮了存儲器中一個 SRAM 和七個 eDRAM 單元的比例,以利用混合 CMOS 單元存儲器實現面積縮減。

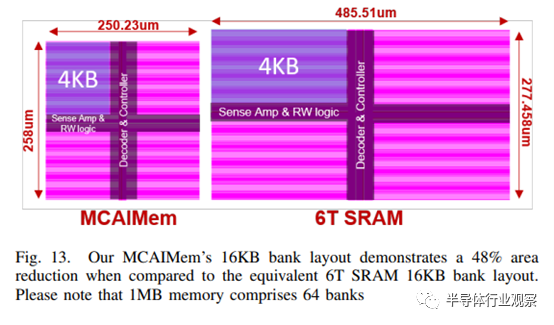

此外,我們還利用 DNN 數據表示的特點,集成了非對稱 eDRAM 單元,以降低能耗。為了驗證我們提出的 MCAIMem 解決方案,我們進行了大量仿真,并對傳統 SRAM 進行了基準測試。結果表明,MCAIMem 在面積和能效方面明顯優于這些替代方案。具體來說,與 SRAM 設計相比,我們的 MCAIMem 可以減少 48% 的面積和 3.4 倍的能耗,而且不會造成任何精度損失。

引言

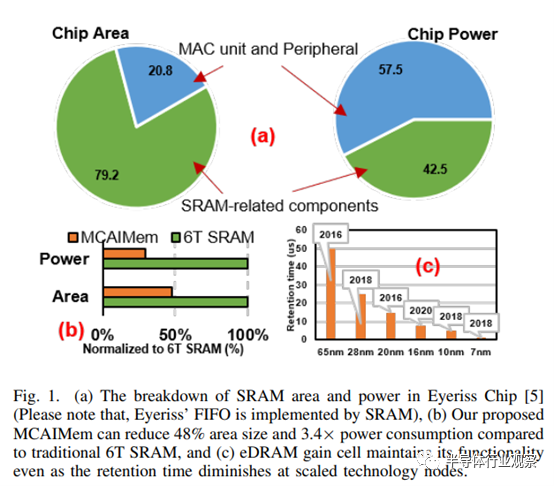

深度神經網絡(DNN)加速器已成為各種機器學習系統的重要組成部分。DNN 需要存儲大量參數才能實現高精度,因此對內存的要求很高。DNN 已在圖像識別、物體檢測、語言翻譯和自動駕駛等廣泛應用中證明了其有效性。最先進的 DNNs 需要數十億次運算和巨大的內存來存儲激活和權重,transformer的大小在兩年內增加了 240 倍就是證明 。專用內存導致尖端 DNN 加速器更多地使用較大的片上內存。例如,在 Eyeriss(如圖 1.(a) 所示)中,SRAM 占芯片面積的 79.2%,占功耗的 42.5%;在 Simba 等芯片設計中,SRAM 占芯片面積的 67%;而最新的晶圓級芯片可容納高達 18 GB 的片上存儲器。由此可見,使用片上 SRAM 存儲器需要更高的功耗和面積。

6T SRAM 長期以來一直是嵌入式存儲器的首選,因為它具有邏輯兼容的位單元、快速差分讀取和靜態數據保持能力。然而,由于其相對較大的單元尺寸以及在低工作電壓下讀寫的競爭要求,使得 6T SRAM 難以在先進的 CMOS 技術中擴展。

最近,非易失性存儲器因其單元尺寸小、單元泄漏低和快速讀取訪問操作而引起了研究界的興趣。早期的研究試圖用 ReRAM、FeFET 等非易失性存儲器取代片上 SRAM。然而,非易失性存儲器的寫入操作比讀取操作更慢,能耗更高。這會對 DNN 應用中的人工智能芯片性能產生負面影響,例如片上學習,片上讀取和寫入操作都是必須的。

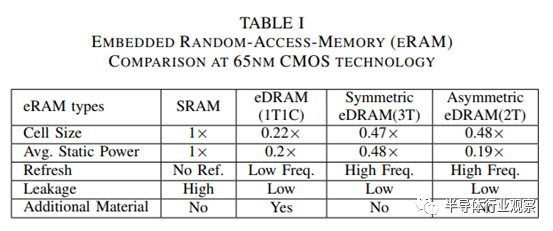

片上 SRAM 的另一個替代品是嵌入式動態隨機存取存儲器 (eDRAM)。表 I 比較了采用相同 65 納米低功耗 CMOS 工藝的不同嵌入式存儲器。我們發現,與 6T SRAM 相比,1T1C eDRAM(1 個晶體管和 1 個電容器)的位元密度高 4.5 倍,靜態功耗低 5.0 倍,甚至包括刷新功耗。這使得芯片尺寸更小、存儲器訪問速度更快、存儲器密度更高,這是在給定功耗限制條件下提高微處理器性能的最有效方法。

然而,非易失性存儲器和傳統 eDRAM(1T1C)需要復雜的制造工藝,因為它們需要專門的材料才能在晶圓上部署。

3T(三晶體管)和 2T(雙晶體管)CMOS eDRAM 增益單元設計是嵌入式動態隨機存取存儲器電路,與傳統 SRAM 相比,每個存儲單元使用的晶體管數量更少。因此密度更高,面積更小。3T/2T eDRAM 單元使用邏輯器件制造,因此只需進行極少的修改即可在標準 CMOS 工藝中構建。工業設計表明,使用三個晶體管可實現比 SRAM 高約 2 倍的位元密度。為此,eDRAM 增益單元(3T 和 2T)可在不改變制造技術的情況下減少片上 SRAM 面積。

如表 I 所示,與片上 SRAM 相比,eDRAM 增益單元在面積和能耗方面都有優勢。具體來說,與 SRAM 相比,2T eDRAM 的靜態功耗降低了 5.26 倍。然而,由于保持時間較短,使用 eDRAM 增益單元會導致大量刷新功耗,從而限制了 eDRAM 增益單元相對于片上 SRAM 的功耗優勢。因此,在人工智能芯片中實施 eDRAM 增益單元仍然是一個可行的考慮因素。

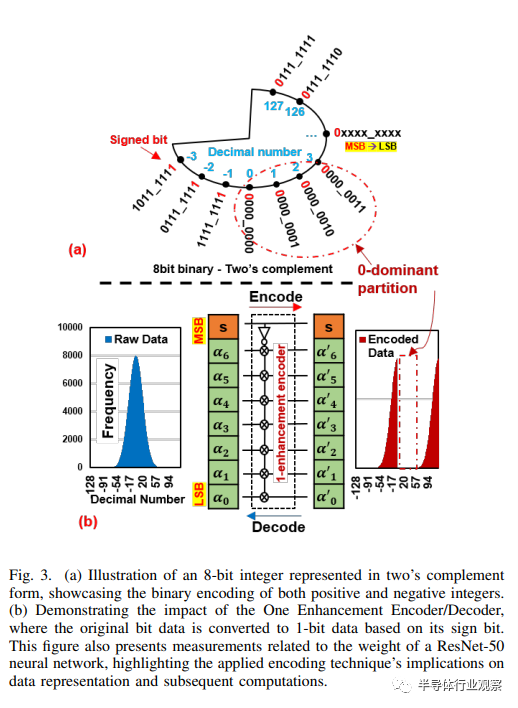

在深度學習應用中,INT8 已成為理想的數值表示方法,可在各種任務中保持精度。在作為 DNN 量化標準的 8 位整數格式中,發生在最重要位(MSB:Most Significant Bits)上的錯誤比發生在最不重要位(LSB:Least Significant Bits)上的錯誤權重更大。根據量化后 DNN 的 8 位整數數據往往聚集在零點附近的觀察。對于這種接近零的小整數,正值的 MSB 通常為 0,負值的 MSB 通常為 1。這種模式提供了通過位翻轉來增加正整數中 1 的數量的機會,從而在 DNN 數據中形成 1 的優勢。零位較多的 LSB 由于重要性較低,可以承受誤差,對最終精度的影響很小。

最近的一項研究提出了一種非對稱 DNN 數據編碼器,在保持 DNN 性能的同時,提高了 INT8 表示法中 0 位的頻率。這一想法可與使用 2T eDRAM 的片上數據存儲結合起來進一步利用,2T eDRAM 顯示了位-1 和位-0 之間數據保留的不對稱性,其中位-1 比位-0 提供更少的靜態和訪問能量。

將 6T SRAM/2T eDRAM 混合設計與一個增強型數據編碼器(增強 INT8 表示法中位-1 的普遍性)相結合,可以優化芯片的面積和能耗。因此,我們推出了 MCAIMem,一種基于 SRAM 和非對稱 eDRAM 的混合存儲單元,設計用于節省面積和能耗的片上人工智能存儲器。MCAIMem 適應性強,能夠滿足各種內存容量和性能需求,因此適用于從緊湊型邊緣設備到大型數據中心等各種人工智能應用。我們的貢獻如下:

據我們所知,我們首次提出了用于片上人工智能存儲器的 6T SRAM 和 2T eDRAM 混合單元。我們對 2T eDRAM 單元進行了修改,使其與 SRAM 單元保持一致,并提高了容量以延長保留時間。我們的混合存儲器單元大大減少了人工智能加速器的片上存儲器占用空間

我們提出的共電壓檢測放大器(CVSA:common voltage sense amplifier)可同時用于 SRAM 和 2T eDRAM 單元。通過控制 CVSA 的參考電壓,我們可以延長 2T eDRAM 的刷新周期,從而降低 MCAIMem 的動態刷新能耗。

我們利用了非對稱 2T eDRAM,其中存儲 bit-1 比 bit-0 消耗更少的能量。結合 DNN 數據的單增強編碼器/解碼器解決了 eDRAM 的可靠性問題,如刷新率和保持時間,從而顯著降低了 MCAIMem 的靜態功耗。

如圖 1.(b) 所示,我們的 MCAIMem 通過融合 6T SRAM 和 2T eDRAM 的優勢,創建了高性能、高能效和緊湊型混合存儲器解決方案,從而將片上人工智能存儲器系統的面積消耗減少了 48%,能效提高了 3.4 倍。

在第二節,我們介紹了增益單元 eDRAM、外圍電路以及 DNN 數據表示中使用的二乘法的背景信息。第三節詳細介紹了人工智能存儲器的綜合設計和運行機制。第四節討論了 MCAIMem 對人工智能應用的影響。第五節介紹了 45 納米工藝技術的硬件評估結果,包括電路和系統兩個層面。第六節探討了在人工智能應用中采用 eDRAM 的最新研究成果。最后,第七節得出結論。

背景

本節介紹了采用全 CMOS 技術和操作的 2T/3T eDRAM 增益單元電路設計的背景,回顧了 DNN 中的二乘表示法,并總結了為 AI 芯片設計混合 SRAM 和 eDRAM 單元存儲器所面臨的挑戰和要求。

1

嵌入式 DRAM 單元和傳感設計

3T 和 2T eDRAM:

與傳統 SRAM 相比,3T 和 2T eDRAM 設計每個存儲單元使用的晶體管更少,因此面積更小,密度更高,位元密度大約提高了 2 倍。最近的研究表明,eDRAM 的增益單元目前正在積極開發中,最新的實現采用了 7-10 納米 FinFET 技術。如圖 1.c 所示,在休眠模式下,eDRAM 單元的漏電流低于 SRAM,從而降低了靜態功耗,包括漏電功耗和刷新功耗。

eDRAM 單元的單元寫入邊際優于 SRAM,因為在增益單元(gain cell)中,存取器件(access device)和交叉耦合鎖存器(cross-coupled latch)之間不存在競爭。然而,傳統增益單元的存儲電容較小,漏電流在工藝-電壓-溫度(PVT:Process-Voltage-Temperature)變化下呈指數變化,導致刷新功耗較高和/或讀取電流較小,因而保持時間較短。前者源于更頻繁的刷新操作,后者則源于更快的單元電壓損耗。

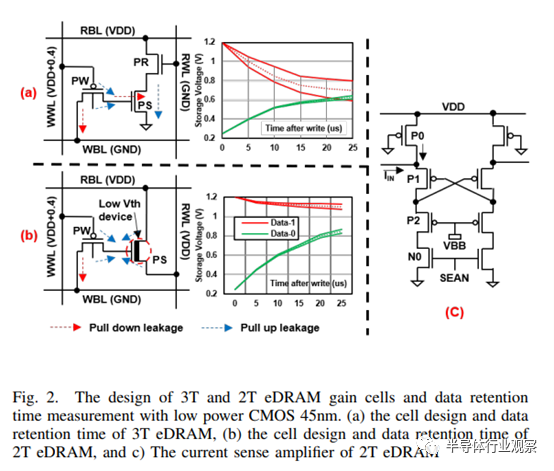

要理解 eDRAM 增益單元,可以考慮傳統 3T 增益單元的基本保持特性。在圖 2.(a) 所示的 3T NMOS 單元中,PW 代表寫入訪問器件,PS 代表存儲器件,PR 代表讀取訪問器件。在 3T eDRAM 中,PS 的柵極電容用于存儲比特-1 或比特-0 表示的電荷電壓。與 1T1C eDRAM 相比,PS 的容量較小。因此,3T 增益單元采用解耦讀寫結構,讀取數據時使用獨立的讀字線(RWL)和讀位線(RBL),寫入數據時使用寫字線(WWL)和寫位線(WBL)。這提高了位元設計中的讀寫邊際和靈活性,使增益單元在未來的技術節點中能夠很好地擴展。

在數據保留模式下,PW 和 PR 將被停用,使存儲節點處于浮動狀態。周圍器件的次閾值、柵極和結漏會導致浮動電壓隨時間變化。數據保留時間取決于進入存儲節點的總漏電流。在 SPICE 中進行的蒙特卡洛仿真,顯示了采用低功耗 CMOS 45nm 技術的 1 Mb 存儲器宏中單元與單元之間的變化,如圖 2.(a) 所示。當讀取參考偏置電平為 0.65 V 時,位 1 電壓和位 0 電壓會在相同的保持時間內接近讀取參考偏置電平。

創新的 2T 增益單元設計采用了更少的晶體管,其特點是由 RWL 驅動的單個高驅動電流 NMOS 讀取器件和一個 PMOS 寫入器件,可保持臨界 bit-1 電壓在 VDD 附近。圖 2.(b) 展示了 2T eDRAM 單元,其結構和工作原理與 3T eDRAM 有很大不同。之前的 3T eDRAM 單元使用 PMOS 器件作為寫入訪問晶體管,通過 PMOS 柵極重疊和結點泄漏來抵消 NMOS 柵極泄漏,從而延長單元保持時間。

然而,在 PVT 變化下,漏電補償證明是不夠的,因為 NMOS 存儲設備的反相溝道柵極漏電在比特-1 中占主導地位,如圖 2(a)所示。

在圖 2.(b) 所示的 2T eDRAM 單元中,讀取訪問晶體管由 RWL 信號取代,預充電電平設置為 VDD。存儲晶體管基本上處于關閉狀態,因此其柵極漏電流微不足道。由于讀取路徑不存在閾值下漏電,因此建議采用低 Vth 晶體管,以進一步提高讀取速度。在 0.65V 讀取參考偏置下,存儲單元表現出不對稱性,位-1 不會改變,而位-0 容易翻轉為位-1。均衡的 P 和 N 擴散密度是所提出的 2T 不對稱單元的另一個優點。本文旨在利用這一特性最大限度地減少靜態和動態能耗,因為位-0 的翻轉需要更多的能量。

2T eDRAM 檢測放大器:

在增益單元中,NMOS 柵極電容用于存儲電荷,使其對電壓變化非常敏感。直接訪問 NMOS 可能會導致存儲位翻轉。因此,傳統增益單元需要一個電流檢測放大器來檢測存儲節點。對于 2T 單元設計,RBL 必須表現出有限的擺幅,以避免因未選擇單元的漏電流而導致讀取失敗。

然而,較小的電壓擺幅會導致較差的讀取感應裕度。非對稱 2T 增益單元利用低 Vth 讀取器件實現更快的讀取速度,同時將速度關鍵的第 1 位電壓保持在 VDD 附近,從而使情況更加復雜。為解決這一問題,在 2T eDRAM 設計中采用了電流模式檢測放大器 (C-S/A),在檢測期間將 RBL 電壓保持在 VDD 附近,并允許將多個低 Vth 單元連接到單個 RBL。

如圖 2.(c) 所示,C-S/A 由一個交叉耦合 PMOS 鎖存器 (P1) 和一個偽 PMOS 二極管 (P2) 組成,偽 PMOS 二極管由負電源 VBB 驅動,而 VBB 在芯片上很容易獲得,可用于欠驅動 WWL。負 WWL 是 PMOS 器件向單元寫入比特-1 而不產生閾值電壓損耗的必要條件。兩個 PMOS 對(P1 和 P2)都在飽和模式下工作,從而提高了匹配度。不過,這種 C-S/A 設計僅用于讀取 2T eDRAM 單元中的存儲位,因為位-0 仍需要定期回寫以避免位翻轉。

因此,寫操作需要一個額外的寫電路,由于 2T eDRAM 單元尺寸小,讀/寫電路需要大量的開銷,因此導致效率低下。在這種 2T eDRAM 中。傳統的 2T eDRAM 只能利用 2T eDRAM 的非對稱特性,通過 C-S/A 在較小的電壓擺幅下進行感應,而我們的方法則不同,它通過電壓感應擴展了讀取過程。在我們的方案中,存儲電荷的電壓裕量更大,位 0 為 0 至 0.8V,位 1 為 0.8 至 1.0V。更深入的討論見第 III-B 節。

2

DNN 表示中的二乘補法和一增強法

在深度神經網絡(DNN)中,數據表示法的選擇對精度、計算復雜性和功耗有很大影響。二進制表示法是 DNN 中符號整數值的常用格式,因為它簡化了算術運算,尤其是乘法和加法運算。這種格式將負數表示為相應正數二進制表示的二進制補碼,從而簡化了硬件實現,降低了電路復雜度。

目前,INT8 被認為是 DNN 推理的最佳表示形式,能保持精確的結果。8 位二進制量化技術已被廣泛采用,并優于其他量化技術。在這項工作中,我們選擇 8 位二進制作為設計片上緩沖器的基準。

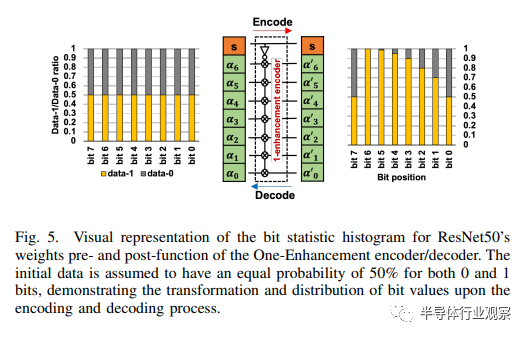

如圖 3.(a)所示,第一位(即有符號位:signed bit)決定數字是正數還是負數。正如 ZEM 所指出的,DNN 數據的范圍通常很窄(例如 [-50,50])。接近零的負值具有 1 主導位,而相應的正數則表現為 0 主導位。轉換 0 主位時,需要根據帶符號位翻轉所有數據位。如圖 3.(b) 所示,構建編碼器只需要一個 INV 和七個 XOR 門,就能將原始數據轉換為 1 主位數據。單增強編碼器將 DNN 數據編碼為 1 主位數據。解碼器根據簽名比特翻轉編碼數據,從而重建原始數據。

與 ZEM 不同的是,我們的工作旨在創建 1 主導數據,以減少混合單元存儲器設計在存儲 DNN 數據時的刷新和靜態能耗。在本文中,存儲在片上存儲器中的 DNN 數據在計算前要經過編碼和解碼。

3

設計挑戰和要求概述

我們在考慮單增強編碼器/解碼器的要求時,有符號位充當控制位,決定何時執行編碼或解碼操作。保護簽名位不受錯誤影響至關重要。在本文中,我們利用 2T eDRAM 來提高面積和能效。然而,由于單元電壓損耗加快,2T eDRAM 需要更頻繁的刷新操作。為了確保簽名位的安全,我們將其分配到 6T SRAM,并將其余位映射到 2T eDRAM。因此,在設計混合 SRAM 和 eDRAM 單元時,我們需要應對以下挑戰:

兼容性:確保在單一存儲器架構中無縫集成 SRAM 和 eDRAM 單元,并保持與現有制造工藝的兼容性。

密度和面積效率:在不犧牲性能或增加芯片復雜性的情況下,實現高存儲器密度和面積效率。

保持時間和刷新率:解決 eDRAM 單元固有的保持時間限制,優化刷新率,在不影響數據完整性的前提下最大限度地降低功耗。

可擴展性:開發可輕松擴展的存儲器架構,以適應從邊緣設備到數據中心的各種人工智能應用對存儲器容量和性能的不同要求。

可靠性:保證混合內存設計在不同運行條件下的穩健性和可靠性,尤其是在涉及頻繁讀寫操作的人工智能工作負載中。

在本文中,我們將解決上述問題,并介紹適合人工智能應用的高效片上存儲器設計。更多詳情將在后續章節中介紹。

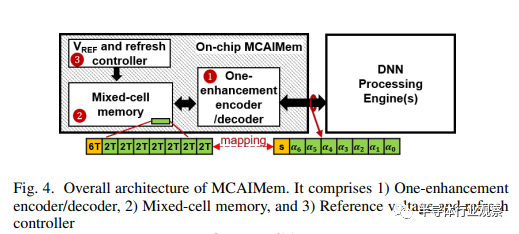

我們的MCAIMEM

本節將介紹 MCAIMem,這是我們專為人工智能芯片開發的創新型片上混合單元存儲器設計。如圖 4 所示,MCAIMem 由三個關鍵部分組成:

混合 SRAM/eDRAM 單元存儲器,包括映射方案和電路相關設計;

一個增強編碼器/解碼器;

負責延長刷新操作時間的參考電壓控制器。

片上 MCAIMem 是人工智能加速器的緩沖器,用于存儲計算過程中的權重和激活。從片外 DRAM 傳輸過來的數據保留在 MCAIMem 中,隨后由 DNN 處理引擎使用,該引擎可以是傳統的 CPU/GPU,也可以是合成陣列或內存計算(CIM)架構。

入站/出站(Inbound/outbound)數據必須通過一個增強編碼器模塊進行編碼/解碼,這將在第 III-A1 節中討論。編碼后的數據將保存在我們的混合單元存儲器設計中,這是 6T SRAM 和 2T eDRAM 的組合,旨在最大限度地減少片上存儲器的面積占用。有關混合單元存儲器設計的更多細節將在第 III-B 節中介紹。由于包含 2T eDRAM,因此需要進行定期刷新操作。刷新控制器將在第 III-C 節中討論。

1

一次增強編碼器/解碼器和數據映射

1) 一次增強編碼器/解碼器模塊:要在片上 MCAIMem 中存儲數據,首先需要使用一次性增強編碼器/解碼器模塊對數據進行編碼。在 45 納米技術節點上進行合成后,我們對一次增強編碼/解碼模塊進行了實驗評估。經測量,該模塊的功耗為 1.35×10-2mW,僅占內存總功耗的 0.007%,因此其影響可以忽略不計。在面積方面,該模塊僅占 35.2um2 的面積,與 108KB 的內存大小相比,僅占 0.004%。這些指標表明,該模塊對功耗和空間需求的影響微乎其微,尤其是與大量的存儲單元相比。此外,與編碼器/解碼器相關的延遲僅為 0.23ns。即使時鐘周期為 1ns(對應于 1GHz 的時鐘頻率),也有 0.67ns 的寬裕延遲,可確保不會出現違反時序的情況。因此,編碼器/解碼器的延遲不會對系統的整體性能構成威脅。

如第 II-B 節所述,輸入數據在存儲到我們的混合單元存儲器之前,會根據其符號位進行翻轉。通過將原始比特數據增強為通常為 1 位的值,可以降低存儲器的總體能耗,因為單元經過優化,可以更高效地存儲和訪問 1 位數據。可以利用二進制表示法中的帶符號位來進行這種增強,因為根據數字的符號,帶符號位要么是 0,要么是 1。編碼器對輸入數據進行修改,使其出現更多的 1 位,而解碼器則逆轉這一過程以恢復原始數據。例如,剪枝會導致 20-80% 的數據為 0 。由于大部分數據接近于 0,因此在不犧牲數據完整性或準確性的情況下,增強表示以產生更多比特-1 值,可以提高內存系統的能效。

如圖 5 所示,第 6 位、第 5 位和第 4 位大多轉換為位-1,因此將它們映射到 2T eDRAM 單元的效率很高。第 0 位、第 1 位、第 2 位和第 3 位繼續保持相當數量的位-0。使用 2T eDRAM 存儲這些比特時,可能會出現保留錯誤。不過,由于 2T eDRAM 的非對稱性質,只有從 0 到 1 的翻轉錯誤才被視為保留錯誤。這些錯誤可能會影響 DNN 應用的輸出。為確保這些錯誤不會對 DNN 應用結果產生不利影響,我們將在第 IV-A 節評估其影響。

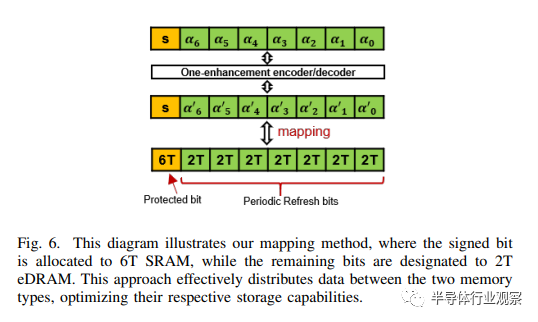

2) 混合單元映射方案:如第 II-A 節所述,使用 2T eDRAM 可能會因保留時間短而導致錯誤。基于單增強編碼器/解碼器,控制位至關重要,因為控制位出錯會導致其余所有位出錯。因此,在 2T eDRAM 中存儲 DNN 數據時,我們需要確保控制位受到良好保護,同時允許其余位近似。建議的位映射如下:

將控制位映射到 6T SRAM,

將 7 個最小有效位 (LSB) 映射到 2T eDRAM。

如圖 6 所示,一個 6T SRAM 單元分配給帶符號/控制位,而下面的 7 個位則映射到 2T eDRAM 單元。輸入的 DNN 數據首先由單增強編碼器編碼,然后存儲在混合單元陣列中。簽名位/控制位安全地存儲在 6T SRAM 中,而其余位則根據簽名位翻轉并存儲在 2T eDRAM 中,如圖 6 所示。

這種存儲器映射方法確保了 6T SRAM 中簽名/控制位的安全性,同時要求對其余位進行定期刷新操作,以防止數據翻轉 ping。這一機制對于保持比特-1 在大多數 DNN 數據(約 80%)中的主導地位至關重要。由于 2T eDRAM 的特性,存儲比特-1 比存儲比特-0 消耗更少的能量。因此,通過將單增強編碼器與非對稱 2T eDRAM 結合使用,可以實現靜態節能。

2

混合單元(mixed-cell)存儲器設計

如映射方法所述,我們的混合單元存儲器設計由一個 6T SRAM 單元和七個 2T eDRAM 單元組成。為了集成這些單元,我們需要修改 6T SRAM 和 2T eDRAM 的電路設計。在這項工作中,我們建議對 2T eDRAM 進行修改,并對 6T SRAM 稍作改動。此外,我們還提出了一種可同時用于 6T SRAM 和 2T eDRAM 的電壓檢測放大器。這些調整的細節將在下面的小節中討論。

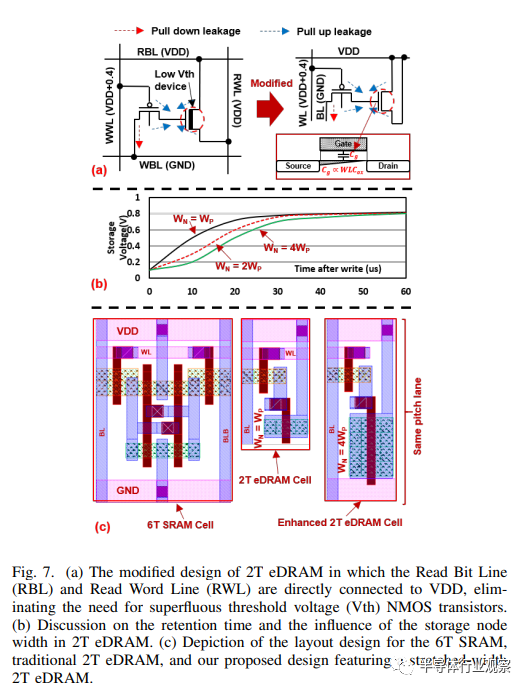

1) 增強非對稱 2T eDRAM 單元的保持時間:在結合 6T SRAM 和 2T eDRAM 的設計時,我們遇到了間距通道不匹配的挑戰,并且需要同時適用于 6T SRAM 和 2T eDRAM 的混合感應放大器。這是因為與 6T SRAM 相比,2T eDRAM 的尺寸要小得多。為了解決間距通道問題,我們調整了 2T eDRAM 存儲晶體管的尺寸。如圖 7.(c) 所示,在設計 6T SRAM 和 2T eDRAM 的單元布局時,可能會出現間距通道不匹配的情況。與 SRAM 單元相比,2T eDRAM 單元僅占 60% 的面積。因此,我們可以將 2T eDRAM 的寬度增加到 4 倍,以便與 6T SRAM 單元的設計保持一致。

如第 II-A 節所述,2T eDRAM 由兩個主要部分組成:存取晶體管和存儲節點。如圖 7(a)所示,存儲節點中的柵極電容(Cg)存儲代表比特-1 或比特-0 的電荷電壓。NMOS 柵極的容量定義為 Cg ∝ W LCox。通過增加 NMOS 柵極的寬度,我們不僅提高了存儲節點的容量,還改善了 2T eDRA 的保持時間。圖 7.(b) 展示了使用 CMOS 45 納米技術設計的 eDRAM 的 SPICE 仿真;當存儲位 0 時,保持時間顯著延長。例如,當存儲節點寬度增加 4 倍時,電荷從 0.18V 變為 0.8V 所需的時間增加了一倍。

此外,增加存儲節點的容量還能帶來額外的好處。它使 2T eDRAM 更能抵御讀取干擾效應。這樣,我們就可以移除 2T eDRAM 中的 RWL 和 RBL,將它們直接連接到 VDD。現在,NMOS 晶體管只起到存儲電容器的作用。來自存儲節點 VDD 的柵極漏電以及寫入晶體管的柵極漏電和結漏電將存儲節點的電荷補充到位 1。因此,2T eDRAM 的非對稱特性保持不變。

通過這種設計,我們預計位 1 的存儲無需保留時間,而位 0 則需要定期刷新操作來保持其放電狀態。因此,我們可以將存儲節點的漏極和源極直接連接到 VDD,如圖 7.(a) 所示。在本研究中,我們利用上拉漏電流來維持 "1 "位并存儲 "0 "位,因此無需改變低電壓閾值 (LVT) 器件通常需要的摻雜和柵極氧化物厚度。這種方法使此類修改變得沒有必要。

2) 混合存儲單元中 SRAM 單元設計的調整:我們對 2T eDRAM 的存儲節點進行了重大修改,但保留了傳統 2T eDRAM 設計中的 PMOS 接入晶體管。做出這一決定是為了確保只有第 0 位發生變化,而第 1 位保持不變。為了盡量減少 PMOS 的閾下漏電,并確保下拉漏電路徑始終低于上拉漏電路徑,我們采用了 VDD+0.4V 電壓。不過,使用 PMOS 晶體管作為存取晶體管可能與 6T SRAM 中存取晶體管的設計相沖突。

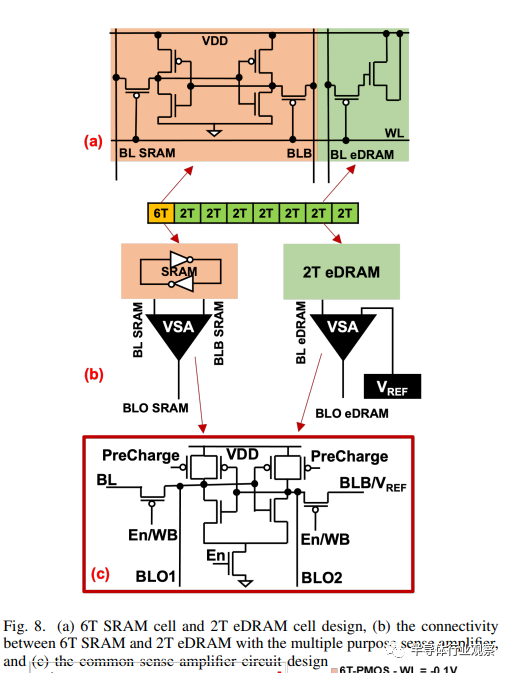

為解決這一問題,我們對 SRAM 單元設計進行了細微修改,如圖 8.(a) 所示,將 SRAM 中的訪問晶體管也改為 PMOS。通過調整兩個存儲單元中的訪問晶體管類型,我們促進了 6T SRAM 和 2T eDRAM 設計的整合,同時保持了所需的功能和性能。

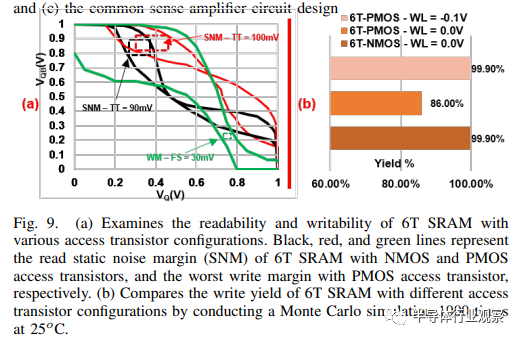

通過修改 6T SRAM 位單元中的存取晶體管(參見圖 9.a),我們發現使用 pMOS 存取晶體管(紅線)時,讀取靜態噪聲裕度 (SNM) 為 100mV,而使用 nMOS 晶體管(黑線)時為 90mV。不過,pMOS 晶體管的寫入能力較低。隨著節點 QB 放電和 Vgs 下降,當 QB 降到閾值電壓以下時,晶體管會減弱并關閉,從而導致 FS 角的寫入裕量受限為 30mV(綠線)。如圖 9.b 所示,在字線 (WL) 上施加 -0.1V 電壓時,pMOS 存取晶體管的寫入良率會增加,達到 nMOS 晶體管的寫入良率。

3) 用于 SRAM 和 2T eDRAM 的電壓檢測放大器電路(Voltage sense amplifier circuit):如第 II-A 節所述,2T eDRAM 取消了讀寫路徑,這意味著讀寫操作需要單獨的電路。此外,2T eDRAM 的保留時間較短,需要定期刷新操作來維護數據。設計混合單元的主要挑戰之一是提供同時滿足 6T SRAM 和 2T eDRAM 的混合感應放大器。

在 2T eDRAM 中,需要一個電流檢測放大器來檢測讀取路徑中的微小增益,而不會干擾存儲節點中的數據。但是,刷新操作要求將讀取的數據寫回存儲節點,從而導致大量的外圍電路開銷。如第 III-B1 節所述,通過將 2T eDRAM 的寬度尺寸增加 4 倍,該設計可以抵御讀取干擾。因此,我們建議為 6T SRAM 和 2T eDRAM 安裝一個電壓檢測放大器,如圖 8(c)所示。這使得 2T eDRAM 和 6T SRAM 的讀寫操作完全相同。6T SRAM 和 2T eDRAM 連接到電壓檢測放大器時的主要區別在于,6T SRAM 的 BL 和 BLB 都是連接的。相反,對于 2T eDRAM,只有一個 BL 連接到感應放大器,而感應放大器的 BLB 連接到參考電壓 (VREF),如圖 8(b)所示。

這不僅簡化了讀寫操作,而且使用電壓檢測放大器還能在讀取操作過程中將數據寫回 2T eDRAM 存儲節點。這就簡化了刷新過程,因為只需要一次讀操作就能完成刷新,而不是標準 2T eDRAM 設計中傳統的一連串讀和寫操作。

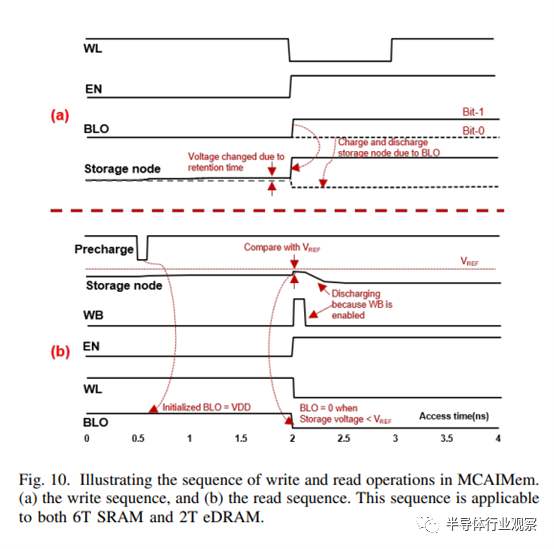

4) 電壓檢測放大器的讀寫操作:圖 10.(a) 展示了使用電壓檢測放大器 (VSA) 的寫操作。寫入過程首先是向位線輸出端 (BLO1) 施加電壓,然后通過使能信號 (EN) 啟用電壓檢測放大器。這一操作會導致位線充電或放電。當字線 (WL) 被激活時,位線電壓會改變 6T SRAM 或 2T eDRAM 中的數據。對于 SRAM,6T SRAM 中的 PMOS 存取晶體管必須弱于存儲節點,寫入操作才能成功。對于 2T eDRAM,存儲節點的充放電過程與 SRAM 類似。

圖 10.(b) 顯示了 VSA 的讀操作。為初始化讀取操作的感測放大器,啟用了預充電,將 BLO1 和 BLO2 充至 1。對于 2T eDRAM,可將參考電壓施加到位線柵 (BLB)。該參考電壓 (VREF ) 用于比較存儲節點的電壓,并確定 BLO1 的數據輸出。一旦感測放大器中的 WL 和 EN 啟用,存儲節點將對位線進行充電或放電。如果位線(BL)電壓大于檢測放大器內的 VREF,BLO1 將被設置為 1;如果 BL 電壓小于 VREF,BLO1 將被設置為 0。因此,必須禁用感測放大器中的 WB,以便為 2T eDRAM 中的存儲節點充電。對于 6T SRAM,VSA 的 BLB 連接到 SRAM 單元的 BLB。

基準電壓和刷新控制器

如圖 10(b)所示,我們改進的 2T eDRAM 的讀操作允許停用回寫(WB:write-back)信號。由于位線電壓的存在,存儲節點可以充電或再充電,因此 MCAIMem 的刷新操作與執行讀操作一樣簡單。

我們的混合單元存儲器設計采用了 2T eDRAM,它需要周期性刷新操作。我們選擇了 [3] 中所述的標準定期刷新方法,也稱為全局刷新操作。在這種方法中,必須在 12.57us 內對 MCAIMem 的每一行執行刷新操作。詳細地說,普通刷新周期間隔是用刷新時間除以行數計算得出的。由于采用了單增強編碼器,用于存儲 DNN 數據的靜態功耗大大降低,但 bit-0 仍需要頻繁刷新操作,以確保 DNN 數據的安全。該模塊負責確定 2T eDRAM 檢測放大器的參考電壓,這有助于延長刷新周期,降低 DNN 數據中 0 位的動態刷新能量。參考電壓的決定及其詳細討論見第 IV-B 節。

減輕 MCAIMEM下的DNN精度損失

在本節中,我們將探討 MCAIMem 對 DNN 應用結果的影響。首先,我們將研究保留誤差對 DNN 性能的影響。其次,我們將討論為人工智能芯片上的節能 DNN 應用延長刷新周期的方法。

1

保留誤差對人工智能芯片結果的影響

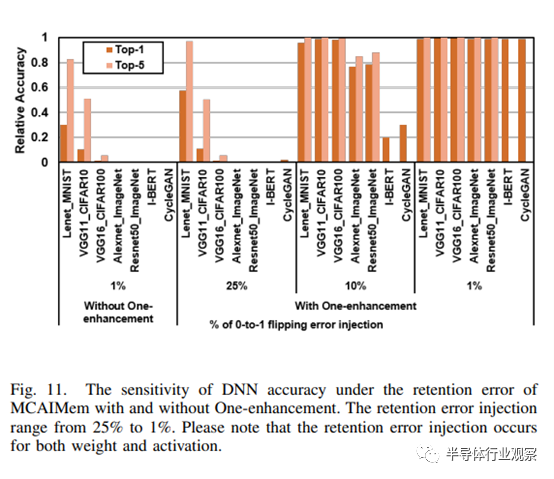

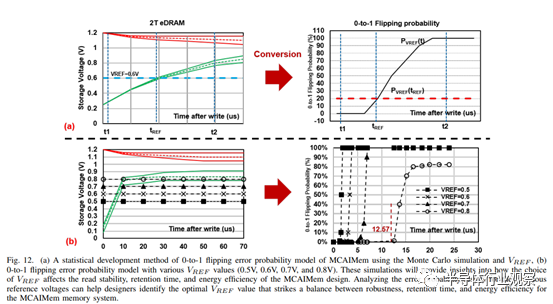

DNN 以其魯棒性而著稱,其誤差通常較小,且僅發生在 LSB 中。在 MCAIMem 中,我們的內存配置由一個 SRAM 和七個 2T eDRAM 混合組成。在混合單元存儲器設計中,潛在錯誤主要來自 2T eDRAM 的保持錯誤,因此有必要探討其對 DNN 應用的影響。如圖 12(b)所示,在 12.57μs 之前,2T eDRAM 在不到 1%的情況下會發生位-0 到位-1 的翻轉,而在 13μs 之后,超過 25%的情況下會發生位-0 到位-1 的翻轉,沒有觀察到位-1 的錯誤。因此,我們采用了錯誤注入方法來評估翻轉錯誤率,并確定其對 DNN 應用準確性的影響,進而影響 MCAIMem 的刷新周期。

值得注意的是,在本研究中,保留時間問題僅限于 2T eDRAM,不影響 SRAM。因此,我們故意在每次計算之前,將誤差注入 DNN 數據的權重和激活中,使誤差產生累積效應。我們設計了兩種方法:首先,我們將誤差注入 DNN(不包括單增強編碼器/解碼器),在這種情況下,只有 0 位會按照預定的誤差率翻轉。或者,在應用一次增強編碼器后、解碼數據前,向第 0 位注入錯誤,翻轉錯誤率從 1%到 25%不等。

我們利用 MNIST、CIFAR10、CIFAR100 和 ImageNet 等數據集,對 LeNet、VGG11、VGG16、AlexNet 和 ResNet50 等多個 CNN 進行了模擬。在語言建模方面,我們使用了 I-BERT(BERT 的整數版本)和 GLUE 數據集 。在生成建模方面,我們使用了 CycleGAN 的量化版本和 horse2zebra 數據集。這種綜合評估可以揭示不同的保留誤差水平對 DNN 準確性的影響程度以及 One-enhancement 方法的有效性。對于指定的每個誤差率,可以比較使用 MCAIMem 和不使用 One 增強編碼時 DNN 的準確性。

值得注意的是,就 GAN 而言,輸出的準確性無法直接測量。因此,我們依靠平均相對誤差來量化我們的 GAN 與原始模型之間的差異。這種比較有助于評估 "一個增強 "技術在多大程度上減少了保留誤差對 DNN 精度的影響。

圖 11 顯示,如果不應用 "一個增強 "編碼器/解碼器,各種網絡的 DNN 精度都會驟降為零。造成精度下降的原因是,SRAM 中只有簽名位受到保護,而其他主位仍然容易受到保留誤差的影響。然而,在實施單增強編碼器/解碼器后,絕大多數 MSB 位都變成了 1 位,不易發生翻轉,而少量保留 0 位的 LSB 位可能會遇到保留錯誤。因此,AlexNet/ResNet50 上的 ImageNet、I-BERT 上的 GLUE 和 CycleGAN 上的 horse2zebra 可以容忍高達 1% 的注入誤差。此外,MNIST 和 CIFAR10/100 數據集的抗錯能力更強,可容許高達 25% 的保留誤差。當采用一次增強技術時,MSB 中的顯著位錯誤會被引入權值和激活值,這明顯降低了推理任務的準確性。不過,事實證明這種方法有利于延長 eDRAM 的保留時間。雖然會引入位錯誤,但這些錯誤主要影響 LSB,因此不會明顯影響推理過程的準確性。

在 DNN 應用中,結果是決定人工智能性能的關鍵。與硬件性能和能耗相比,保持 DNN 輸出的準確性是一個更重要的因素。因此,我們的 MCAIMem 應符合這些要求,并在混合單元設計中考慮最多 1% 的最大保留誤差。

2

利用自適應 VREF 延長刷新周期

在第 II-A 節中,我們解釋了隨著時間的推移,比特-0 趨向于翻轉為比特-1,只有比特-0 會出現保留誤差。為了使用單增強編碼器保持 DNN 輸出的準確性,允許的最大保持誤差為 1%。因此,我們需要根據比特-0 的保持時間建立誤差模型,從而確定一個能保持 DNN 輸出精度的刷新時間。

在 2T eDRAM 中,泄漏電流會導致比特-0 在特定持續時間后傾向于翻轉到比特-1。根據 2T eDRAM 的訪問時間,這將導致位 0 讀數的變化。為了計算 0 到 1 的翻轉概率,我們執行了蒙特卡羅模擬,生成了大量存儲 bit-0 的 2T eDRAM 的變化樣本。然后,考慮到訪問時間和特定參考電壓 (VREF),我們計算與 2T eDRAM 樣本總數相關的翻轉比特數,如圖 12(a)所示。這一錯誤翻轉模型有助于確定最佳 VREF,從而在 MCAIMem 中實現穩健性、保持時間和能效之間的平衡。

我們在 85℃ 的溫度下進行了 100,000 次蒙特卡羅模擬,這反映了典型的臺式機和服務器工作環境,溫度范圍在 25-85℃ 之間 [24]。這包括評估存儲節點中的數據移動,并在 0 到 20 微秒之間改變訪問時間,同時讀取數據。圖 12.(b) 顯示,當 VREF 為 0.5 時,1% 的翻轉概率在 1.3 微秒時啟動。相反,當 VREF 為 0.8 時,1% 的翻轉概率在 12.57 微秒時開始。從圖中可以看出,翻轉概率斜率很陡,這意味著根據特定的 VREF 來延長刷新周期所能降低的刷新功耗微乎其微。不過,調整 VREF 可以延長所需的刷新周期。因此,我們選擇 0.8V 的 VREF 來最大限度地延長比特-0 的刷新周期,并最大限度地減少混合單元存儲器中的動態刷新操作。

評估

我們的研究主要涉及用于服務器和臺式機應用的人工智能芯片,工作溫度范圍為 25 攝氏度至 85 攝氏度。我們特別沒有考慮電壓變化,而是通過蒙特卡洛仿真集中研究工藝變化。在本節中,我們將討論分為兩個主要部分。首先是電路仿真,然后是系統仿真。后者特別探討了由我們提出的 MCAImem 設計驅動的 DNN 應用。

1

電路評估

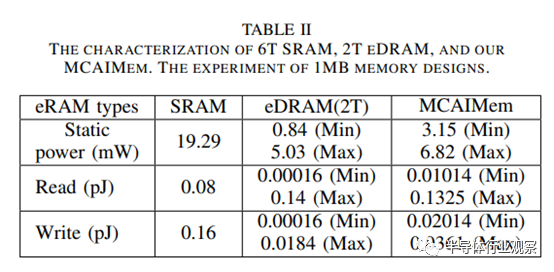

在電路評估中,我們使用 CMOS 45nm 技術創建了 1MB 6T SRAM、2T eDRAM 和混合單元存儲器的布局。我們根據布局尺寸計算這些嵌入式 RAM 的芯片面積,并進行比較。此外,我們還提取了這些存儲器的 SPICE 模型,并進行了后仿真,以分析每種存儲器類型的靜態功耗、讀取和寫入操作。表 II. 總結了特性分析結果。

如圖 13 所示,與單獨的 SRAM 存儲器相比,SRAM 和 eDRAM 混合設計的面積縮小了 48%。在電路仿真過程中,2T eDRAM 的非對稱特性會影響存儲數據值的靜態功耗和訪問功耗。當所有位數據都為 1 時,eDRAM 的功耗較低,因為當存儲節點位于 VDD 時,漏電流大大降低。從 VDD 到存儲節點的柵極漏電極小,現在的主要漏電是 PMOS 的次閾值電流。由于我們對 PMOS 存取晶體管的柵極施加了 0.4V 的三角電壓,因此該電流很小。如果所有比特數據都為 0,則來自 VDD 的較高柵極漏電流會試圖將存儲節點充電到比特-1。因此,單增強技術增加了位-1 的位數,這對降低 2T eDRAM 的靜態功耗至關重要。

與 2T eDRAM 相比,我們的混合單元存儲器包括一個 6T SRAM 和七個 2T eDRAM。靜態功耗來自 SRAM 和 eDRAM,但與單獨的 SRAM 相比,可降低 3-6 倍。在讀寫操作方面,6T SRAM 大部分是平衡的,而 2T eDRAM 仍然顯示出不對稱的特性。讀取位-1 時,初始 BL 為 VDD,因此感應放大器沒有變化,從而實現了低能耗。相反,當讀取位-0 時,存儲節點必須重新充電至 0,來自存儲節點的電流是造成能耗的主要因素。

2

系統評估

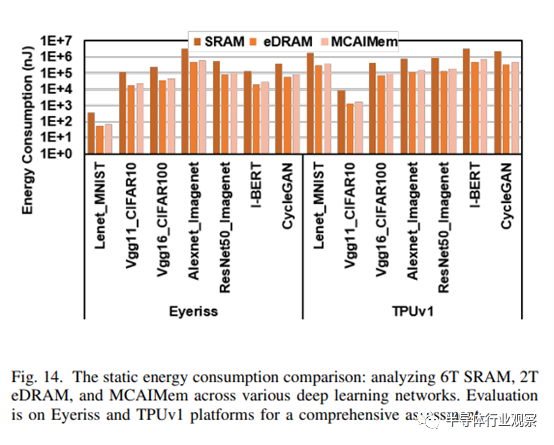

本評估旨在通過模擬 LeNet、VGG11、VGG16、AlexNet 和 ResNet-50 等不同 CNN 網絡,以及 MNIST、CIFAR10/100 和 ImageNet 等數據集,確定 MCAImem 對 DNN 應用的影響。此外,我們還對語言網絡 I-BERT 和生成網絡 CycleGAN 進行了模擬。考慮到 Eyeriss 和 Google TPUv1 的配置,我們修改了 SCALE-Sim ,以估算每個內存設備的靜態和動態能耗。為了使我們的功耗模型適應各種設備配置,我們根據它們的內存要求進行了調整。具體來說,對于需要 108KB SRAM 的 Eyeriss,我們修改了嵌入式 RAM 功率模型,將其減少到原來 1MB 內存設備配置的十分之一。

相反,對于需要 8MB 的 Google TPUv1,我們將嵌入式 RAM 功率模型提高了 8 倍。關于 RRAM 模型,我們采用了 [34] 中的模型,假設權重和激活都利用 RRAM 作為片上緩沖區。這反映了與 Eyeriss 和 TPUv1 配置相關的內存大小調整。此外,考慮到 RRAM 的非易失性內存可以在不丟失數據的情況下切換開關,我們沒有將靜態功耗歸因于 RRAM,而只考慮了每字節的讀寫能耗。

在這項以仿真為中心的研究中,我們提取了每種設備配置的計算時間,并假定其時鐘頻率為 100 MHz。在確定每種存儲器類型的計算時間后,我們應用各自的功率模型計算最終的靜態和動態能量。我們采用 6T SRAM 和傳統 2T eDRAM(不含一個增強編碼器/解碼器)作為基準比較。我們的評估嚴格按照片上緩沖性能進行,有意忽略了與 MAC 操作相關的能耗。我們選擇的時鐘頻率為 100MHz,與人工智能加速器中觀察到的最慢運行時鐘頻率一致--以 100MHz 的 Eyeriss 和 700MHz 的 TPUv1 為例。所選的時鐘頻率不僅決定了跨層訪問和保持內存的時間,而且由于我們使用的是 eDRAM,必須進行刷新操作以保護數據,因此這一時鐘頻率也是必不可少的。因此,時鐘頻率對于估算人工智能加速器計算過程中所需的刷新操作次數至關重要。

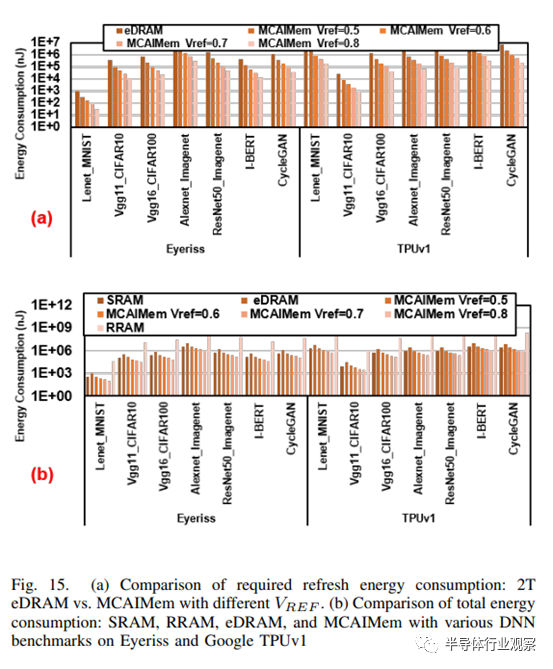

利用 SCALE-SIM 技術,我們可以量化時鐘周期的數量。由于采用了合成陣列設計,每個時鐘周期都能同時促進 MAC 和內存訪問,從而簡化了片上內存訪問的統計。圖 15 描述了可實現的最小功耗節省。有趣的是,由于采用了更快的時鐘頻率,每層的數據保留時間被截斷,這可能會導致計算進行時刷新操作的次數減少,從而導致功耗降低。

在靜態功耗方面,SRAM 的能耗高于 2T eDRAM 和我們的混合電池存儲器。雖然我們的混合電池存儲器的靜態能耗高于 2T eDRAM,但其性能卻優于 SRAM。在 SRAM/eDRAM 比例為 1/7 的情況下,混合單元存儲器中 SRAM 的固定能源開銷占總能耗的 76.5%。更多詳情可參見圖 14。

至于刷新功耗,SRAM 不需要刷新操作,而 2T eDRAM 和我們的混合單元存儲器則需要。如第 IV-B 節所述,調整參考電壓 (VREF ) 可以幫助延長刷新周期,減少刷新操作。我們選擇了帶有電流模式檢測放大器的傳統 2T eDRAM,并對混合單元存儲器中電壓模式檢測放大器的 VREF 值[0.5、0.6、0.7、0.8]進行了實驗。圖 15.(a) 表明,適當的 VREF 值可顯著降低刷新能量。因此,我們選擇的 0.8 VREF 值產生了最低的刷新操作,因為它將刷新周期延長了近 10 倍,從 1.3us 延長到 12.57us。

關于總能耗(包括整個推理過程中的靜態和動態能耗),eDRAM 占地面積小,但由于其刷新能耗要求,在總體能耗方面并不突出。相反,我們的混合單元存儲器在面積占用最小化和能耗降低方面都具有優勢,能效比 6T SRAM 高出 3.4 倍,如圖 15...(b)所示。不過,RRAM 的能效比 SRAM 低 100 多倍,這是因為它需要進行大量寫入操作。

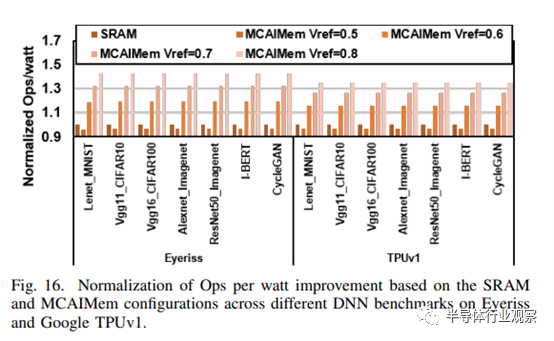

鑒于片上緩沖區在 Eyeriss 和 TPUv1中分別占 42.5% 和 37% 的功耗,使用 VREF =0.8 的 MCAIMem 配置可使每瓦性能提高 35.4% 到 43.2% 的峰值,超過采用 SRAM 的片上緩沖區的效率,如圖 16 所示。因此,MCAIMem 是一種引人注目的解決方案,有可能為高效人工智能存儲器設計的創新鋪平道路。

相關工作

深度神經網絡(DNN)需要大量內存才能實現卓越性能,這導致內存需求增加。解決對片上數據緩沖區和數據移動的更高要求對于提高 DNN 加速器性能至關重要。Chen 等人的研究表明,與 ALU 相比,片外 DRAM 訪問的能耗高出 200 倍,訪問時間也更長。因此,優化片上緩沖區已成為提高 DNN 加速器吞吐量的首要挑戰。問題的關鍵在于如何最大限度地提高片上存儲器容量,同時最小化片外訪問,以提高 DNN 加速器的能效。

DaDianNao 建議在傳統 DNN 加速器中用全 eDRAM(1T1C)取代 SRAM,以顯著提高片上緩沖區容量。然而,這種方法需要定期刷新以維護 DNN 數據,從而導致大量能耗--占 DNN 加速器總能耗的 38.3%。RANA 是一種較新的技術,它利用了與 eDRAM 保留時間相比較短的激活數據壽命,從而消除了不必要的刷新操作。隨著 DNN 應用的發展,這一觀點可能會變得不那么適用,從而導致激活數據增加,并有可能違反激活數據生命周期約束。

為了提高吞吐量,有人提出了內存計算(CIM)來替代傳統的 DNN 加速器。目前已開發出采用兩個 2T eDRAM 的 4T Dual eDRAM 陣列和采用混合 SRAM 和 eDRAM 配置作為計算節點的 DualPIM [21]等技術。此外,最近的 eDRAM 節點優化側重于減少泄漏和增強 CIM 的魯棒性。雖然這些方法顯示出顯著的性能和節能效果,但對片上緩沖器的需求依然存在。

此外,一項名為 ZEM的研究探討了 DNN 數據的異或度量特性,以延長 DNN 數據在片外 DRAM 中的保留時間,從而顯著降低片外 DRAM 的功耗。然而,這項工作的主要目的是降低 DNN 應用程序處理過程中的片外 DRAM 功耗,而不是解決通過最小化片外 DRAM 訪問來提高 DNN 加速器性能這一核心挑戰。在本文中,我們提出了一種針對片上緩沖器的設計,通過創建混合 SRAM 和 eDRAM 單元設計,最大限度地減少片上緩沖器的面積和能耗。這種方法有望用于下一代 DNN 加速器的片上緩沖器設計。

結論

本文介紹了 MCAIMem,這是一種創新的面積和能效 AI 存儲器設計,它采用混合 CMOS 存儲器單元設計,包括 SRAM 和 eDRAM 單元。我們優化了 SRAM/eDRAM 單元的比例,以減少面積,并利用 DNN 的數據表示和非對稱 eDRAM 單元降低能耗。實驗結果表明,與傳統的 SRAM 設計相比,我們的 MCAIMem 設計可將面積減少 48%,能耗降低 3.4 倍,而且不會犧牲精度。這項工作凸顯了混合 CMOS 存儲單元和非對稱 2T eDRAM 單元在實現人工智能存儲器設計的性能、面積和能耗優化平衡方面的潛力。總之,我們的混合 CMOS 單元存儲器設計 MCAIMem 提供了一種前景廣闊的解決方案,有望成為高效人工智能存儲器設計的新標準。

致謝本文作者:Duy-Thanh Nguyen, Abhiroop Bhattacharjee, Abhishek Moitra, Priyadarshini Panda

原文鏈接

https://arxiv.org/abs/2312.03559

審核編輯:劉清

-

編碼器

+關注

關注

45文章

3601瀏覽量

134201 -

存儲器

+關注

關注

38文章

7455瀏覽量

163623 -

緩沖器

+關注

關注

6文章

1920瀏覽量

45450 -

sram

+關注

關注

6文章

764瀏覽量

114638 -

人工智能芯片

+關注

關注

1文章

119瀏覽量

29070

原文標題:替代昂貴的SRAM

文章出處:【微信號:光刻人的世界,微信公眾號:光刻人的世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種創新的面積和能效AI存儲器設計—MCAIMem

一種創新的面積和能效AI存儲器設計—MCAIMem

評論