本案例描述了一個由于CPU和PHY之間RGMII時序不滿要求導致通信異常問題,最后通過電感材料(磁珠)對信號相位的移位特性來改變信號延時,從而解決RGMII信號延時不夠的案例,實驗結果通過。

一、問題描述

某單板上某物理層芯片和CPU之間的接口,采用的是RGMII方式。在該單板調試過程中,發現物理層芯片發送給CPU的方向,數據一直不通。測量芯片輸出的RGMII信號發現,芯片已經有發出時鐘和數據信號,但是CPU接收端無法識別,在CPU的RGMII接收寄存器中,接收到的數據個數一個為0。

經實測信號分析,由于時序不滿足要求,沒法達到接收端建立時間要求導致該問題。如下對該問題進行分析和解決。

二、問題分析

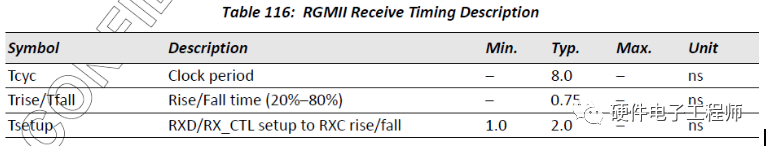

在CPU接收端,RGMII的接收時序如下:

圖1. RGMII接收端時序要求

從上面的時序要求看,在接收端,要求RGMII的時鐘信號邊沿比數據信號的邊沿延遲最小1ns,典型的延遲時間是2ns。延遲2ns的時候,RGMII的時鐘邊沿正好在數據的中間。

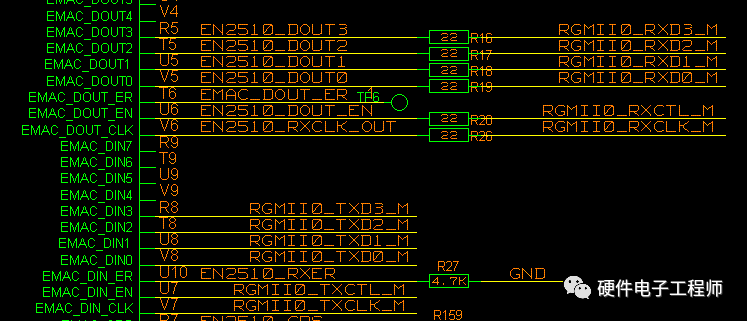

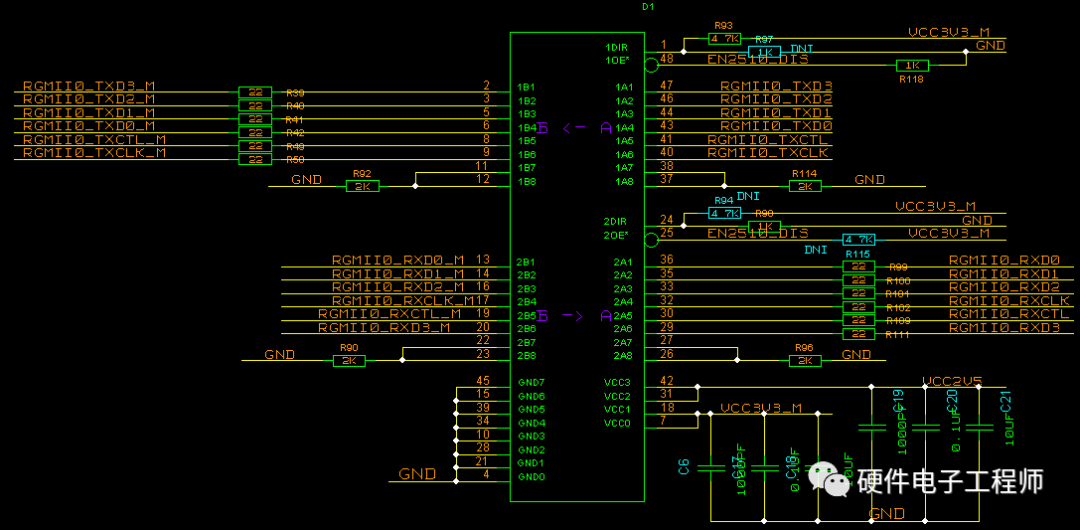

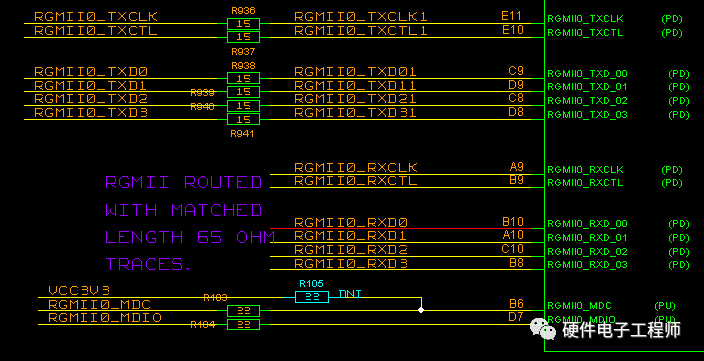

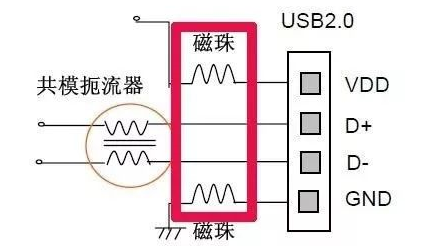

還硬件方案中CPU端RGMII工作電壓為2.5V,在物理層RGMII工作電壓是3.3V。CPU和物理層芯片之間,通過轉換芯片74AVC164245進行電平轉換。具體的連接圖如下:

圖2. 物理層端的RGMII原理圖

圖3. RGMII接口中的電平轉換原理圖

圖4. CPU端的RGMIII原理圖

在CPU接收端,測量接收到的RGMII時鐘和數據,邊沿是對齊的,建立時間不夠不符合時序要求1ns的延時。在CPU的RGMII控制寄存器中,對時鐘延遲時間進行設置,但依然不能達到要求。經與CPU廠家溝通以及實測,這個RGMII控制寄存器能調整的接收時鐘延遲,最大只能到600ps。在發送端芯片內,無法對RGMII的發送時鐘進行延時設置。

三、問題解決

為了驗證該問題,首先做如下驗證分析:

(1)為解決這個問題,考慮到增加走線長度,按照信號在PCB上的傳輸特性,1ns的延時,PCB內層走線的話,要繞5600mil,明顯不現實。

(2)電平轉換芯片74AVC164245手冊中輸入輸出信號的延時,在1ns到4ns之間。正好在單板上,74AVC164245芯片有空余的PIN還沒有使用,通過飛線的方式,把RGMII的時鐘,在轉換芯片上,多繞了一次,測試發現,數據可以通了。通過示波器測量信號,發現此時時鐘比數據,延遲了大概1.5ns,滿足接收端的RGMII時序要求。用這個飛線的方式,做大流量跑流測試,丟包嚴重,性能不穩定。

通過以上驗證分析,在不改板前提下兩種方式都無法解決該問題。經分析和頭腦風暴,考慮到電感對信號的延時的特性,嘗試使用感性材料來實現時鐘的延遲。從理論上看,串聯在鏈路中的電感,可以使交流信號相位延遲90度,這里的RGMII信號,時鐘是125MHz,延遲90度,正好就是2ns,符合RGMII的接收時序要求。

把物理層芯片的RGMII輸出端的匹配電阻R26,換為100MHz@220歐的磁珠,測試發現數據可以正常通訊,在大流量,長時間的拷機過程中,未出現丟包的情況。測量磁珠前后的時鐘波形,發現時鐘結果磁珠后,延時大概1.6ns。更換100MHz@600歐姆的磁珠,時鐘延時2ns,但磁珠交流阻值越大,對信號的衰減也越大。考慮到時鐘衰減和和延遲的結合,使用100MHz@180歐的磁珠,測試發現時鐘信號幅度滿足要求,延時1.5ns,能滿足要求。經過大流量測試,無丟包情況,通過實驗。

四、問題總結

本案例利用一個“野路子”解決硬件調試中常見的問題,該解決思路拓寬了我們思維邊界;同時也告訴我們當遇到問題時,堅持第一性原則,追本溯源到最底層最原始的物理原理去,定能柳暗花明又一村。

來源: 本文轉載自硬件電子工程師公眾號

審核編輯:湯梓紅

-

芯片

+關注

關注

453文章

50406瀏覽量

421829 -

寄存器

+關注

關注

31文章

5317瀏覽量

120008 -

cpu

+關注

關注

68文章

10825瀏覽量

211150 -

磁珠

+關注

關注

6文章

266瀏覽量

44138 -

RGMII

+關注

關注

0文章

27瀏覽量

12153

原文標題:硬件調試:一個“野路子”解決RGMII延時不夠問題

文章出處:【微信號:電子設計聯盟,微信公眾號:電子設計聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通過磁珠解決RGMII延時不夠案例

通過磁珠解決RGMII延時不夠案例

評論