最近,Imec 公布的超大規模自旋軌道轉移 MRAM (SOT-MRAM) 器件已實現創紀錄的性能,每比特開關能量低于 100 飛焦耳,耐用性超過 10 的 15 次方。

這些結果使得 SOT-MRAM 成為替代 SRAM 作為高性能計算 (HPC) 應用中最后一級緩存的有希望的候選者。就像 SRAM 一樣,它提供高開關速度(在亞納秒范圍內)和無限的耐用性。

此外,由于是非易失性,SOT-MRAM 位單元在高單元密度下可實現比 SRAM 更低的待機功耗。此外,SOT-MRAM 位單元可以做得比 SRAM 單元小得多,從而轉化為更高的位封裝密度。

Imec 通過實驗探索了在 300mm 晶圓上加工的單垂直 SOT-MRAM 器件的擴展潛力和局限性,這是有史以來第一個關于 SOT-MRAM 器件擴展性的研究報告。在 IEDM 2023 上,他們表明,縮小 SOT 軌道不僅減少了 SOT-MRAM 單元的占地面積,而且還大大提高了單元的性能和可靠性。

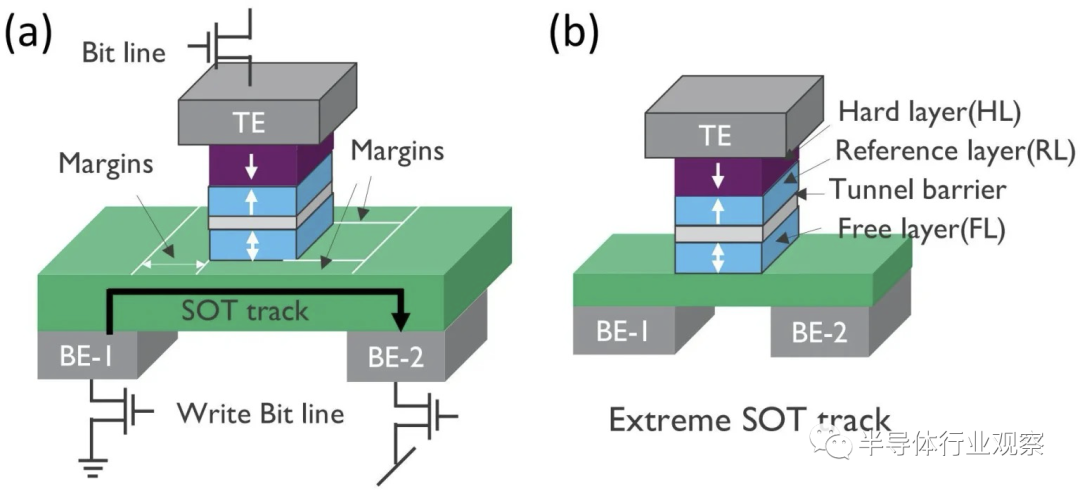

SOT 軌道是由鎢 (W) 或鉑 (Pt) 等金屬制成的層,位于磁性隧道結 (MTJ)(SOT-MRAM 器件的實際開關元件)下方。SOT 軌道用作面內電流注入層,引入它是為了解耦讀取和寫入路徑。

“在傳統的 SOT-MRAM 設計中,SOT 軌道占用的面積大于實際 MTJ 柱的占地面積,為覆蓋過程控制提供足夠的余量,”imec 磁學項目總監 Sebastien Couet 解釋道。“但這會導致能量浪費,因為部分電流會流到 MTJ 區域之外。我們將 SOT-MRAM 器件擴展至極限,SOT 軌道和 MTJ 柱具有相當的尺寸(臨界尺寸約 50 納米)。對于這些器件,我們觀察到每比特的開關能量低于 100 飛焦耳 (fJ),即與傳統設計相比減少了 63%。這有助于解決 SOT-MRAM 的剩余挑戰,傳統上 SOT-MRAM 需要高電流進行寫入操作。”

縮放 SOT 軌道可以提高存儲器的耐用性,因為它可以減少 SOT 層內的焦耳熱。

“憑借超過 1015 個編程/擦除周期的耐用性,我們通過實驗驗證了我們的假設,即 SOT-MRAM 單元可以具有無限的耐用性——這是緩存存儲器的重要要求,”Couet 說。

“我們的數據為電路設計人員提供了寶貴的輸入,以便在先進節點上執行 SOT-MRAM 技術的設計技術協同優化 (DTCO)——性能改進和設計裕度之間的權衡。未來的工作重點是材料工程,以進一步降低每位的開關能量,并優化位單元配置,以進一步縮小與 SRAM 相比的單元面積。從長遠來看,這些經驗也將轉移到電壓門控 (VG) SOT-MRAM 多柱器件的開發中——imec 針對高密度嵌入式存儲器應用的終極解決方案。”Sebastien Couet 補充道。

我們將見證SRAM的死亡?

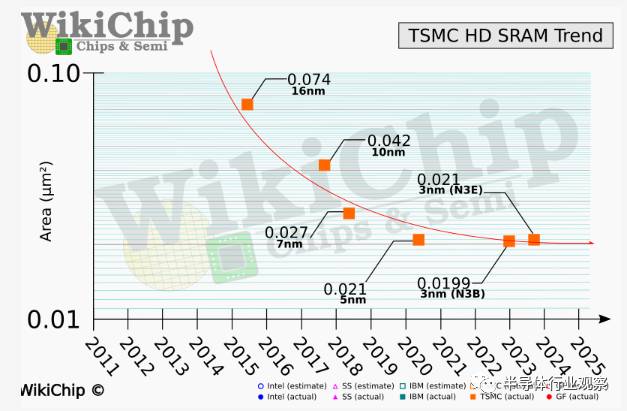

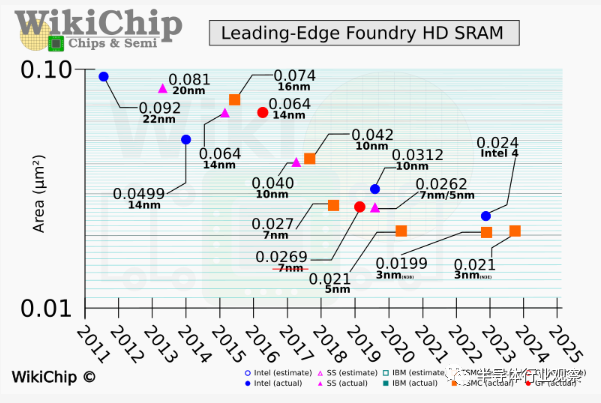

今年,第 68 屆年度 IEEE 國際電子器件會議 (IEDM) 全面恢復,來自世界各地的近 1,500 名工程師(親臨現場)每年都會返回舊金山市中心,討論半導體行業的最新發展。雖然學術界和工業界都有大量有趣的論文,但臺積電的那篇論文帶來了可怕的壞消息——雖然邏輯仍在或多或少地沿著歷史趨勢線擴展,但 SRAM 擴展似乎已經完全崩潰。

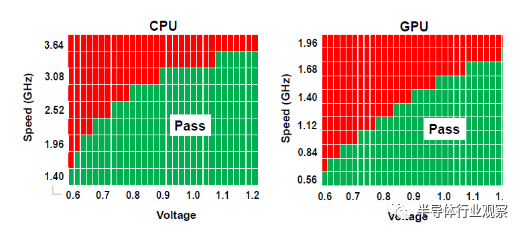

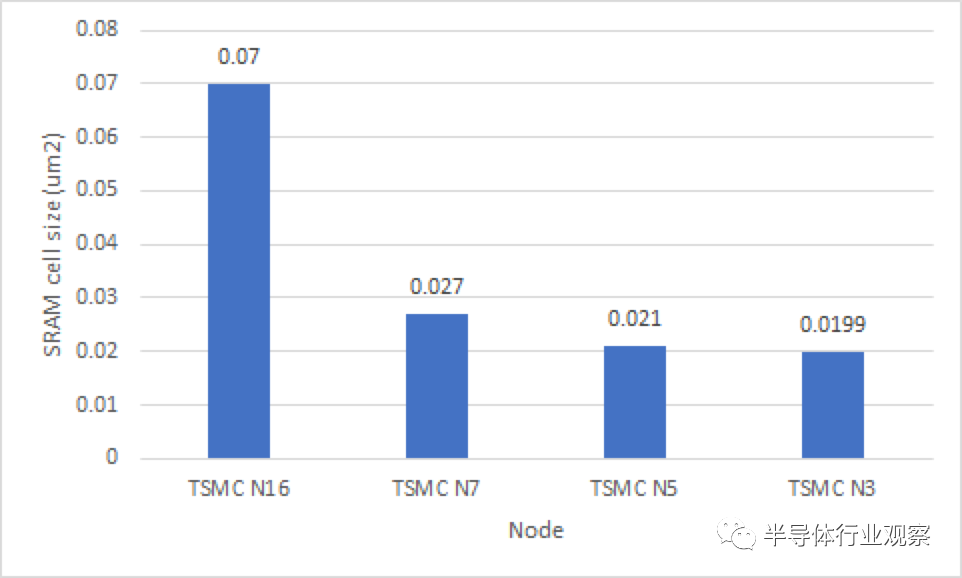

在會議上,臺積電談到了原始基礎 N3 (N3B) 節點以及增強型 (N3E),后者是N3B 稍微寬松一些的變體。臺積電展示原型測試芯片配備了一個由超過 35 億個晶體管和一個可完全運行的 256Mbit SRAM 宏組成的邏輯電路(圖 1)。SRAM 存儲單元面積為 0.0199μm 2,是有史以來最小的。我們確認 SRAM 宏即使在 0.5V 的電壓下也能完美工作(圖 2)。

有趣的是,對于新的 N3E 節點,高密度 SRAM 位單元尺寸達到 0.021 μm2,這與他們的 N5 節點的位單元大小完全相同,并沒有縮小。N3B 變體預計不會進入太多產品,但確實具有縮放 SRAM 位單元;然而,在 0.0199μm2 時,它僅縮小了 5%(或縮小了 0.95 倍)。

就粗略的內存密度而言(假設 ISO 輔助電路開銷),N3E 大致為 31.8 Mib/mm2,并將增加到 33.55 Mib/mm2 或 1.75 Mib/mm2(230 KB)的改進。

這是一些嚴重的壞消息!從這個角度來看,雖然據說 N3B 和 N3E 都提供了 1.6 倍和 1.7 倍的芯片級晶體管縮放,但 SRAM 的 1.0 倍和 1.05 倍縮放是災難性的。現在,我們仍然希望臺積電在某個時候為 N3 推出更密集的 SRAM 位單元變體,我們確實希望在未來看到 SRAM 的某種程度的微縮,但好的舊微縮 SRAM 微縮似乎已經死了。

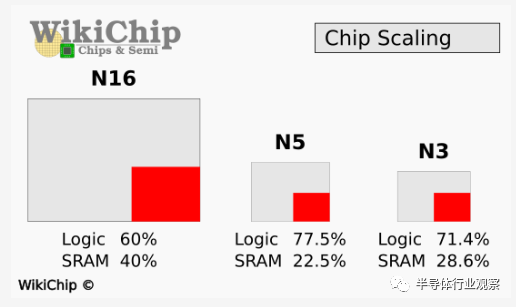

考慮一個假設的 100 億晶體管芯片,其中包含 40% 的 SRAM 和 60% 的邏輯,位于 TSMC N16 上。忽略實際限制和模擬/物理/等,這樣一個假設的芯片將約為 255 平方毫米,其中 45 平方毫米或 17.6% 用于 SRAM。將完全相同的芯片縮小到 N5 將產生一個 56 平方毫米的芯片,其中 12.58 平方毫米或占芯片的 22.5% 用于 SRAM。將芯片進一步縮小到 N3(基于我們最初但未完全確認的值)將產生一個 44 平方毫米的芯片,其 SRAM 密度相同為 12.58 平方毫米,現在占面積的近 30%。

當然,這種影響不會在所有方面都感受到同樣的影響。芯片上 SRAM 和緩存的百分比因目標市場和整體能力而異。然而,對于一些 AI 硬件初創公司來說,架構要求芯片的很大一部分被 SRAM 覆蓋,這些工程師將比其他人更快地遇到更多挑戰。

SRAM 微縮的崩潰并不僅限于臺積電。我們已經指出 SRAM 縮放速度變慢的問題已經有一段時間了。例如,雖然英特爾仍在縮減其 SRAM 位單元,但該公司最近宣布的Intel 4 進程SRAM 縮放比例已從歷史上的 0.5-0.6 倍放緩至 0.7-0.8 倍。對于 Intel 4,我們的估計密度(ISO 輔助電路開銷與 TSMC 相比)為 27.8 Mib/mm2 或 4 Mib/mm2 或落后 13%。期望 Intel 的 Intel 3 工藝能夠匹敵或擊敗它們并非不切實際。

那么,我們該何去何從?事實上,目前唯一可行的 SRAM 替代品就是更多的 SRAM,因此我們預計 SRAM 會直接占用更多的面積。這并不是說我們不期望更多的 SRAM 擴展。雖然我們確實希望臺積電和其他代工廠生產更密集的 SRAM,但歷史上的擴展似乎已經正式結束。Imec 等一些研究機構提出了更高密度的 SRAM 位單元。例如,在去年的 IEDM 2021 上,Imec 在一個假設的“超越 2 納米節點”上展示了大約 60 Mib/mm2 的 SRAM 密度,大約是今天密度的兩倍,該節點使用utilizing forksheet晶體管和先進的雙面互連方案。

除了 SRAM,業界一直在研究許多其他替代內存架構。新興的內存技術包括 MRAM、FeRAM、NRAM、RRAM、STT-RAM、PCM 等。與 SRAM 相比,這些新興的內存位單元提供了獨特的權衡,例如在較低的讀/寫規范下具有更高的密度、非易失性能力、較低的讀寫周期能力,或者在可能較低的密度或速度下具有較低的功耗。雖然它們不是 SRAM 的直接替代品,但向前發展它們可能會扮演 4 級或 5 級緩存的角色,其中較低的性能權衡可以通過更高的密度來抵消。

目前,該行業似乎已經到了一個有趣的拐點。

審核編輯:劉清

-

HPC

+關注

關注

0文章

311瀏覽量

23682 -

嵌入式存儲器

+關注

關注

0文章

24瀏覽量

12405 -

MRAM

+關注

關注

1文章

236瀏覽量

31698 -

SRAM芯片

+關注

關注

0文章

65瀏覽量

12048

原文標題:創紀錄的SOT-MRAM,有望替代芯片中的SRAM

文章出處:【微信號:致真精密儀器,微信公眾號:致真精密儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

小米雙十一銷售額創紀錄 全渠道累計支付319億

創紀錄!光電封裝大廠業績強勁,≥800G產品同比增收近20%

看點:英偉達市值創紀錄 臺積電明年3nm訂單激增 工信部大力發展新領域新賽道

imec實現硅基量子點創紀錄低電荷噪聲

探索存內計算—基于 SRAM 的存內計算與基于 MRAM 的存算一體的探究

誰將接任蘋果公司CEO?分析認為特努斯有望成為繼任者

Microchip推出容量更大、速度更快的串行SRAM產品線

Microchip推出容量更大、速度更快的串行 SRAM產品線

臺積電開發出SOT-MRAM陣列芯片,功耗極低

臺積電開發出SOT-MRAM陣列芯片

殺手锏!臺積電開發SOT-MRAM陣列芯片

臺積電和ITRI成功研發SOT-MRAM,功耗僅為STT-MRAM的百分之一

sram讀寫電路設計

耦合強粘接和抗凍特性的凝膠電解質用于耐低溫水系混合電容器

創紀錄的SOT-MRAM有望成為替代SRAM的候選者

創紀錄的SOT-MRAM有望成為替代SRAM的候選者

評論